Лекции / Схемотехника ЭВМ. Лекция 07. Счётчики. Синхронные и асинхронные

.pdf3.5.Синхронные счётчики

Ксинхронным относят счётчики с параллельным переносом, построенные на счётных триггерах, и счётчики, построенные на синхронных триггерах, все тактовые (синхронизирующие) входы которых объединены в единую цепь, на которую подают счётные импульсы. Синтез таких счётчиков состоит из следующих процедур.

1. Учитывая динамику и эффективный (активный) перепад на тактовом входе, выбирают тип триггера и серию элементов.

2. Определяют количество триггеров счётчика.

3. Составляют таблицу переходов счётчика, исходя из заданного порядка изменения его состояний.

4. Составляют характеристическую таблицу для выбранного типа триггера.

5. Минимизируют функции возбуждения для всех триггеров счётчика. Полученные уравнения полностью определяют структуру синтезируемого счётчика.

6. Проверяют, является ли схема самовосстанавливающей, если

2n−1 +1 ≤ M < 2n , так как могут возникнуть устойчивые паразитные циклы из состояний, не входящих в рабочий цикл.

7. Оформляют окончательную принципиальную схему счётчика. Все примеры, приведённые ниже, рассматриваются без учёта па-

раметров быстродействия.

Пример 3.1. Синтезировать суммирующий синхронный счётчик с модулем счёта M = 12 с естественным порядком изменения состояний, начиная с нулевого, на универсальных D-триггерах. Порядок выполнения следующий.

1.Тип триггера задан в условии задачи.

2.Определяем количество триггеров n = ]log2 12[ = 4.

3.Составляем таблицу переходов (табл.3.2).

Таблица 3.2

Таблица переходов счётчика с M = 12

|

|

t |

|

|

|

t+1 |

|

|

|

|

|

|

|

Q3 Q2 Q1 Q0 |

|||

|

Q3 Q2 Q1 Q0 D3 D2 D1 D0 |

|||||||

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

2 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

3 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

4 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

5 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

6 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

7 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

8 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

9 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

10 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

11 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

4. Составляем характеристическую таблицу для универсального D-триггера (табл.3.3).

Учитывая, что для D-триггера Di =Qit +1 , в табл.3.2 используются

столбцы Qit +1 как значения Dit .

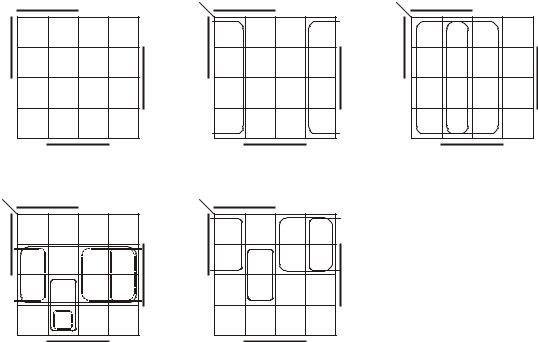

5. Используя карты Карно (рис.3.9), минимизируем функции возбуждения Di для четырёх разрядов счётчика. Из рис.3.9 следует

|

|

|

|

|

|

D0 = |

|

, |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

Q0 |

|

||||||||||

|

Таблица 3.3 |

D1 =Q1 Q0 , |

|

|

|||||||||||||

|

|

(3.10) |

|||||||||||||||

Характеристиче- |

|

|

|

|

|

|

|

|

|

|

|||||||

D2 =Q2 Q3Q1Q0 , |

|||||||||||||||||

|

|

||||||||||||||||

ская таблица D- |

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

триггера |

Di |

|

D3 =Q3 |

Q0 |

+Q3 |

Q1 |

+Q2Q1Q0. |

|

||||||||

|

Qti Qit+1 |

|

6. Уравнения (3.10) |

определяют |

струк- |

||||||||||||

|

0 0 |

|

|

0 |

|

туру синтезируемого счётчика. Прежде чем |

|||||||||||

|

0 1 |

|

|

1 |

|

оформлять схему счётчика, проверим, будет |

|||||||||||

|

|

|

|

ли он самовосстанавливающимся. |

|

||||||||||||

|

1 0 |

|

|

0 |

|

|

|||||||||||

|

|

|

|

В рабочем цикле отсутствуют состояния |

|||||||||||||

|

1 1 |

|

|

1 |

|

||||||||||||

|

|

|

|

12, 13, 14 и 15. Счётчик может установиться в |

|||||||||||||

|

С= |

|

|

|

|

одно из этих состояний при первичном вклю- |

|||||||||||

|

|

|

|

|

|||||||||||||

|

|

|

|||||||||||||||

чении питания либо в результате сбоя от действия помех. Из карт Карно следует, что если счётчик установится в состояние 12, то дальнейшая работа осуществляется в цикле 12→13→14→15→12…, который является устойчивым. Таким образом, можно сделать вывод, что уравнения (3.10) соответствуют не самовосстанавливающемуся счётчику, следовательно, нужно обеспечить вхождение в рабочий цикл из любого нерабочего состояния. Так как D0 - D3 являются не полностью определёнными функциями, вхождениеврабочий циклможнообеспечитьразличнымобразом.

Откажемся от связки в выражении для D2 в формуле (3.10) и запишем D2 в дизъюнктивной нормальной форме (см. штриховые контуры

на рис.3.9,г): D2′ =Q2 Q1 +Q2 Q0 +Q3 Q2 Q1 Q0 .

Теперь из карт Карно видно, что счётчик будет менять состояния следующим образом:

0→1→2→3→4→5→6→7→8→9→10→11→0… 12→13→14→15→8…,

т.е. будет самовосстанавливающимся.

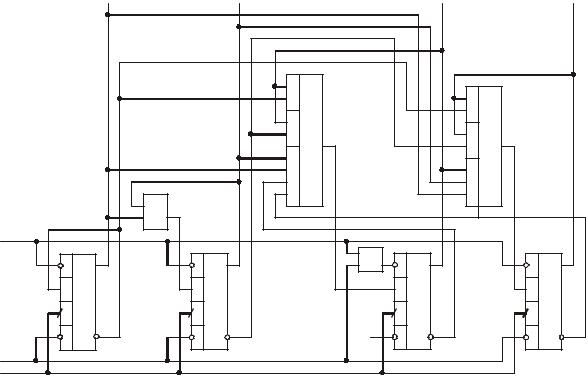

7. Схема счётчика приведена на рис.3.10. Формирование цепей «Уст. "0"» и «Уст. "11"» проанализируйте самостоятельно.

|

Q1 |

|

|

D0 |

Q1 |

|

D1 |

|

Q1 |

|

|

10 |

11 |

9 |

8 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

Q3 |

|

|

|

Q3 |

|

|

Q3 |

|

|

|

|

14 |

15 |

13 |

12 |

- |

- |

- |

- |

- |

- |

- |

- |

|

|

|

Q2 |

|

|

|

Q2 |

|

|

|

Q2 |

6 |

7 |

5 |

4 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

2 |

3 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

|

|

Q0 |

|

|

|

Q0 |

|

|

|

Q0 |

|

|

|

а |

|

|

|

б |

|

|

в |

|

|

D2 |

Q1 |

|

|

D3 |

Q1 |

|

|

|

|

|

|

0 |

0 |

0 |

0 |

1 |

0 |

1 |

1 |

|

|

|

|

Q3 |

|

|

|

Q3 |

|

|

|

|

|

|

|

- |

- |

- |

- |

- |

- |

- |

- |

|

|

|

|

|

|

|

Q2 |

|

|

|

Q2 |

|

|

|

|

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

|

|

|

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

Q0 |

|

|

д |

Q0 |

|

|

|

|

|

|

|

г |

|

|

|

|

|

|

|

|

Рис.3.9. Карты Карно: а - эталонная; б - для D0; в - для D1; г - для D2; д - для D3

|

Q0 |

Q1 |

|

Q2 |

Q3 |

|

|

& |

1 |

|

& 1 |

|

|

|

|

|

|

|

|

& |

|

|

& |

|

|

|

|

|

|

|

|

& |

|

|

& |

|

|

|

|

|

|

|

|

=1 |

|

|

|

Уст. «0» |

|

|

|

|

|

|

R TT |

R TT |

& |

R TT |

R TT |

|

|

||||

|

D |

D |

|

D |

D |

|

C |

C |

«1» |

C |

C |

|

S |

S |

S |

S |

|

Уст. «11» |

|

||||

|

|

|

|

|

|

ТИ |

|

|

|

|

|

|

Рис.3.10. Схема синхронного суммирующего счётчика с М = 12 |

|

|||

Пример 3.2. Синтезировать реверсивный синхронный трёхразрядный счётчик на JK-триггерах. Порядок выполнения следующий.

Количество и тип триггера (этап 1 и 2) заданы в условии задачи. Введём сигнал-модификатор m для указания направления счёта и

примем, что при m = 0 счётчик будет суммирующим, а при m = 1 - вычитающим.

3. Составляем таблицу переходов (табл.3.4).

Таблица 3.4

Таблица переходов 3-разрядного реверсивного счётчика

|

|

Номер |

m |

Q2 |

Q1 |

Q0 Q2 |

Q1 |

Q0 |

|

J2 |

K2 |

J1 |

|

K1 |

J0 |

K0 |

|

|

|

|

набора |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

0 |

|

0 |

|

|

1 |

|

|

|

|

|

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

|

0 |

|

1 |

|

|

|

1 |

|

|

|

2 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

|

0 |

|

|

|

0 |

1 |

|

|

|

|

3 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

|

1 |

|

|

|

1 |

|

1 |

|

|

|

4 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

|

|

0 |

0 |

|

|

1 |

|

|

|

|

5 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

|

|

0 |

1 |

|

|

|

1 |

|

|

|

6 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

|

|

0 |

|

|

0 |

1 |

|

|

|

|

7 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

|

|

1 |

|

|

1 |

|

1 |

|

|

|

8 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

|

1 |

|

1 |

|

|

1 |

|

|

|

|

9 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

|

0 |

|

0 |

|

|

|

1 |

|

|

|

10 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

|

0 |

|

|

|

1 |

1 |

|

|

|

11 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

|

0 |

|

|

|

0 |

|

1 |

|

|

|

12 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

|

|

1 |

1 |

|

|

1 |

|

|

|

|

13 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

|

|

0 |

0 |

|

|

|

1 |

|

|

|

14 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

|

|

0 |

|

|

1 |

1 |

|

|

|

|

15 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

|

|

0 |

|

|

0 |

|

1 |

|

|

|

|

|

|

t |

|

|

|

|

|

|

t+1 |

|

|

|

|

|

|

|

4. Составляем |

характеристическую |

таблицу |

для |

JK-триггера |

||||||||||||||

(табл.3.5).

Таблица 3.5

Характеристическая таблица JK-триггера

Qti Qit+1 |

|

Ji |

Ki |

|

|

|

|

|

|

0 0 |

|

0 |

|

|

0 1 |

|

1 |

|

|

1 0 |

|

|

|

1 |

1 1 |

|

|

|

0 |

С= |

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

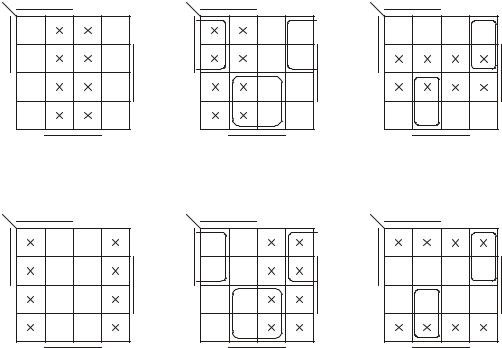

5. Используя характеристическую таблицу для JK-триггера, заполняем шесть правых столбцов табл.3.4. Из карт Карно (рис.3.11) следует

J0 = K0 =1; |

|

|||||

|

|

|

|

|

|

|

J1 = K1 = mQ0 +mQ0 ; |

||||||

|

||||||

J2 = K2 = mQ1Q0 +mQ1Q0.

6.Так как для проектируемого счётчика M = 23 = 8, он является самовосстанавливающимся.

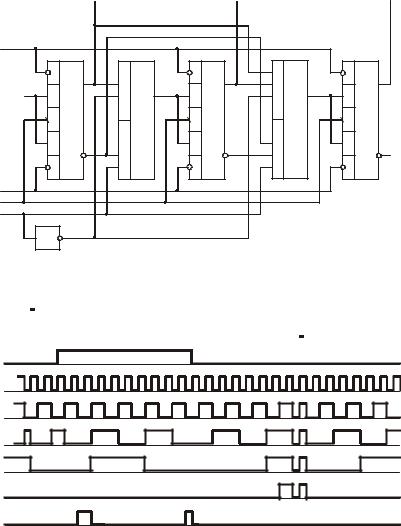

7.Принципиальная схема счётчика приведена на рис.3.12, а временные диаграммы, поясняющие его работу, на рис.3.13.

На временных диаграммах показаны сигналы переноса P2 и заёма Z2 . Самостоятельно запишите уравнения для P2 и Z2 и дополните соответствующими элементами схему на рис.3.12. Как использовать сигналы P2 и Z2 дляпостроениясинхронногореверсивногочетырёхразрядного счётчика?

Схема с раздельными тактовым входом ТИ и управляющим входом m не является единственным вариантом построения синхронного реверсивного счётчика. Если использовать JK-триггер в счётном режиме (J = K = 1), то учитывая (3.2) - (3.8) и (3.9), можно записать, введя обозначение Ci для тактового входа i-го JK-триггера:

C0 = |

|

ТИ +mТИ; |

|

|

|||||||||||||||||

m |

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C1 =Q0 mТИ +Q0mТИ; |

|

(3.11) |

|||||||||||||||||||

C2 =Q1Q0 |

|

ТИ + |

|

1 |

|

0mТИ; |

|

||||||||||||||

m |

Q |

Q |

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C3 =Q2Q1Q0 mТИ +Q2 Q1Q0mТИ. |

|

||||||||||||||||||||

J0 |

Q1 |

|

J1 |

Q1 |

|

J2 |

Q1 |

|

|

|

1 |

1 |

|

0 |

1 |

0 |

0 |

0 |

1 |

m |

|

|

m |

|

|

m |

|

|

|

|

1 |

1 |

|

0 |

1 |

|

|

|

|

|

|

Q2 |

|

|

Q2 |

|

|

|

Q2 |

|

1 |

1 |

|

1 |

0 |

|

|

|

|

|

1 |

1 |

|

1 |

0 |

0 |

1 |

0 |

0 |

|

|

Q0 |

|

Q0 |

|

|

Q0 |

|

|

|

|

а |

|

б |

|

|

в |

|

|

|

|

|

|

|

|

|

|

||

K0 |

Q1 |

|

K1 |

Q1 |

|

K2 |

Q1 |

|

|

|

1 |

1 |

1 |

0 |

|

|

|

|

|

m |

|

|

m |

|

|

m |

|

|

|

|

1 |

1 |

1 |

0 |

|

0 |

0 |

0 |

1 |

|

|

Q2 |

|

|

Q2 |

|

|

|

Q2 |

|

1 |

1 |

0 |

1 |

|

0 |

1 |

0 |

0 |

|

1 |

1 |

0 |

1 |

|

|

|

|

|

|

|

Q0 |

|

Q0 |

|

|

Q0 |

|

|

|

|

г |

|

д |

|

|

е |

|

|

|

Рис.3.11. Карты Карно: а, б, в, г, д, е - соответственно для J0, K0, J1, K1, J2, K2 |

|

|

||||||

Q0 |

Q1 |

Q2 |

R |

|

|

|

|

|

|

|

|

|

|

|

R |

TT |

& |

1 |

R |

TT |

& |

1 |

R |

TT |

«1» |

J |

|

|

|

J |

|

|

|

J |

|

|

|

|

|

|

|

|

|

|||

|

C |

|

|

|

C |

|

& |

|

C |

|

|

K |

|

& |

|

K |

|

|

K |

|

|

|

|

|

|

|

|

|

|

|||

|

S |

|

|

|

S |

|

|

|

S |

|

S |

|

|

|

|

|

|

|

|

|

|

ТИ |

|

|

|

|

|

|

|

|

|

|

m |

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

Рис.3.12. Схема синхронного реверсивного счётчика (n = 3)

R |

|

|

|

|

|

t |

|

|

|

|

|

||

S |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

m

ТИ

Q0

Q1

Q2

P2

Z2

Рис.3.13. Временные диаграммы для схемы счётчика, представленного на рис.3.12

Обозначив mТИ через «+1», а mТИ - через «–1», можно видеть, что счётчик будет суммирующим при подаче на вход «+1» счётных импульсов, а на вход «–1» уровня логического нуля «0» и вычитающим при подаче на вход «–1» счётных импульсов, а на вход «+1» уровня логического нуля «0». Активными перепадами на входах «+1» и «–1» в данном случае являются отрицательные перепады 1/0. «+1» = «–1» = 0 - режим хранения.

Используя вышесказанное, рассмотрим в качестве примера синтез промышленного образца универсального счётчика типа K155ИЕ7, К55ИЕ7 и т.п.

Пример 3.3. Синтезировать реверсивный синхронный четырёхразрядный счётчик на JK-триггерах с возможностью наращивания разрядности, параллельной загрузки данных и установки счётчика в нулевое состояние. Наращивание разрядности обеспечить использованием двух счётных входов («+1» и «–1») с активным перепадом 01 и раздельными цепями переноса (≥15) и заёма (≤0), обеспечивающими соответственно активные перепады 01 после окончания состояний 15 и 0. Параллельную загрузку данных осуществлять уровнем «0» асинхронного сигнала V, а установку в нуль - уровнем «1» асинхронного сигнала R. При наличии двух активных уровней на входах V и R (V = 0; R = 1) счётчик должен устанавливаться в состояние «0», т.е. вход R должен иметь приоритет перед входом V. В используемых JK-триггерах имеются асинхронные входы установки и сброса с активным нулевым потенциалом. Специальное требование: входы «+1»; «–1»; Di; V и R должны быть единичными нагрузками для внешних управляющих элементов (считаем, что схема реализуется в ТТЛили ТТЛШ-схемотехнике).

Учитывая условия задачи и соотношения (3.11), можно записать

C0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

= +1 +− |

1, |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

=Q +1+Q |

|

|

−1, |

|

|

|

|

|

|

|

||||||||||||||||

C |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

1 |

0 |

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(3.12) |

||

|

|

|

|

|

|

|

|

|

|

|

|

−1, |

||||||||||||||

C2 =Q1Q0 +1+Q1Q0 |

|

|

|

|

||||||||||||||||||||||

C |

= Q Q Q |

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

+1+Q |

Q |

Q |

0 |

−1, |

|

|||||||||||||||||||||

3 |

2 |

1 |

0 |

|

|

|

|

2 |

1 |

|

|

|

|

|

|

|||||||||||

откуда следует, что счётчик будет суммирующим при подаче на вход «+1» счётных импульсов, а на вход «–1» уровня логической единицы «1» и вычитающим при подаче на вход «–1» счётных импульсов, а на вход «+1» уровня логической единицы «1». «+1»= «–1» = «1» - режим хранения (блокировка счётных входов).