Лекции / Схемотехника ЭВМ. Лекция 05. Сдвиговые регистры

.pdf

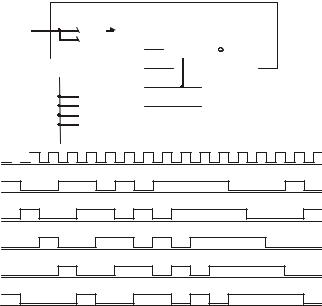

Таблица 2.21

Функционирование регистра в режиме делителя частоты на 15

набораНомер |

Q3 |

Q2 |

Q1 |

Q 0 |

DR |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

1 |

0 |

|

|

|

|

|

|

2 |

0 |

0 |

1 |

0 |

0 |

|

|

|

|

|

|

3 |

0 |

0 |

1 |

1 |

0 |

|

|

|

|

|

|

4 |

0 |

1 |

0 |

0 |

1 |

|

|

|

|

|

|

5 |

0 |

1 |

0 |

1 |

1 |

|

|

|

|

|

|

6 |

0 |

1 |

1 |

0 |

1 |

|

|

|

|

|

|

7 |

0 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

8 |

1 |

0 |

0 |

0 |

1 |

|

|

|

|

|

|

9 |

1 |

0 |

0 |

1 |

1 |

|

|

|

|

|

|

10 |

1 |

0 |

1 |

0 |

1 |

|

|

|

|

|

|

11 |

1 |

0 |

1 |

1 |

1 |

|

|

|

|

|

|

12 |

1 |

1 |

0 |

0 |

0 |

|

|

|

|

|

|

13 |

1 |

1 |

0 |

1 |

0 |

|

|

|

|

|

|

14 |

1 |

1 |

1 |

0 |

0 |

|

|

|

|

|

|

15 |

1 |

1 |

1 |

1 |

0 |

|

|

|

|

|

|

Прежде чем оформлять схему, рассмотрим, как будет вести себя регистр, если он по каким-либо причинам установится в состояние 0, которое отсутствует в рабочем цикле. При написании выражения (2.35)

значение DR на наборе (состоянии) 0 доопределено как «0». Ясно, что схема зациклится в состоянии 0, что равносильно катастрофическому отказу. Следовательно, если регистр попадет в это состояние, то на входе DR нужно выработать значение «1», которое переведет схему в состояние 1, и далее она будет работать в нормальном цикле. Из рис.2.47 следуют три возможных варианта реализации DR = 1 на наборе 0:

DR |

= |

|

|

|

|

|

|

|

|

|

|

|

|

|

= |

|

|

|

|

|

|

|

|

Q |

|

Q |

|

Q |

|

Q |

|

Q |

+Q |

+Q |

+Q |

|

|||||||||||

1 |

3 |

|

2 |

|

1 |

0 |

3 |

2 |

1 |

0 |

|

|

|||||||||||

DR2 = |

|

|

|

|

|

|

|

|

. |

(2.36) |

|||||||||||||

Q2Q1Q0 =Q2 +Q1 +Q0 |

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DR3 =Q3Q1Q0 =Q3 +Q1 +Q0 |

|

||||||||||||||||||||||

|

|

||||||||||||||||||||||

На рис.2.48,а показана схема, в которой сигнал DR реализуется следующим образом:

|

|

|

DR =Q3 Q2 + |

Q2 +Q1 +Q |

0 . |

(2.37) |

||||||||||

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C21 |

RG |

Q0 |

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|||||

|

|

|

|

DR |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

Q1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q2 |

|

|

|

|

|

=1 |

|

|

|

|

|

|

|

|

D0 |

|

|

|

|

|

|||||||

|

|

|

|

|

Q3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

D2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

а |

|

||||||

|

|

|

|

|

|

|

|

|

|

|||||||

С

8 1 2 4 9 3 6 13 10 5 11 7 15 14 12 8 1

DR

Q0

Q1

Q2

Q3

б

Рис.2.48. Делитель частоты на 15: а - схема; б - временные диаграммы

Из рис.2.48,б следует, что ни один из разрядов регистра, ни сигнал DR не могут являться выходом делителя частоты, так как все они выдают четыре импульса в течение рабочего цикла вместо требуемого одного. Выход делителя частоты может быть сформирован одним из следующих способом:

• дешифрированием любого одного рабочего состояния сдвигового регистра, например, если дешифрируется рабочее состояние 11, то

yвых = y11 =Q3Q2Q1Q0 для дешифратора с активной единицей выхода

или yвых = y11 =Q3Q2Q1Q0 для дешифратора с активным нулём выхода;

• дешифрированием любого одного рабочего состояния сдвигового регистра с возможностью понижения ранга произведений для yвых , если воспользоваться наличием нерабочих состояний. В рассматриваемом случае имеется только одно нерабочее состояние 0, поэтому можно сформировать следующие четыре варианта сигнала yвых (для формиро-

вания активной 1 выхода): yвых = y1 =Q3Q2Q1 ; yвых = y2 =Q3Q2Q0 ;

yвых = y4 =Q3Q1Q0 ; yвых = y8 =Q2Q1Q0 . Эти четыре произведения соответствуют двум клеткам карты Карно с наборами 1 и 0; 2 и 0 и т.д.;

•дешифрированием нескольких рабочих состояний, если в рабочем цикле они расположены рядом во времени, в том числе и с учётом нерабочих состояний;

•формированием осведомительного сигнала в зависимости от скважности выходного импульса по отношению к длительности рабочего цикла. Например, если требуется сформировать выходной сигнал, принимающий значение 1 на восьми рядом расположенных во времени состояниях и значение 0 на остальных семи рядом расположенных состояниях, то одним из возможных решений может быть формирование, например, следующего

выходного сигнала, представленного в числовой форме |

СДНФ: y = |

||||||||||||||

= V(1,2,4,9,3,6,13,10; ×: 0). После минимизации (например, с помощью карт |

|||||||||||||||

Карно) получаем yвых = |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Если модуль |

Q3Q2 +Q3Q0 +Q2Q0 +Q3Q2Q1Q0 . |

|||||||||||||||

деления частоты - четное число, то легко сформировать выходной сиг- |

|||||||||||||||

нал со скважностью 2. |

|

||||||||||||||

Для устранения рисков сбоя на выходе логического элемента, формирующего сигнал yвых, рекомендуется подключить конденсатор, емкость которого не должна превышать величину, указанную в технических условиях на используемую серию логических элементов.

Отметим также, что схема, показанная на рис.2.48,а, более известна как генератор цифровой псевдослучайной последовательности длительностью 2n − 1 при n = 4.

2.4.6. Операции, выполняемые сдвиговым регистром

Сдвиговые регистры как многофункциональные узлы ЭВМ могут выполнять различные операции над данными, наиболее важными среди которых являются:

• преобразование параллельного кода в последовательный;

•преобразование последовательного кода в параллельный;

•хранение чисел в ОЗУ с небольшим объемом данных с последовательной выборкой;

•логические и арифметические сдвиги и др.

При преобразовании параллельного кода в последовательный данные загружаются в регистр параллельным кодом. Затем регистр переводится в режим сдвига и данные выдаются в последовательном коде. Выдача данных может осуществляться старшими или младшими разрядами вперед в зависимости от алгоритма их обработки. Типичные примеры использования такого преобразования: построение передатчиков для последовательных интерфейсов; сравнение чисел, представленных последовательными кодами; ввод контролирующих кодов в БИС с ограниченным числом контактных площадок и т.д.

При преобразовании последовательного кода в параллельный данные загружаются в регистр через последовательный вход, после чего они могут быть считаны со всех разрядов регистра одновременно. Типичные примеры использования: построение приёмников для последовательных интерфейсов; вывод контролирующих кодов в БИС с ограниченным числом контактных площадок и т.д.

Хранение чисел в ОЗУ с небольшим объемом данных с последовательной выборкой основано на замыкании сдвигового регистра в кольцо, вкоторомданныемогутзаписываться, храниться исчитываться.

Логические и арифметические сдвиги относятся к командам и выполняются регистрами-аккумуляторами, входящими в состав центральных процессорных элементов всех микропроцессорных комплектов.

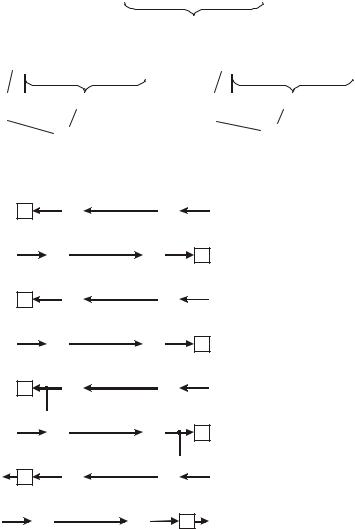

Команды выполняются для данных (чисел) без знака и чисел со знаком (рис.2.49). В большинстве микропроцессоров реализуются восемь команд сдвига, представленных на рис.2.50 [20]. Для всех команд сдвига используется бит переноса С регистра состояний, который является как бы расширением операнда битом 9. Далее под операндом подразумеваются данные без знака либо числа со знаком. Четыре из восьми команд сдвигают операнд, а другие четыре вращают или циклически сдвигают операнд. Командысдвигаициклического сдвигаобразуютдве группы.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

b7 |

|

|

|

|

|

|

... |

|

|

|

|

|

|

b0 |

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

1 |

|

0 |

|

1 |

|

0 |

|

|

1 |

|

1 |

|

1 |

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Данныеабез знака |

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

b7 |

|

|

|

|

|

|

|

|

... |

|

|

|

|

|

|

b0 |

|

|

|

|

|

|

|

|

|

|

b7 |

|

|

|

... |

|

|

|

|

b0 |

|||||||||

|

|

0 |

|

0 |

|

0 |

|

|

0 |

|

1 |

1 |

|

0 |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

1 |

|

1 |

|

1 |

|

0 |

1 |

0 |

|

0 |

|

|||||

Знак |

|

|

|

|

|

|

|

|

Число |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Знак |

Дополнительный код числа |

||||||||||||||||||||||

числа |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

числа |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

+12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

-12 |

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

б |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

в |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

Рис.2.49. Представление данных в формате 1 байт (8 бит): |

|

|

||||||||||||||||||||||||||||||||||||||

|

|

|

|

а - без знака; б - положительных чисел; в - отрицательных чисел |

|||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

SHL |

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

b7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

b0 |

|

|

|

Логический сдвиг влево |

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

SHR |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

b7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

b0 |

|

|

|

|

Логический сдвиг вправо |

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

SAL |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

b7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

b0 |

|

|

|

Арифметический сдвиг влево |

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SAR |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

b7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

b0 |

|

|

|

|

C |

Арифметический сдвиг вправо |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ROL |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

C |

|

|

|

|

|

b7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

b0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Циклический сдвиг влево |

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ROR |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

b7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

b0 |

|

|

|

|

Циклический сдвиг вправо |

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RCL |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

C |

|

|

|

|

|

b7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

b0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Циклический сдвиг |

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

с переносом влево |

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

C |

|

|

|

|

|

|

|

|

RCR |

|

|

|

|

|

||||

|

|

|

|

|

|

b7 |

|

|

|

|

|

|

|

|

|

|

b0 |

|

|

|

|

|

|

Циклический сдвиг |

|

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

с переносом вправо |

|

|

|||||||||||

Рис.2.50. Команды сдвига

Логические команды сдвигают операнд, не считаясь с его знаком, или используются для действий над числами без знака и над нечисло-

выми значениями, например над масками. Сдвиг осуществляется по всем позициям регистра.

Арифметические команды сохраняют знаковый (старший) разряд операнда и используются для действия с числами со знаком; отметим, что арифметический сдвиг влево совпадает с логическим сдвигом влево.

Отметим несколько обстоятельств, которые необходимо иметь в виду, работая с командами простого и циклического сдвига. Во-первых, любая из выполняемых при этом операций эквивалентна умножению (сдвиг влево) или делению (сдвиг вправо) числа на 2 при сдвиге на один разряд. Во-вторых, при использовании команд простого сдвига данные, сдвигаемые за пределы регистра, теряются. В-третьих, команды циклического сдвига сохраняют сдвинутые за пределы регистра биты, помещая их обратно в регистр. В-четвертых, команды сдвига взаимодействуют с флагами регистра состояния. Разряд переноса С регистра состояния участвует в выполнении команд, и его значение изменяется по мере передачи данных в него или из него.

Рассмотрим подробнее все эти операции (команды).

Логический (SHL - shift logical left), арифметический (SAL - shift arithmetic left) сдвиг влево - эта команда часто используется для реализации операции умножения. Как видно из рис.2.50, при выполнении этих команд содержимое старшего разряда регистра передаётся в разряд переноса С регистра состояния. В младший разряд b0 регистра загружается при этом 0. Содержимое каждого разряда регистра перемещается в соседний старший разряд, а содержимое разряда переноса С (независимо от его значения) теряется. Команда SAL не сохраняет знак операнда, но заносит 1 во флаг переполнения V регистра состояния в случае изменения знака операнда.

Логический сдвиг вправо (SHR - shift logical right) - эта команда часто используется для операции деления. Как видно из рис.2.50, при выполнении этой команды содержимое младшего разряда b0 регистра передаётся в разряд переноса С регистра состояния. В старший разряд b7 регистра загружается при этом 0. Содержимое каждого разряда регистра перемещается в соседний младший разряд, а содержимое разряда переноса С теряется.

Арифметический сдвиг вправо (SAR - shift arithmetic right) - со-

держимое младшего разряда передаётся в разряд переноса С регистра состояний, содержимое всех остальных разрядов числа сдвигается вправо на одну позицию. Отличительной особенностью команды является то, что старший (знаковый) разряд сохраняет свое значение, это необходимо при выполнении некоторых арифметических операций в дополнительном коде. Содержимое разряда переноса С теряется.

Циклический сдвиг влево (ROL - rotate left) - содержимое старшего разряда b7 регистра загружается в разряд переноса С регистра состояния. Все разряды операнда, находящегося в регистре, сдвигаются на одну пози-

цию влево, т.е. содержимое каждого разряда перемещается в позицию соседнего старшегоразряда, асодержимоеразрядаb7 загружаетсявразрядb0.

Циклический сдвиг вправо (ROR - rotate right) - содержимое младшего разряда b0 регистра загружается в разряд переноса С регистра состояния. Все разряды операнда, находящегося в регистре, сдвигаются на одну позицию вправо, т.е. содержимое каждого разряда перемещается в позицию соседнего младшего разряда, а содержимое разряда b0 загружается в разряд b7.

Циклический сдвиг с переносом влево (RCL - rotate left through carry) - этой командой все данные, находящиеся в регистре и разряде переноса, сдвигаются на одну позиция влево, причём содержимое b7 загружается в разряд переноса С, а последний - в разряд регистра b0.

Циклический сдвиг с переносом вправо (RCR - rotate right through carry) - этой командой все данные, находящиеся в регистре и разряде переноса, сдвигаются на одну позиция вправо, причём содержимое b0 загружается в разряд переноса С, а последний - в разряд регистра b7.

При использовании команд циклического сдвига не происходит потерьданных, посколькуданныеперемещаются позамкнутомуконтуру.

Пример 2.19. Спроектировать операционный блок, выполняющий указанные восемь операций сдвига, на реверсивном восьмиразрядном сдвиговом регистре. В качестве разряда переноса С регистра состояний использовать отдельный триггер. Сигнал m направления сдвига закодировать так: m = 0 - сдвиг влево, m = 1 - сдвиг вправо. Триггер переноса и регистр должны иметь единую систему синхронизации.

Так как всего выполняется восемь операций, закодируем их 3-разрядным кодом а2а1а0. Функционирование операционного блока

представлено в табл.2.22. Рассматривая Ct +1, b7t +1, b0t +1 и m как функции

алгебры логики (ФАЛ) от переменных a2 , a1, a0 ,Ct ,b7t и b0t , из табл.2.22 получаем выражения в СДНФ:

Dct = Ct +1 = a2a1a0b7 + a2a1a0b0 + a2a1a0b7 + a2a1a0b0 + + a2a1a0b7 + a2a1a0b7 + a2a1a0b7 + a2a1a0b0;

DLt = b7t +1 = a2a1a0b7 + a2a1a0b0 +a2a1a0C;

DRt = b0t +1 = a2a1a0b7 +a2a1a0C;

m = a2a1a0 + a2a1a0b0 +a2a1a0 +a2a1a0.

Таблица 2.22

Функционирование операционного блока, реализующего восемь сдвиговых команд

|

Операция |

набораНомер |

|

a2 |

|

|

|

a1 |

|

|

a0 |

|

C t+1 |

b 7t+1 |

b 0t+1 |

m |

|

||

|

SHL |

|

0 |

|

0 |

|

|

|

0 |

|

|

0 |

|

b 7t |

|

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SHR |

|

1 |

|

0 |

|

|

|

0 |

|

|

1 |

|

b 0t |

0 |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SAL |

|

2 |

|

0 |

|

|

|

1 |

|

|

0 |

|

b 7t |

|

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SAR |

|

3 |

|

0 |

|

|

|

1 |

|

|

1 |

|

b 0t |

b 1t |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ROL |

|

4 |

|

1 |

|

|

|

0 |

|

|

0 |

|

b 7t |

|

b 7t |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ROR |

|

5 |

|

1 |

|

|

|

0 |

|

|

1 |

|

b 0t |

b 0t |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RCL |

|

6 |

|

1 |

|

|

|

1 |

|

|

0 |

|

b 7t |

|

Ct |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RCR |

|

7 |

|

1 |

|

|

|

1 |

|

|

1 |

|

b 0t |

Ct |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

После минимизации получаем |

|

|

|

|

|

|

|

|

|

||||||||||

|

Dc t =Ct +1 = a0b7 +a0b0 ; |

|

|

|

|

|

|

||||||||||||

|

t |

t +1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

DL |

|

=b7 |

= (a2a1b7 +a2a1b0 +a2a1C)a0 ; |

(2.38) |

||||||||||||||

|

DRt =bt +1 |

= a |

2 |

a |

0 |

(a b |

+a C); |

|

|

|

|

||||||||

|

|

|

0 |

|

|

|

|

1 |

7 |

|

1 |

|

|

|

|

||||

|

m = a0. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

Уравнения (2.38) определяют структуру операционного блока, которая и приведена на рис.2.51. 8-разрядный сдвиговый регистр показан в обобщённомвиде, таккакможетбытьреализованвразличных вариантах. Нарис.2.51 обозначено: V - вход выбора режима (например, V = 0 - параллельная загрузка, V = 1 - сдвиг); DR (data right) - данныесправа(состоронымладшихразря-

дов), на этот вход подаётся сигнал b0t +1 ; DL (data left) - данные слева (со стороныстаршихразрядов), наэтотвходподаётсясигнал b7t +1 .

|

|

|

|

R |

TT |

C |

|

|

& |

1 |

|

||

|

|

D |

|

|

||

|

|

|

|

|

|

|

|

|

& |

|

C |

|

|

|

|

|

|

S |

|

|

|

|

& |

1 |

|

|

|

|

|

& |

& |

R |

RG |

|

|

|

|

V |

b0 |

||

|

|

|

|

|

||

|

|

|

|

|

Q0 |

|

|

|

|

|

m |

|

b1 |

|

|

|

|

|

Q1 |

|

|

|

|

|

DR |

|

b2 |

|

|

|

|

|

Q2 |

|

|

|

& |

1 |

DL |

|

b3 |

|

|

|

Q3 |

|||

a2 |

1 |

1 |

|

D0 |

|

b4 |

|

|

|

|

|

Q4 |

|

|

|

& |

|

D1 |

|

b5 |

|

|

& |

D2 |

|

Q5 |

|

|

|

|

D3 |

|

b6 |

|

a1 |

1 |

1 |

|

D4 |

|

Q6 |

|

|

& |

|

D5 |

|

b7 |

|

|

|

D6 |

|

Q7 |

|

|

|

|

|

D7 |

|

|

a0 |

1 |

1 |

|

C |

|

|

|

|

|

|

|||

Уст. «0» |

|

|

|

|

|

|

V |

|

|

|

|

|

|

С (синхр.) |

|

|

|

|

|

|

|

|

Рис.2.51. Схема операционного блока |

|

|

|

|

2.5. Кольцевые счётчики

Кольцевым счётчиком называется сдвиговый регистр, замкнутый в кольцо. Далее рассмотрены схемы, выполненные на D-триггерах, либо схемы, имеющие однофазный последовательный вход и выход. Структуры, выполненные на других типах триггеров, могут быть получены аналогичными методами.

Наиболее распространены две схемы кольцевых счётчиков:

• для первой схемы для всех n разрядов выполняется соотношение

Di =Qi−1 ;

• для второй схемы для n − 1 разрядов выполняется соотношение Di = Qi−1 , а для одного разряда D0 = Qn−1 , т.е. реализуется одна пере-

крестная связь.

Поскольку счётчик кольцевой, не имеет значения, между какими разрядами выполняется перекрестная связь, однако для удобства анализа на схемах для наглядности соединяют выход последнего разряда со входом первого.

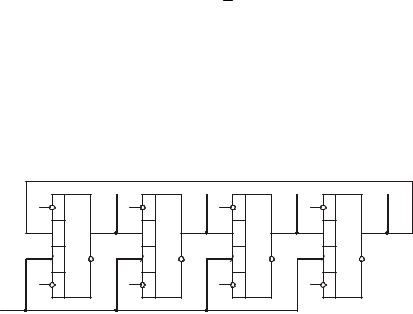

Схемы с одной перекрестной связью называют кольцевыми распределителями, счётчиками Джонсона, счётчиками Мёбиуса, счётчиками в коде Либау-Крейга, кольцами Реженера. На рис.2.52 приведена схема четырёхразрядного кольцевого счётчика с прямыми связями между разрядами, а на рис.2.53 - временные диаграммы этой схемы.

Q0 |

Q1 |

Q2 |

Q3 |

R TT |

R TT |

R TT |

R TT |

D |

D |

D |

D |

C |

C |

C |

C |

S |

S |

S |

S |

C

Рис.2.52. Кольцевой счётчик с прямыми связями

Вариант, показанный на рис.2.53,а, соответствует сдвигу в кольце одной единицы, на рис.2.53,б - сдвигу двух смежных единиц, на рис.2.53,в - сдвигу двух единиц, разделённых нулём, на рис.2.53,г - сдвигу трёх смежных единиц (или одного нуля). Все эти варианты возможны из-за первичного включения схемы либо из-за действия помех на схему. Более наглядно эти (и два дополнительных) варианта отражены на графе переходов схемы рис.2.54,а. Из графа ясно, что шесть возможных замкнутых циклов работы, раз возникнув, могут сами не перейти в нужный для работы цикл. Пусть нужный для работы цикл имеет последовательность следующих состояний: 1-2-4-8-1-… (на рис.2.54,б этот цикл выделен жирными линиями переходов). Анализируя полный граф переходов на рис.2.42,г, определим вхождение в рабочий цикл из любого нерабочего состояния с минимальным числом переходов в рабочий цикл. Результаты анализа отражены на рис.2.54,б.