- •2. Основные понятия алгебры логики

- •3. Цифровые интегральные микросхемы

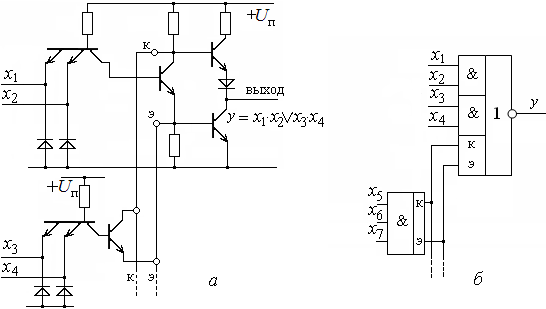

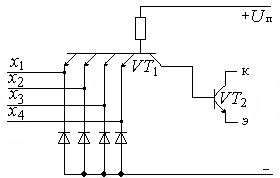

- •4. Логические элементы на кмоп-транзисторах

- •5. Схемотехника интегральных схем инжекционной логики и эсл

- •6. Триггеры

- •7. Счетчики

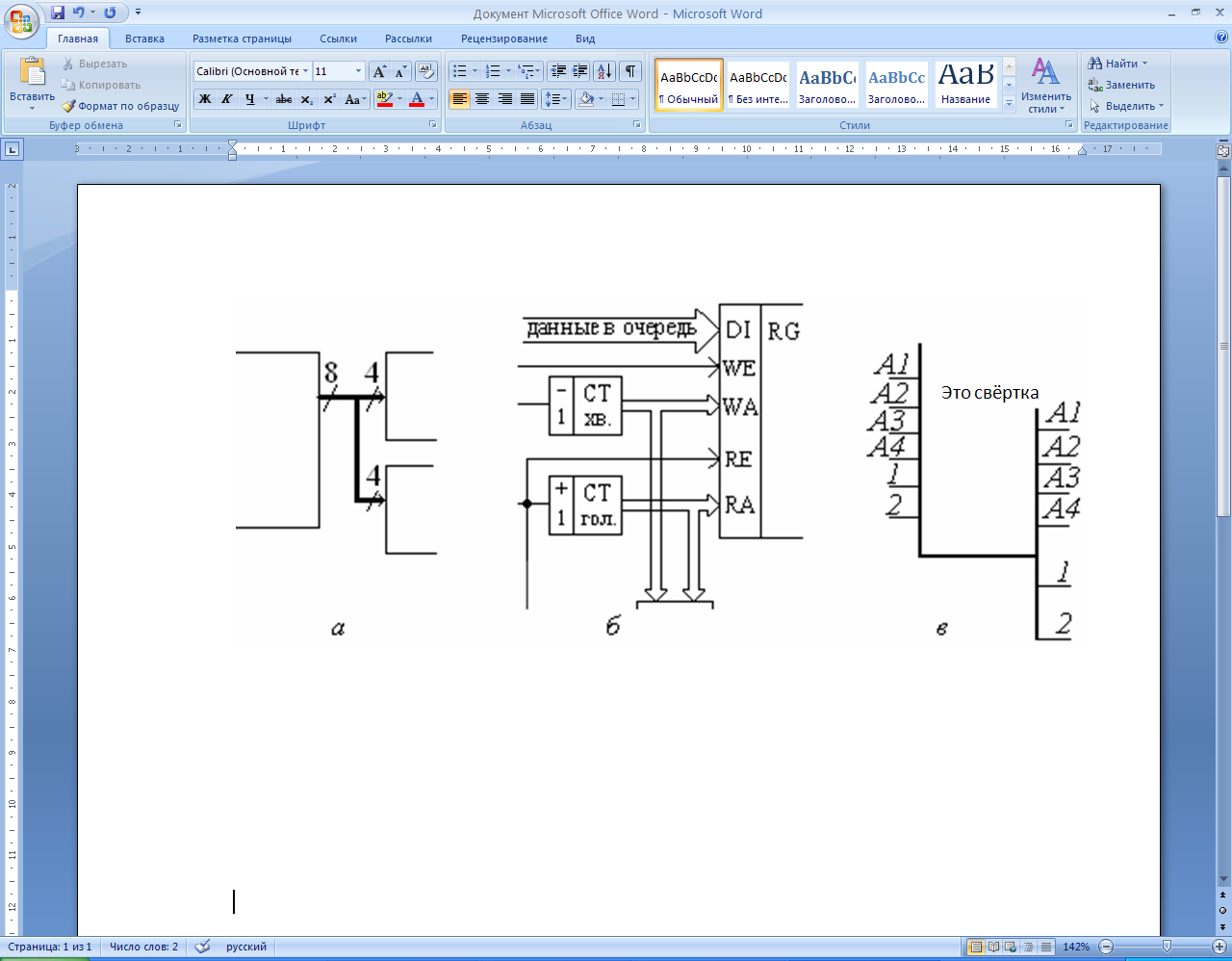

- •8. Регистры

- •9. Мультиплексоры и демультиплексоры

- •10. Шифраторы и дешифраторы

- •11. Арифметические устройства

- •12. Импульсные устройства на имс

- •13. Запоминающие устройства

- •14. Аналого-цифровые и цифро-аналоговые преобразователи

ПРИЛОЖЕНИЕ 3

СХЕМОТЕХНИКА ЭВМ

СБОРНИК ИЛЛЮСТРАЦИОННЫХ МАТЕРИАЛОВ

ОГЛАВЛЕНИЕ

2. ОСНОВНЫЕ ПОНЯТИЯ АЛГЕБРЫ ЛОГИКИ 13

3. ЦИФРОВЫЕ ИНТЕГРАЛЬНЫЕ МИКРОСХЕМЫ 18

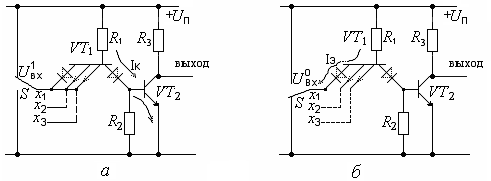

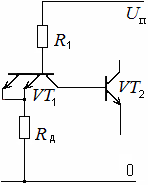

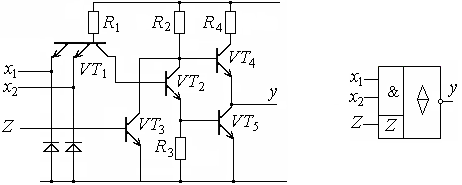

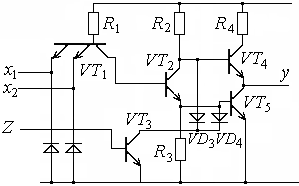

4. ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ НА КМОП-ТРАНЗИСТОРАХ 32

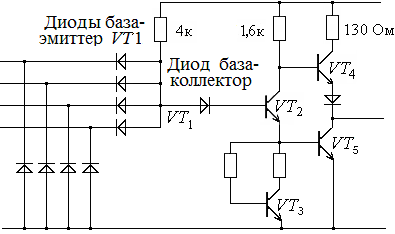

5. СХЕМОТЕХНИКА ИНТЕГРАЛЬНЫХ СХЕМ ИНЖЕКЦИОННОЙ ЛОГИКИ И ЭСЛ 35

6. ТРИГГЕРЫ 39

7. СЧЕТЧИКИ 48

8. РЕГИСТРЫ 53

9. МУЛЬТИПЛЕКСОРЫ И ДЕМУЛЬТИПЛЕКСОРЫ 60

10. ШИФРАТОРЫ И ДЕШИФРАТОРЫ 64

11. АРИФМЕТИЧЕСКИЕ УСТРОЙСТВА 71

13. ЗАПОМИНАЮЩИЕ УСТРОЙСТВА 85

14. АНАЛОГО-ЦИФРОВЫЕ И ЦИФРО-АНАЛОГОВЫЕ ПРЕОБРАЗОВАТЕЛИ 87

1. ОСНОВНЫЕ ОПРЕДЕЛЕНИЯ И ХАРАКТЕРИСТИКИ СХЕМ ЦИФРОВЫХ УСТРОЙСТВ

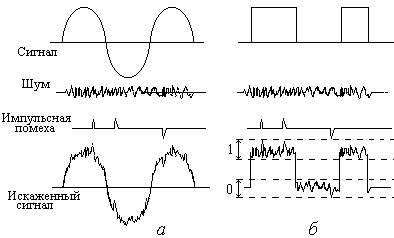

Рис. 1.1. Искажение аналогового (а) и цифрового (б) сигнала.

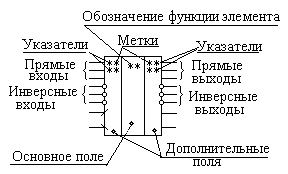

Рис. 1.2. Обозначение входов и выходов микросхемы.

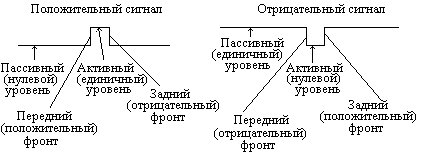

Рис. 1.3. Элементы цифрового сигнала.

Рис. 1.4. Обозначение неинформационных выводов.

Рис.1.5. Обозначение шин: а – толстыми линиями; б – двойными стрелками;

в – нумерация входов и выходов.

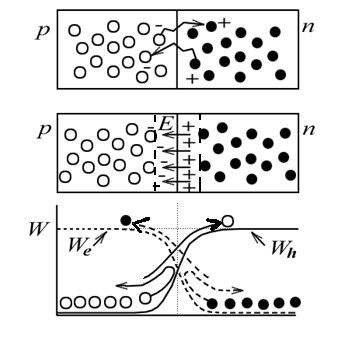

Рис.1.6.Распределение зарядов в области p-n- перехода.

Рис.1.7. Потенциальные пороги вблизи p-n- перехода при прямом (а) и обратном (б) включении внешнего напряжения на нем.

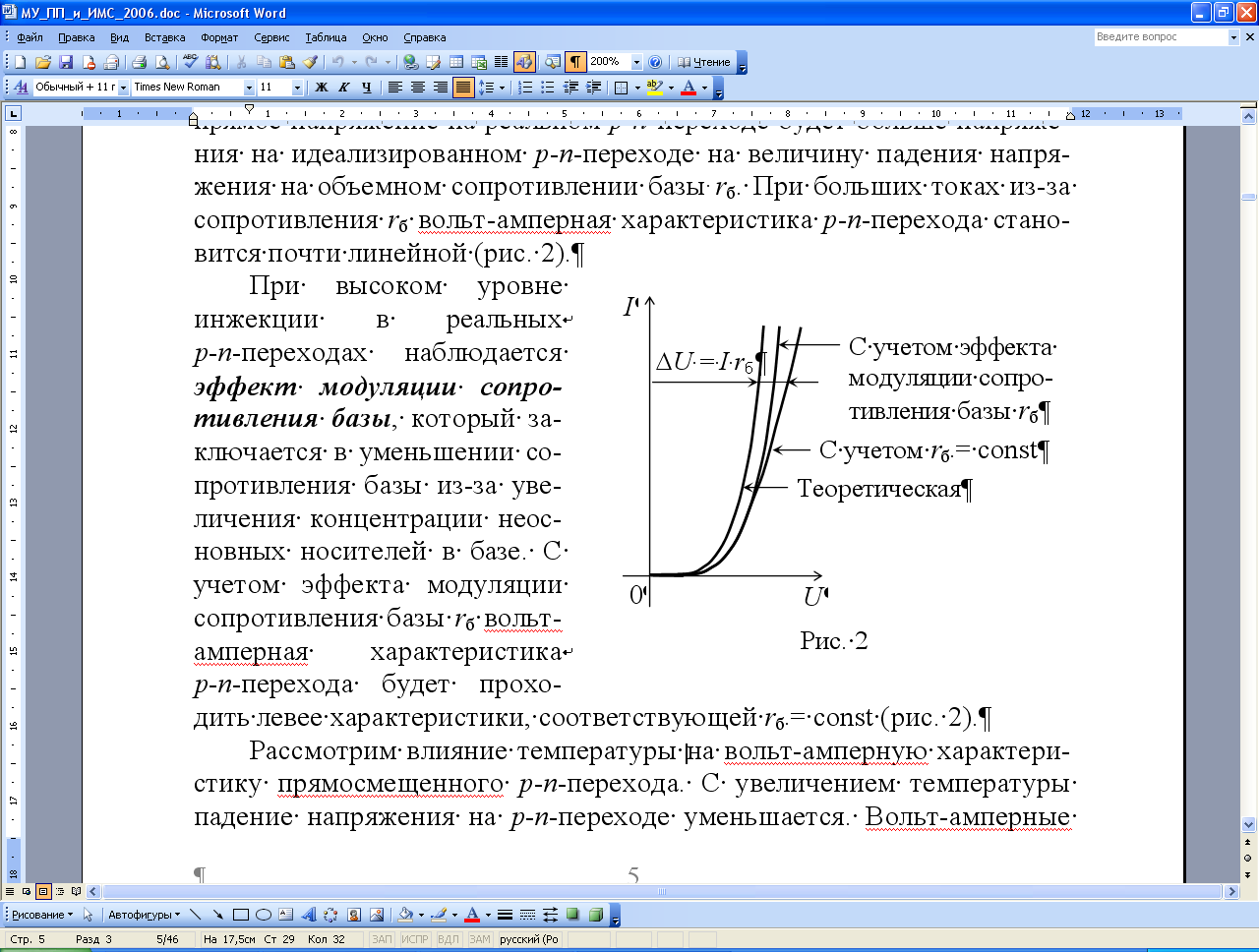

Рис.1.8. Зависимость тока основных и неосновных носителей через p-n- переход от напряжения на нем, ВАХ p-n- перехода.

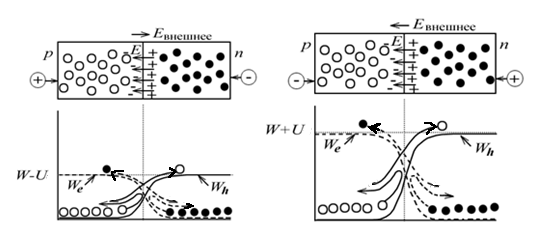

Рис. 1.9. Схема движения электронов и дырок при прямом (а) и обратном (б) включении p-n- перехода.

Рис. 1.10. Идеализированная ВАХ p-n перехода.

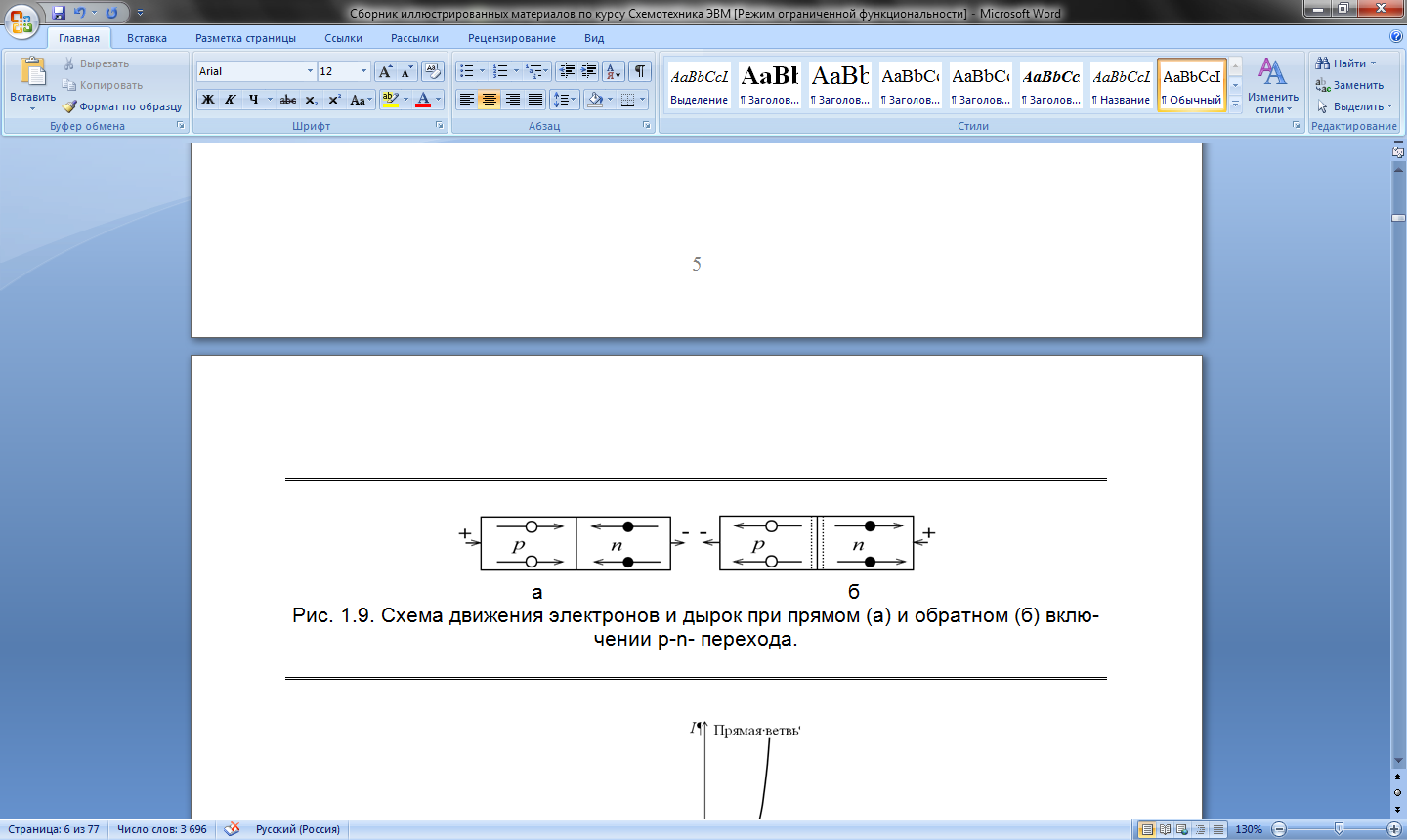

Рис. 1.11. Прямая ветвь ВАХ p-n перехода с учетом различных факторов.

Рис. 1.12. Прямая ветвь ВАХ p-n перехода c учетом различных температур.

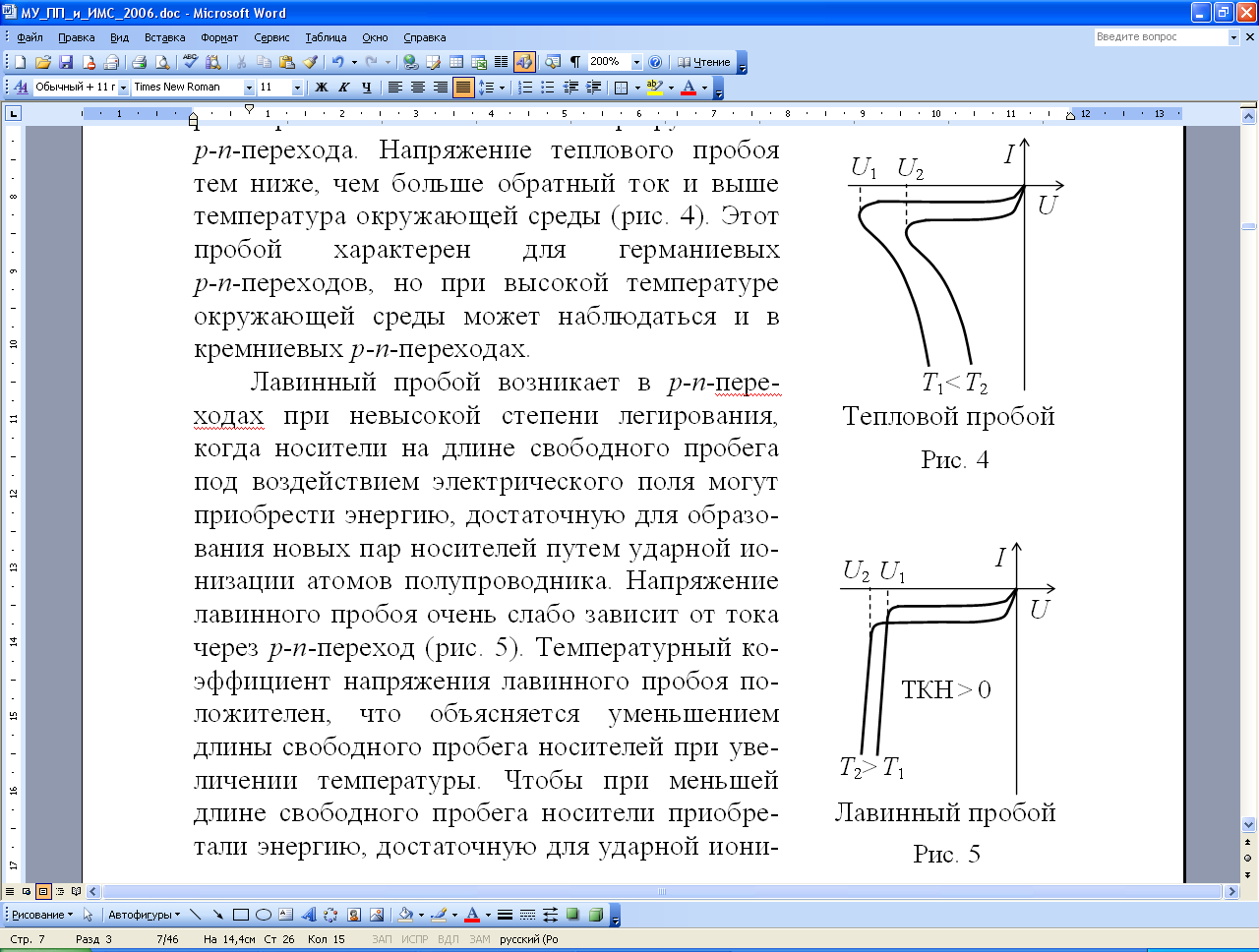

Рис. 1.13. Обратная ветвь ВАХ p-n перехода при тепловом пробое.

Рис. 1.14. Обратная ветвь ВАХ p-n перехода при лавинном пробое.

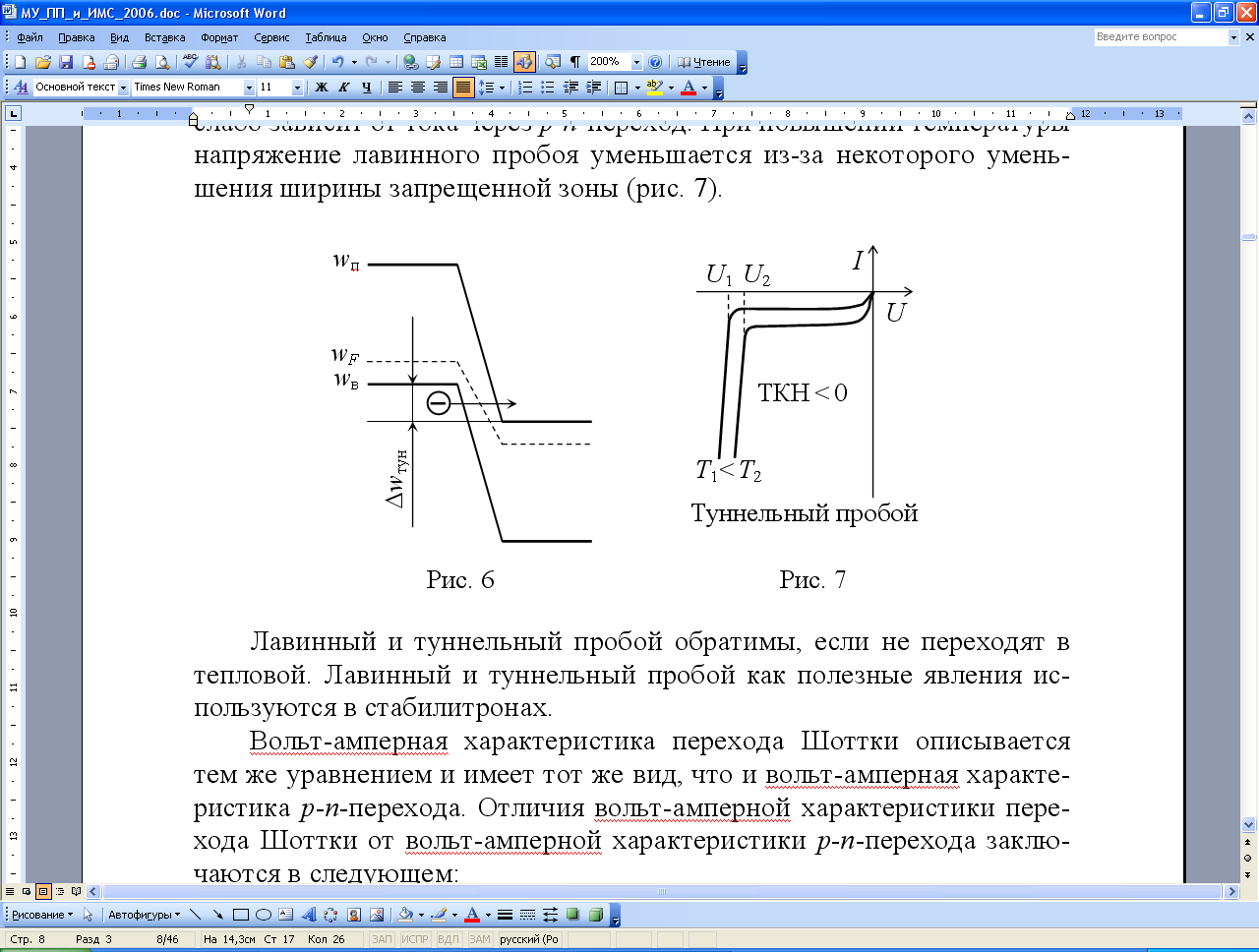

Рис. 1.15. Обратная ветвь ВАХ p-n перехода при туннельном пробое.

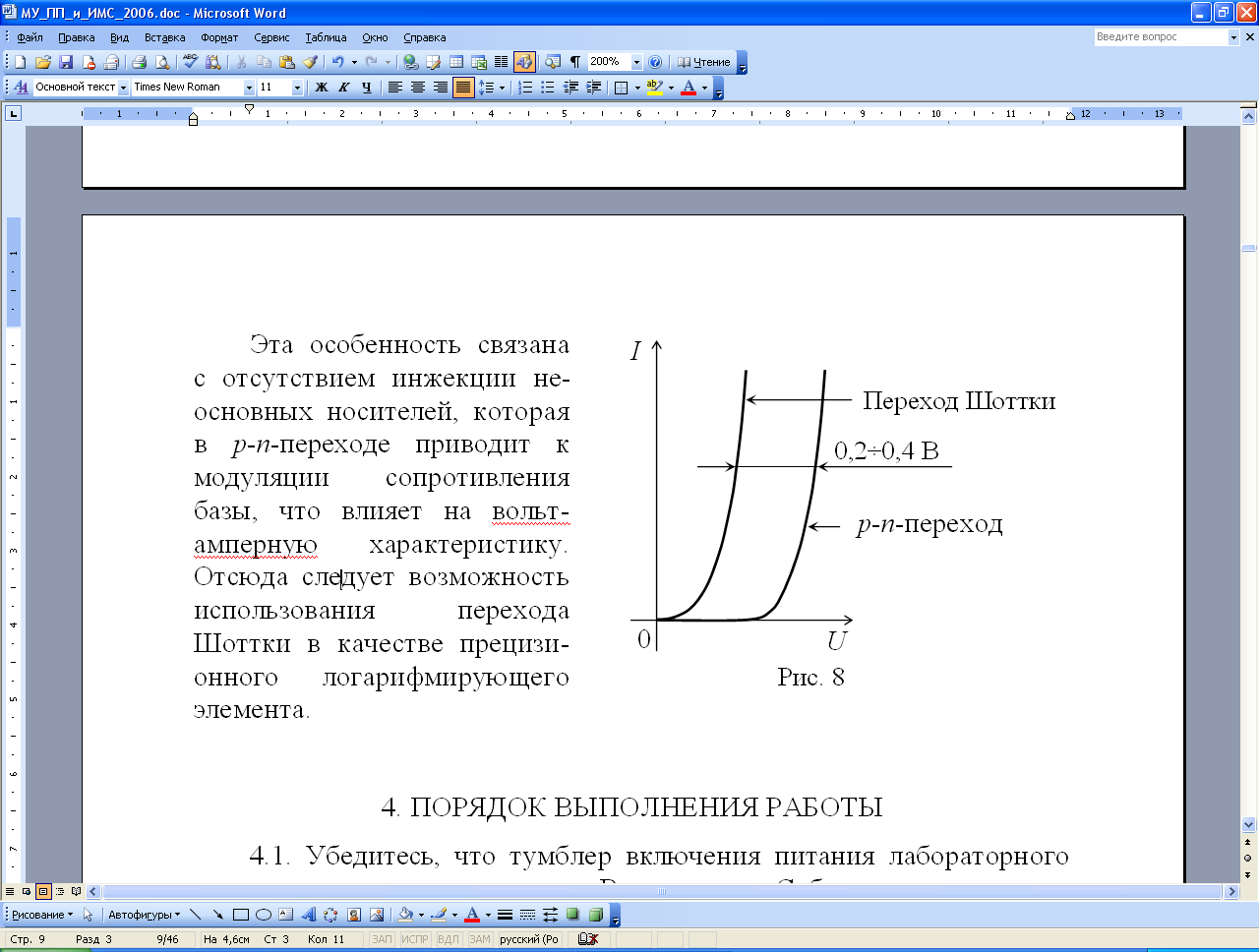

Рис. 1.16 Прямая ветвь ВАХ обусловленная p-n переходом и переходом Шотки.

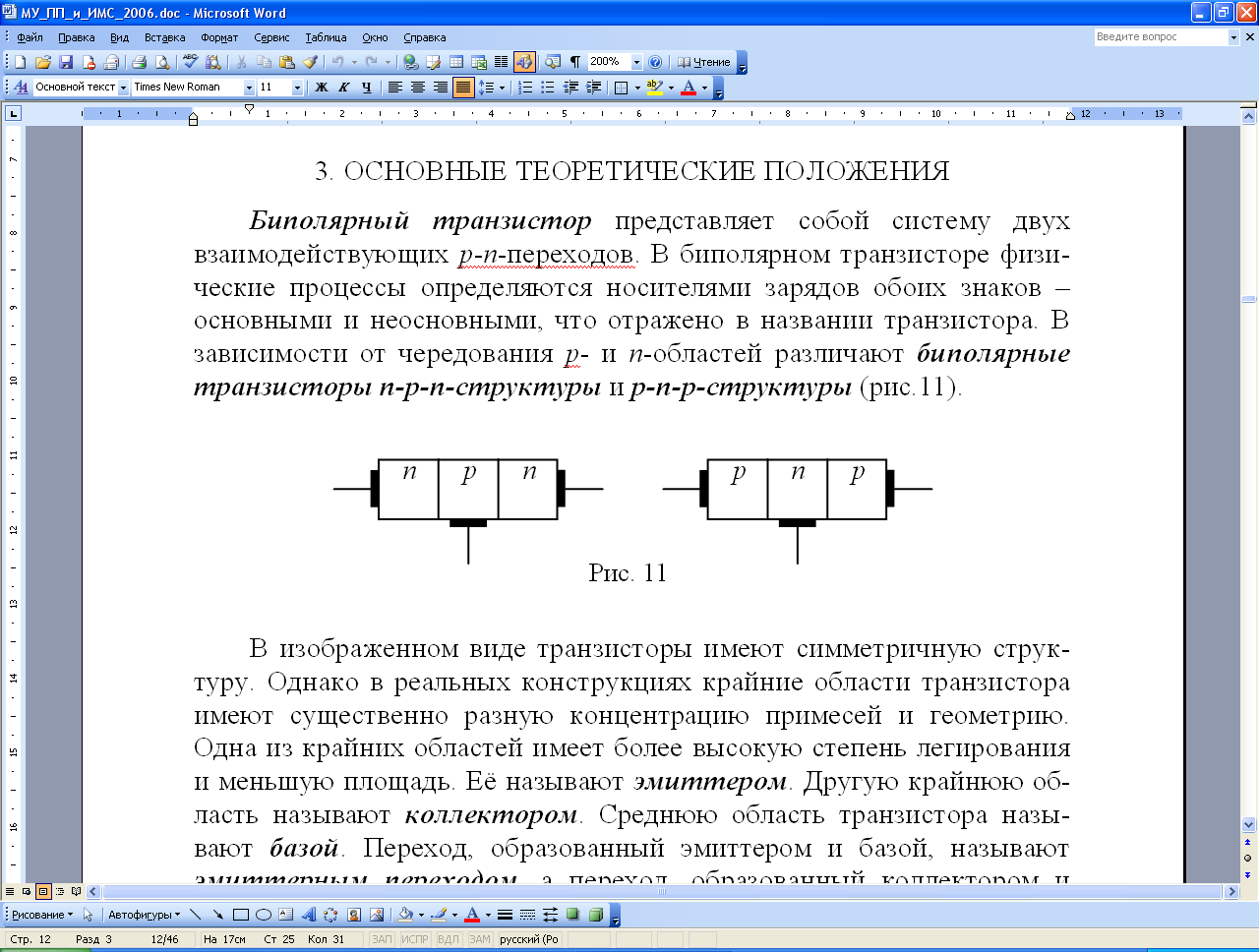

Рис. 1.17. Структуры n-p-n и p-n-p переходов.

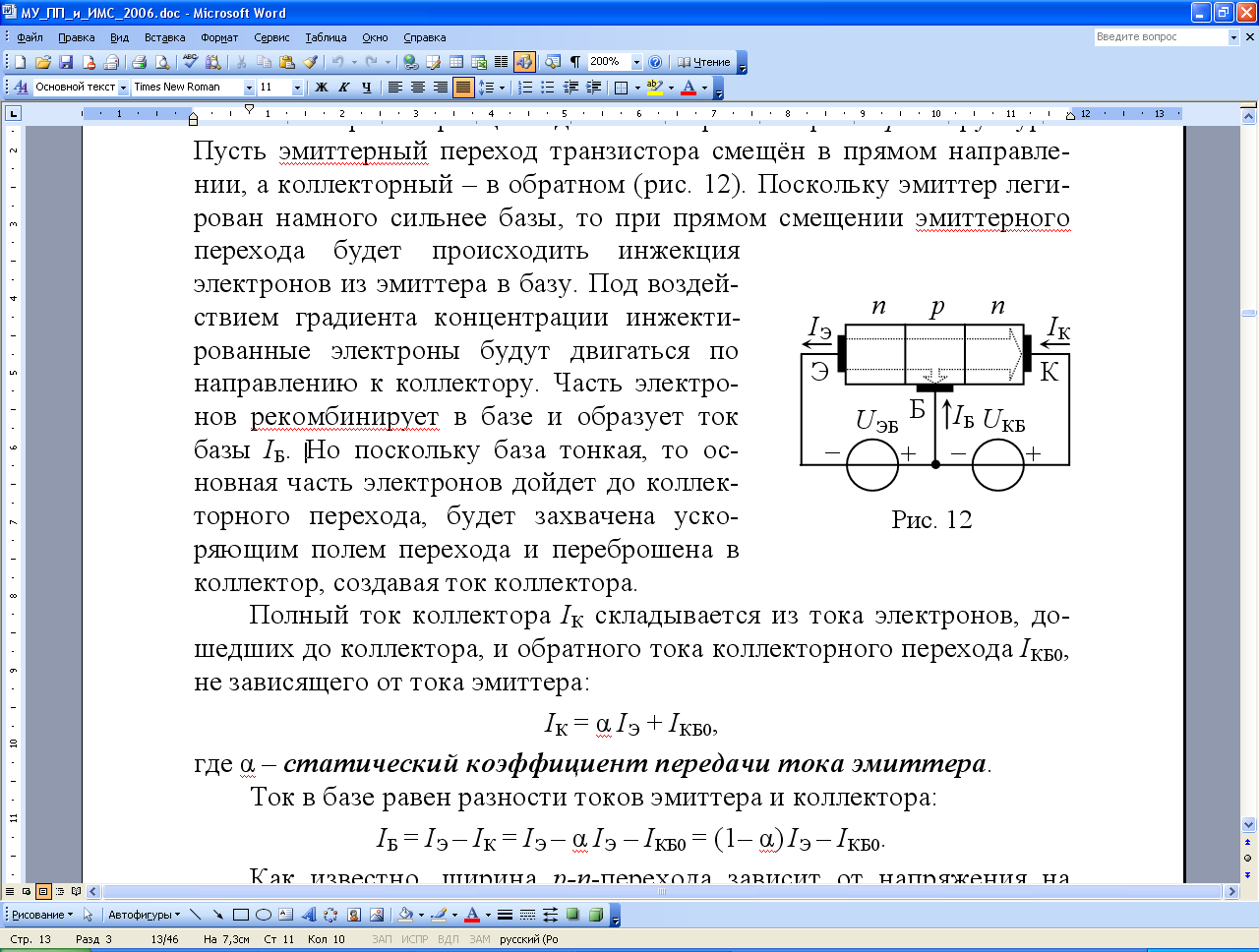

Рис. 1.18. Прямое включение n-p-n транзисторов.

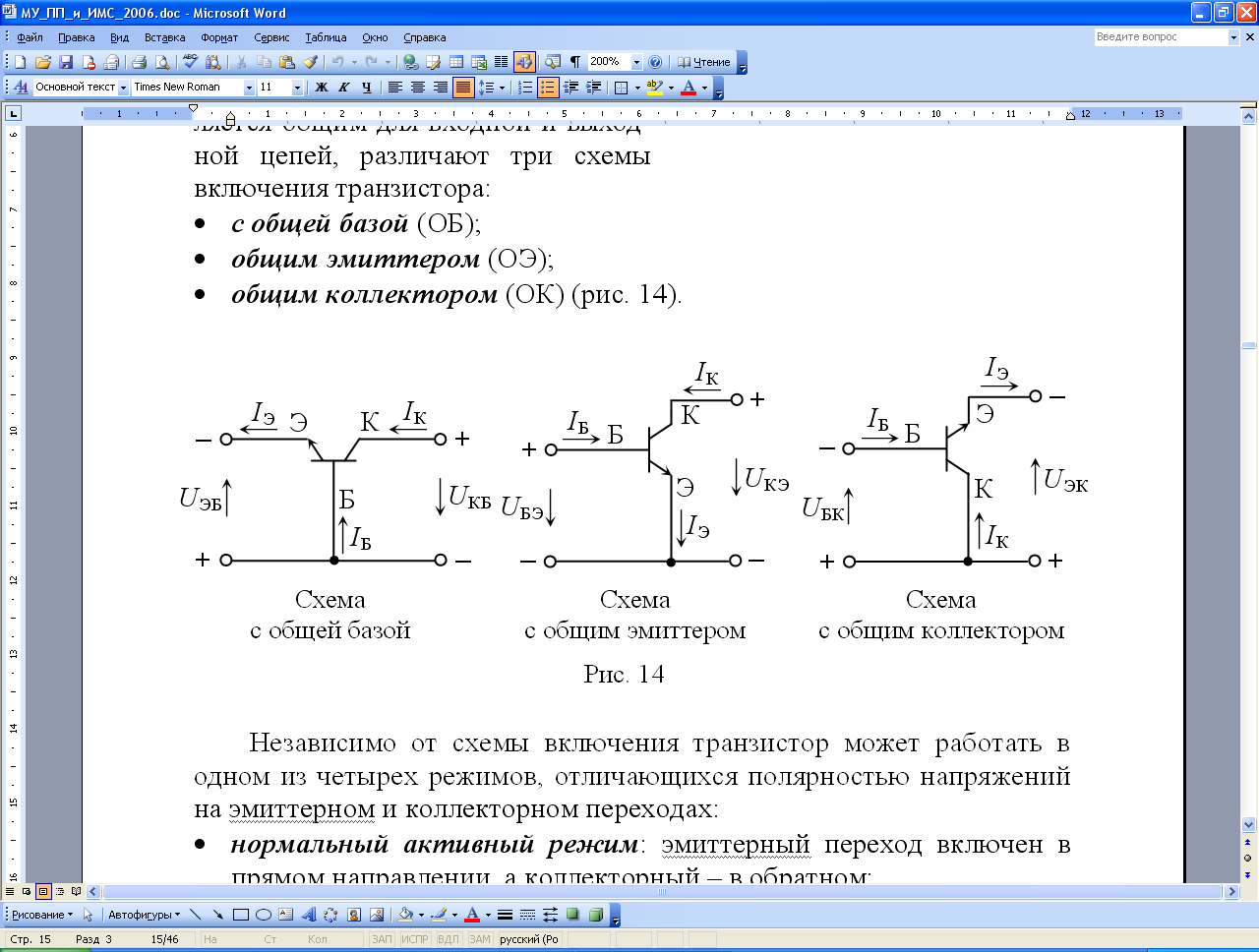

а б в

Рис. 1.19. Возможные схемы включения транзистора:

а. сема с общей базой; б. Схема с общим эмиттером;

в. Схема с общим коллектором.

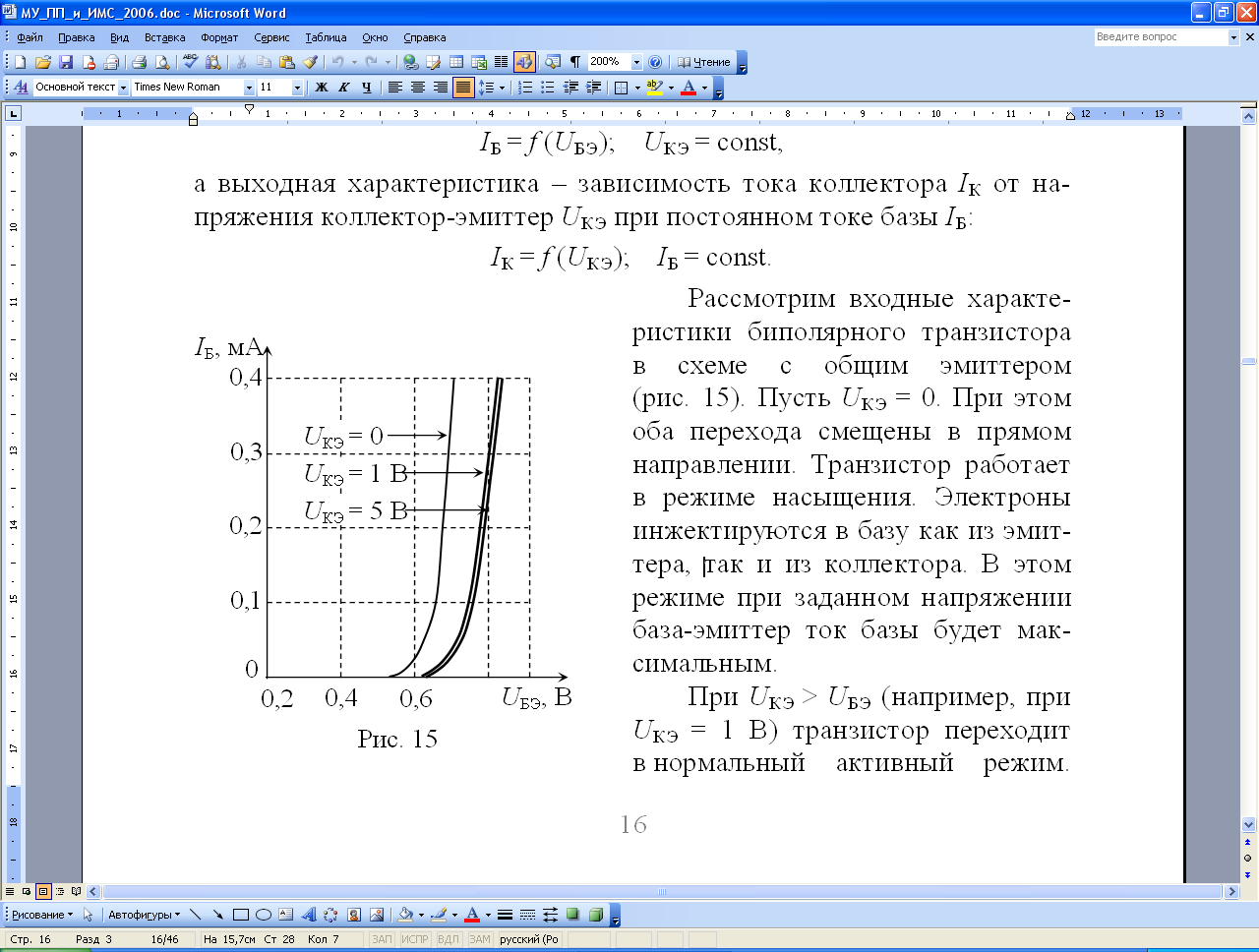

Рис. 1.20. Входные ВАХ характеристики биполярного транзистора в схеме с общим эмиттером

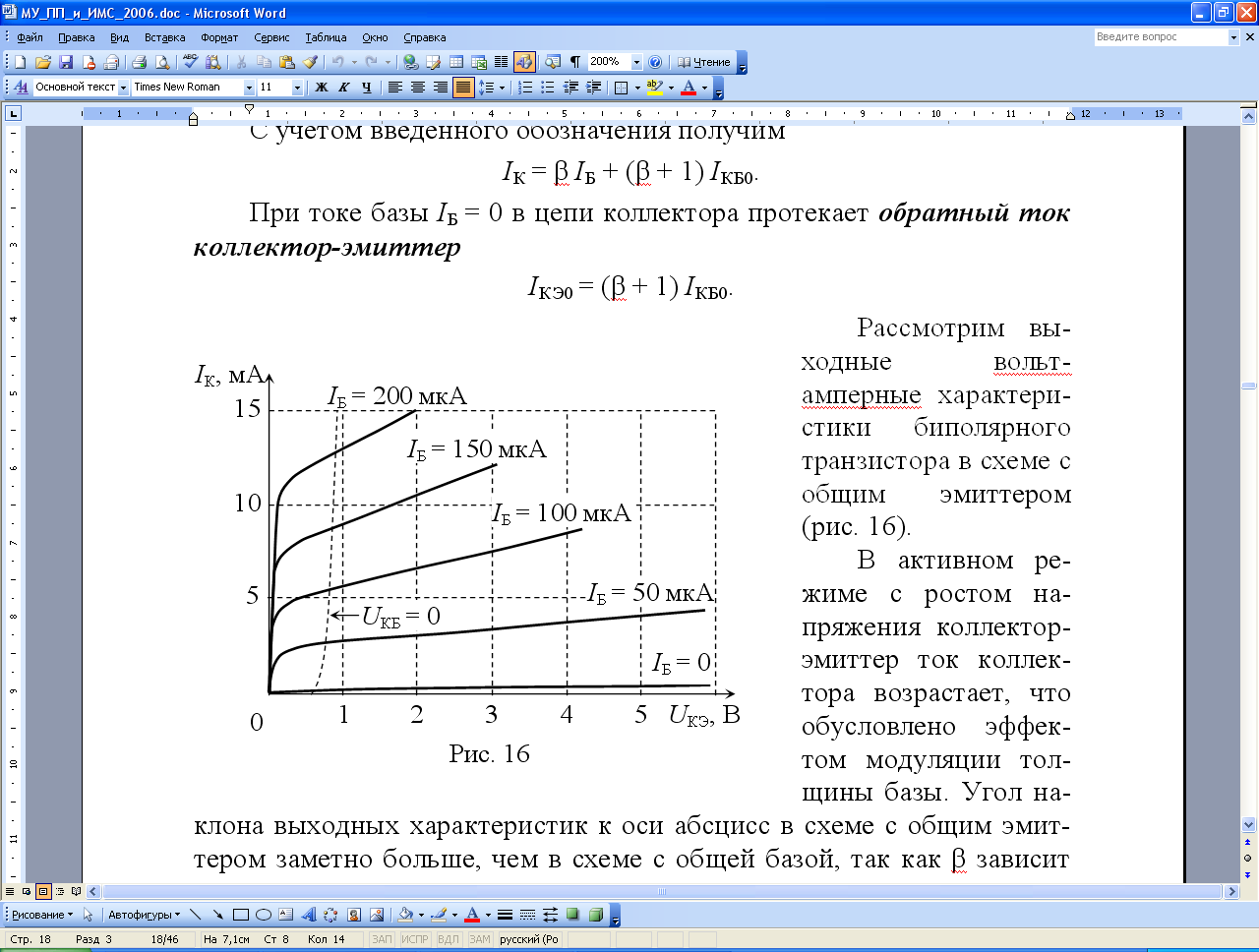

Рис. 1.21. Выходные ВАХ характеристики биполярного транзистора в схеме с общим эмиттером

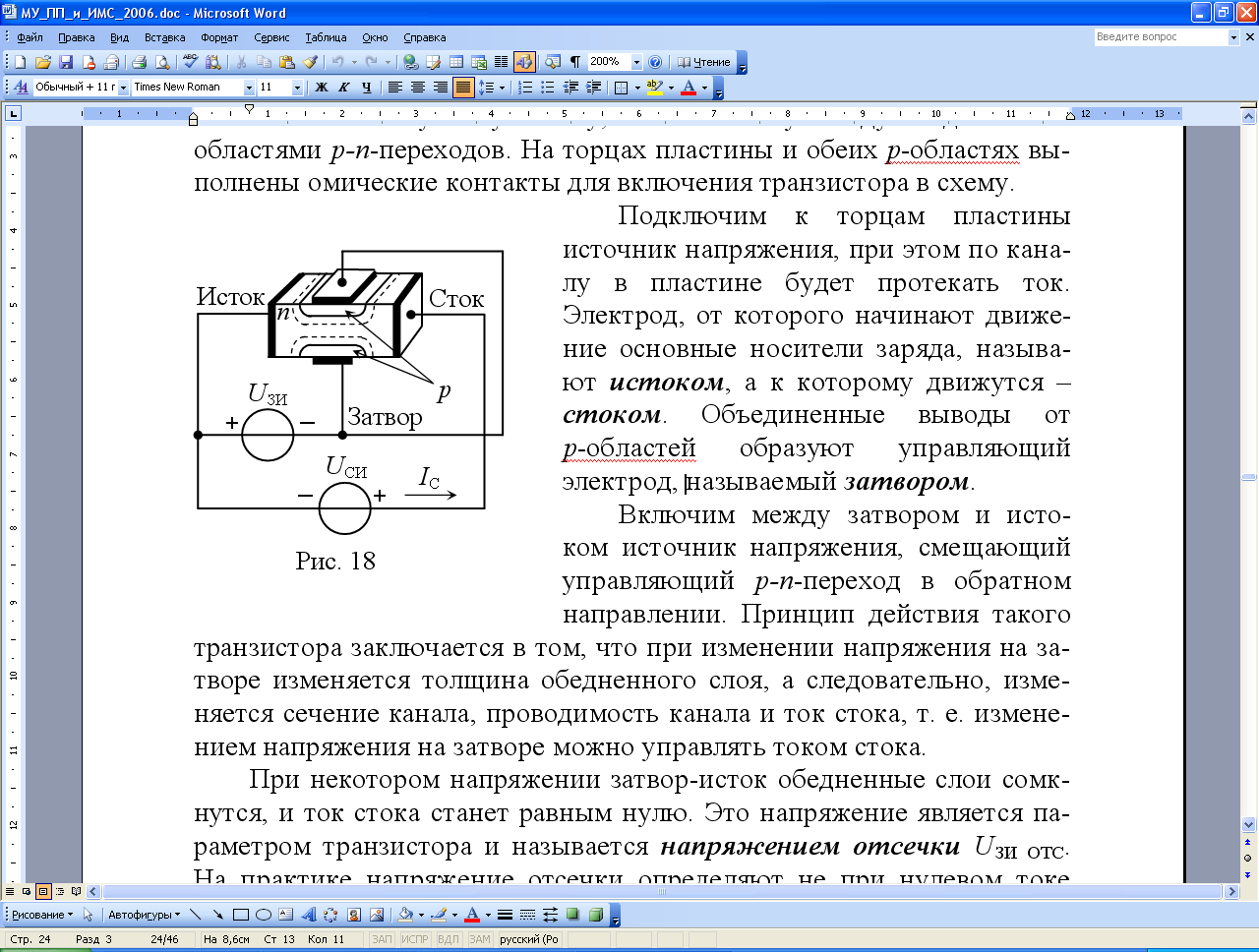

Рис.1.22. Структура полевого транзистора с управляющим p-n-переходом.

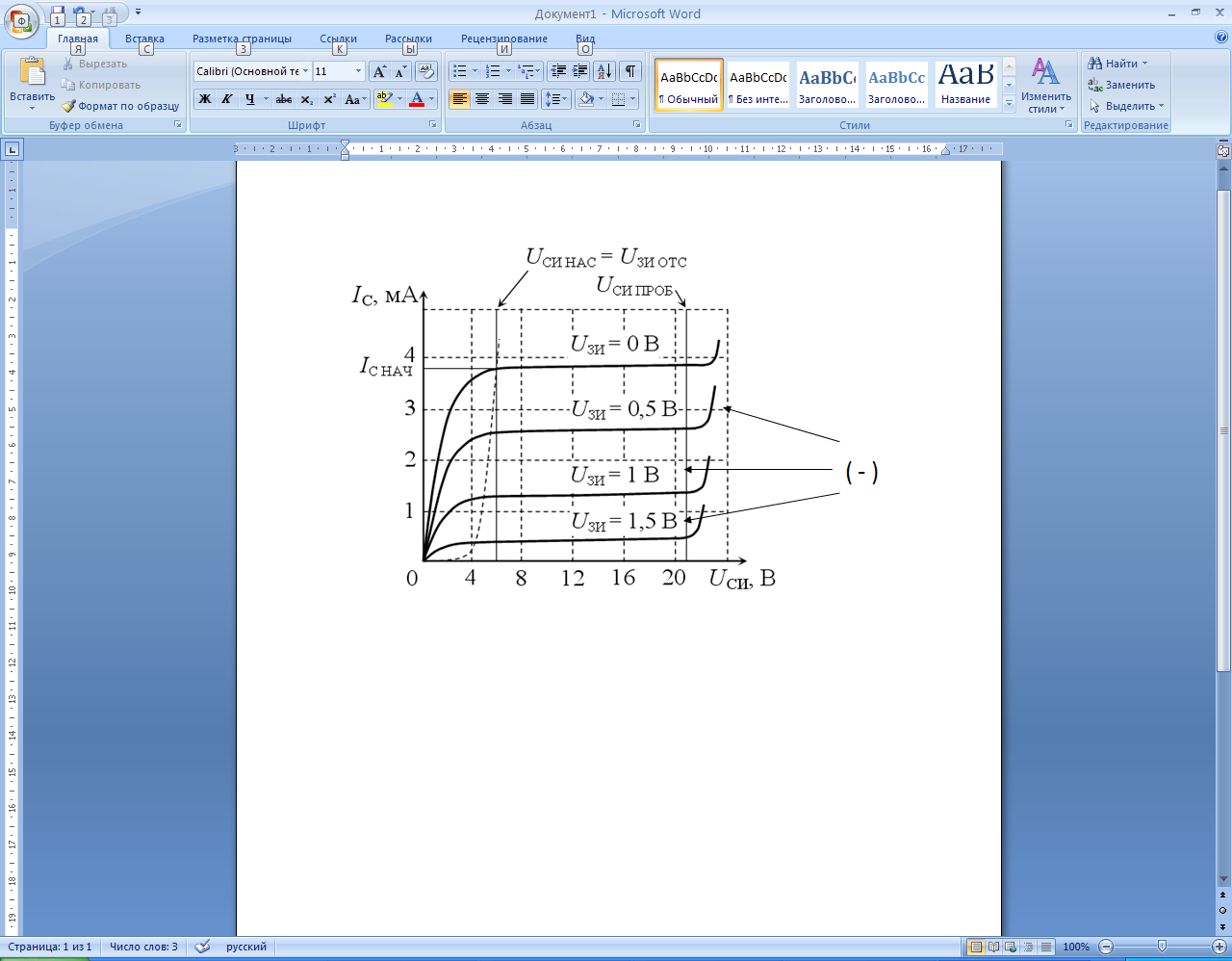

Рис. 1.23 Выходные характеристики полевого транзистора с управляющим p-n переходом.

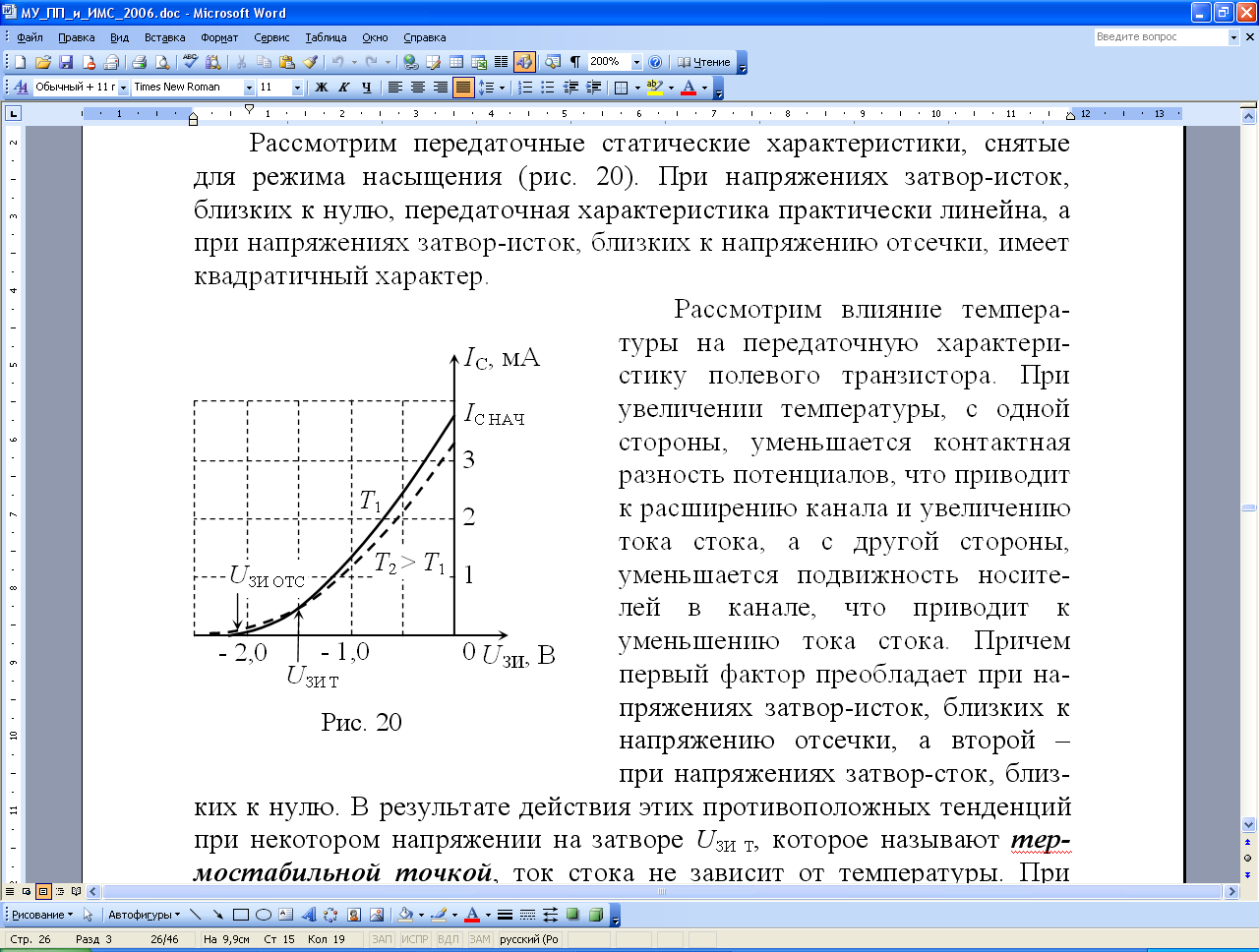

Рис. 1.24. Передаточные статические характеристики для режима насыщения полевого транзистора с управляющим p-n переходом.

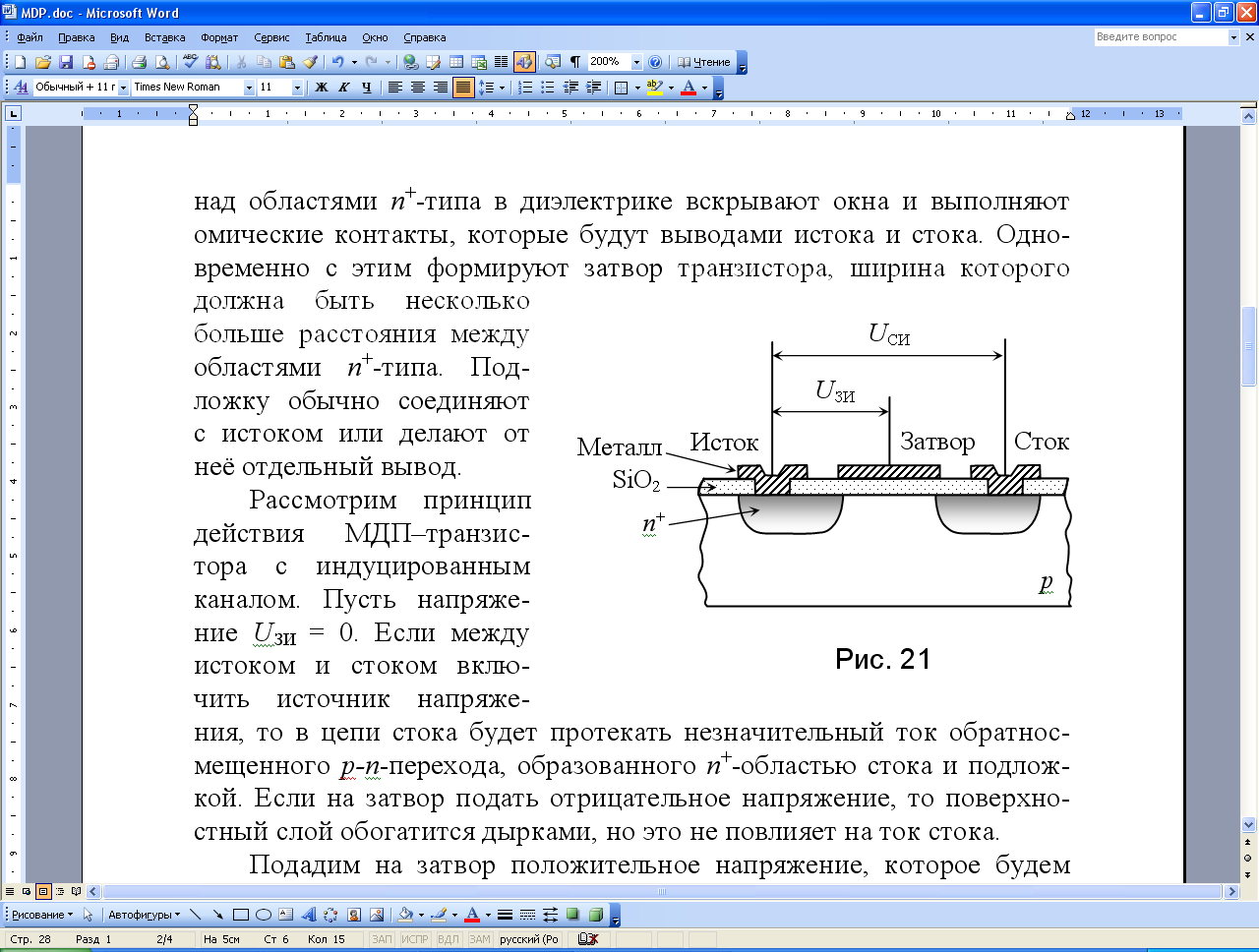

Рис. 1.25. Структура МДП транзистора с индуцированным каналом.

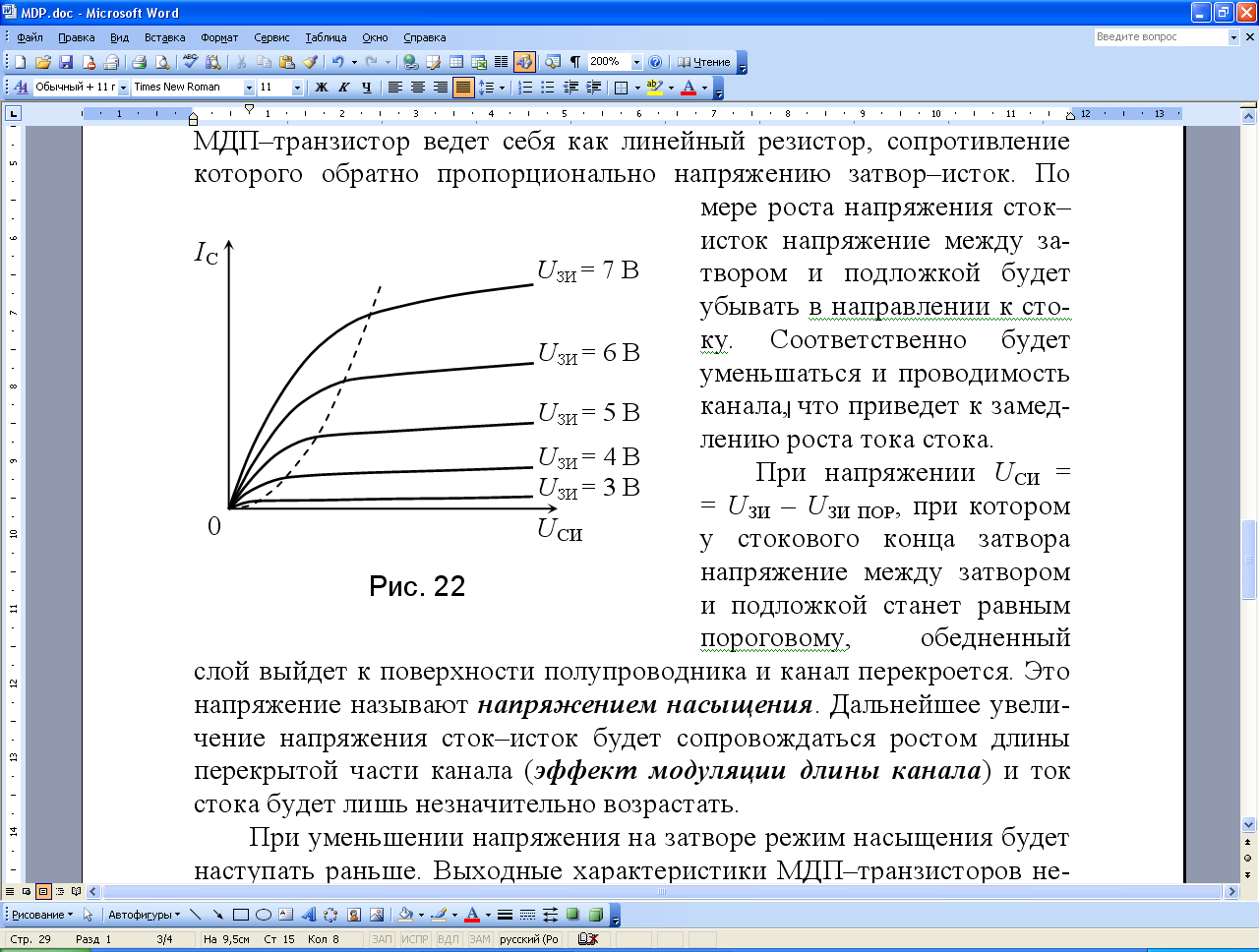

Рис. 1.26. Выходные характеристики МДП транзистора с индуцированным каналом

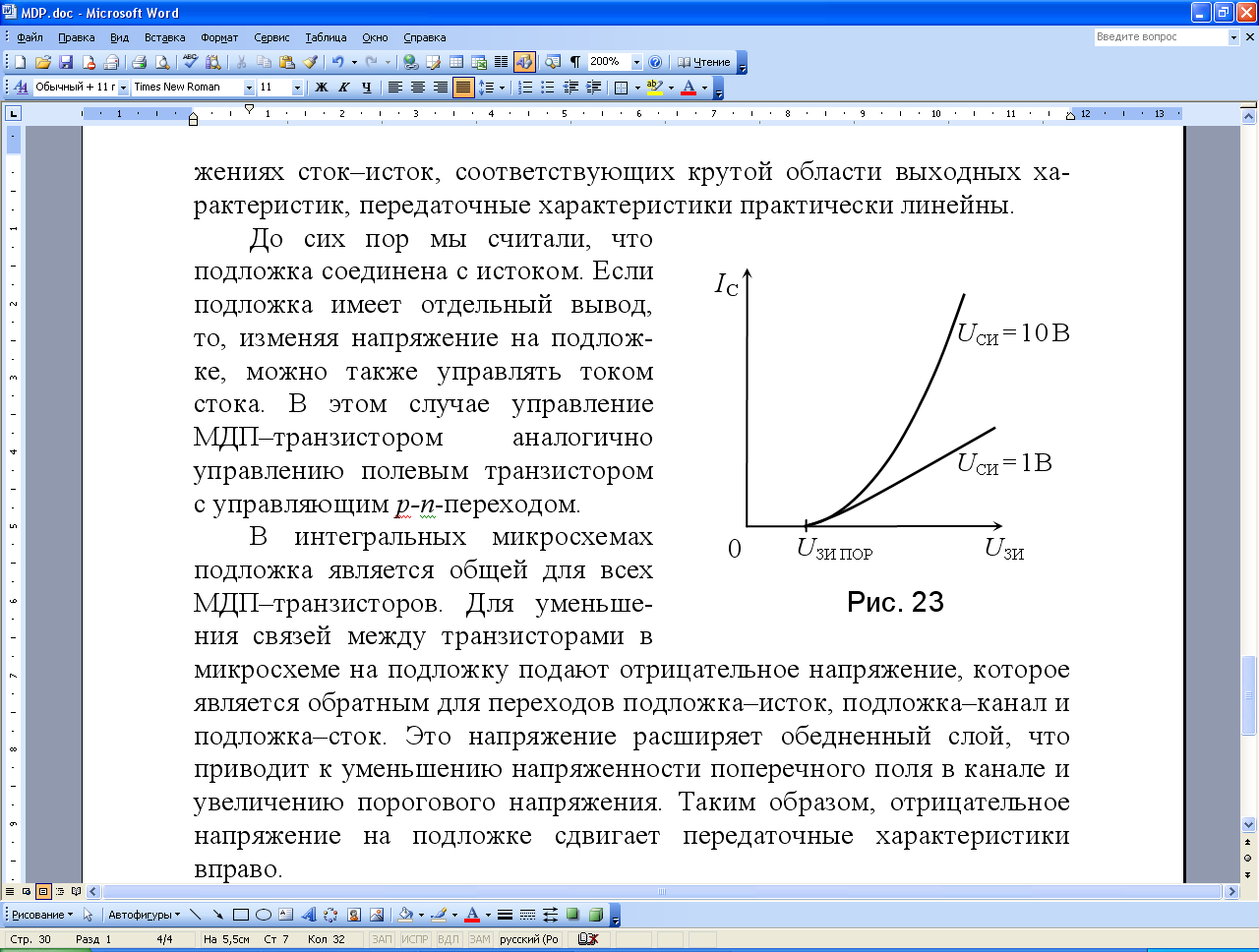

Рис. 1.27. Придаточная характеристика МДП транзистора и индуцированным каналом.

2. Основные понятия алгебры логики

Таблица 2.1

|

Аргументы |

Функция | |

|

Имеются деньги |

Необходимость есть |

Приобрести компьютер |

|

0 |

0 |

0 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

1 |

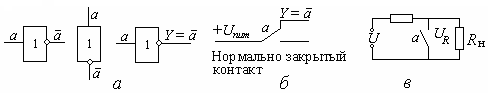

Рис. 2.1. Условное графическое обозначение (а) и релейно-контактная реализация логического элемента НЕ (б) и (в).

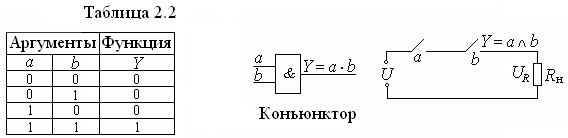

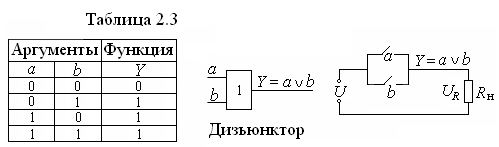

Рис. 2.2. Таблица истинности, условное обозначение и релейно-контактная реализация логического элемента И.

Рис. 2.3. Таблица истинности, условное обозначение и релейноконтактная реализация логического элемента ИЛИ.

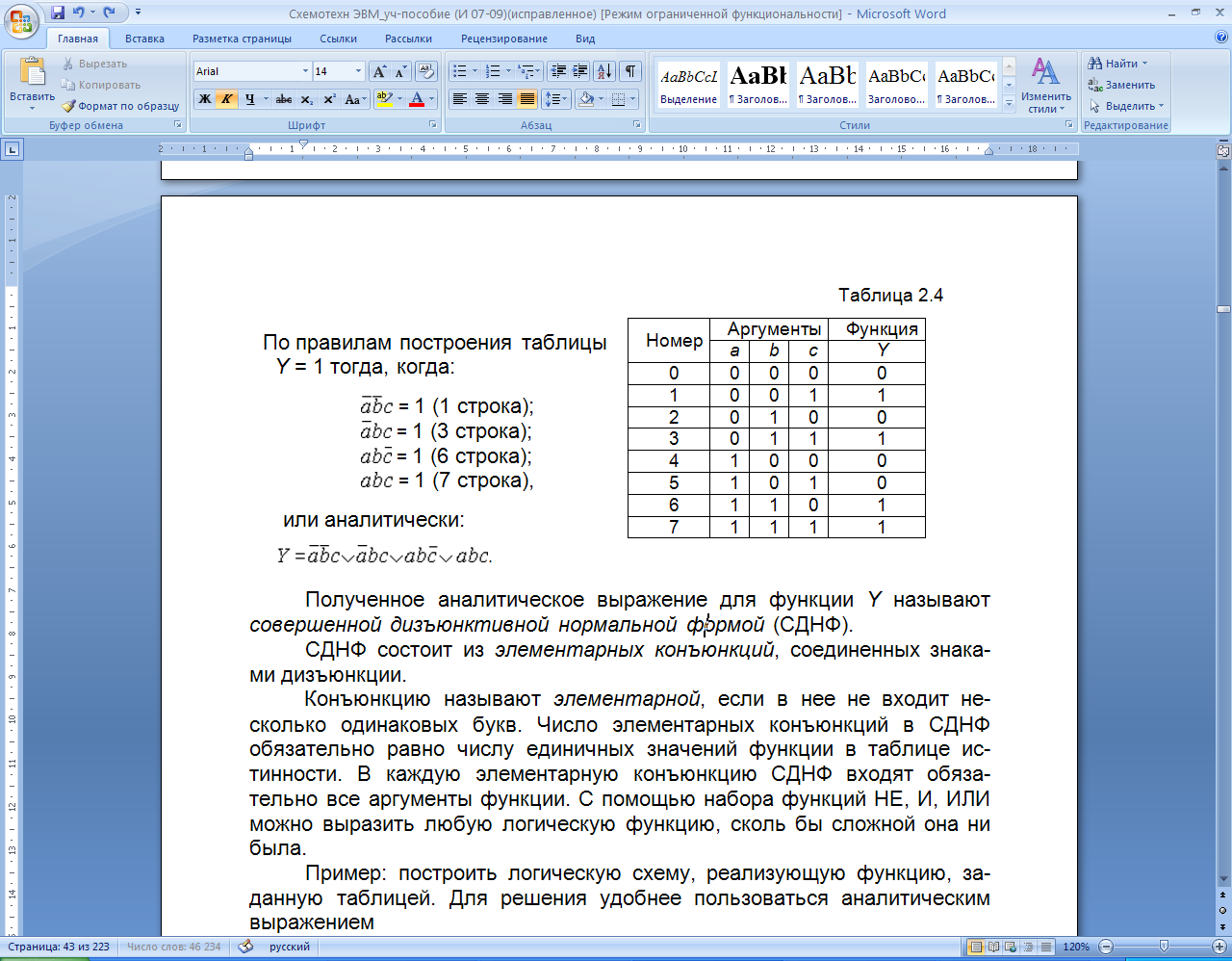

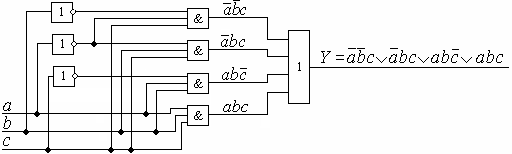

Рис. 2.4. Логическая схема, реализованная по СДНФ.

Рис. 2.5. Сокращенное условное изображение схемы по рис. 2.4

|

Аксиомы операций | ||

|

конъюнкции |

и |

дизъюнкции |

|

0 · 0 = 0 |

|

1 1 = 1 |

|

1 · 0 = 0 · 1 = 0 |

|

0 1 = 1 0 = 1 |

|

1 · 1 = 1 |

|

0 0 = 0 |

Законы булевой алгебры

|

|

Для конъюнкции |

Для дизъюнкции |

|

1. Переместительный закон: |

|

|

|

2. Закон повторения (тавтологии): |

|

|

|

3. Закон нулевого множества: |

|

|

|

4. Закон универсального множества: |

|

|

|

5. Закон дополнительности: |

|

|

|

6. Закон поглощения: |

|

|

|

7. Закон склеивания: |

|

|

|

8. Закон инверсии (закон де Моргана): |

|

|

|

или после инвертирования правых и левых частей: |

|

|

|

9.

Закон обращения: если

| ||

|

10.

Закон двойной инверсии:

| ||

|

11.

Сочетательный закон: | ||

|

12. Распределительный закон:

| ||

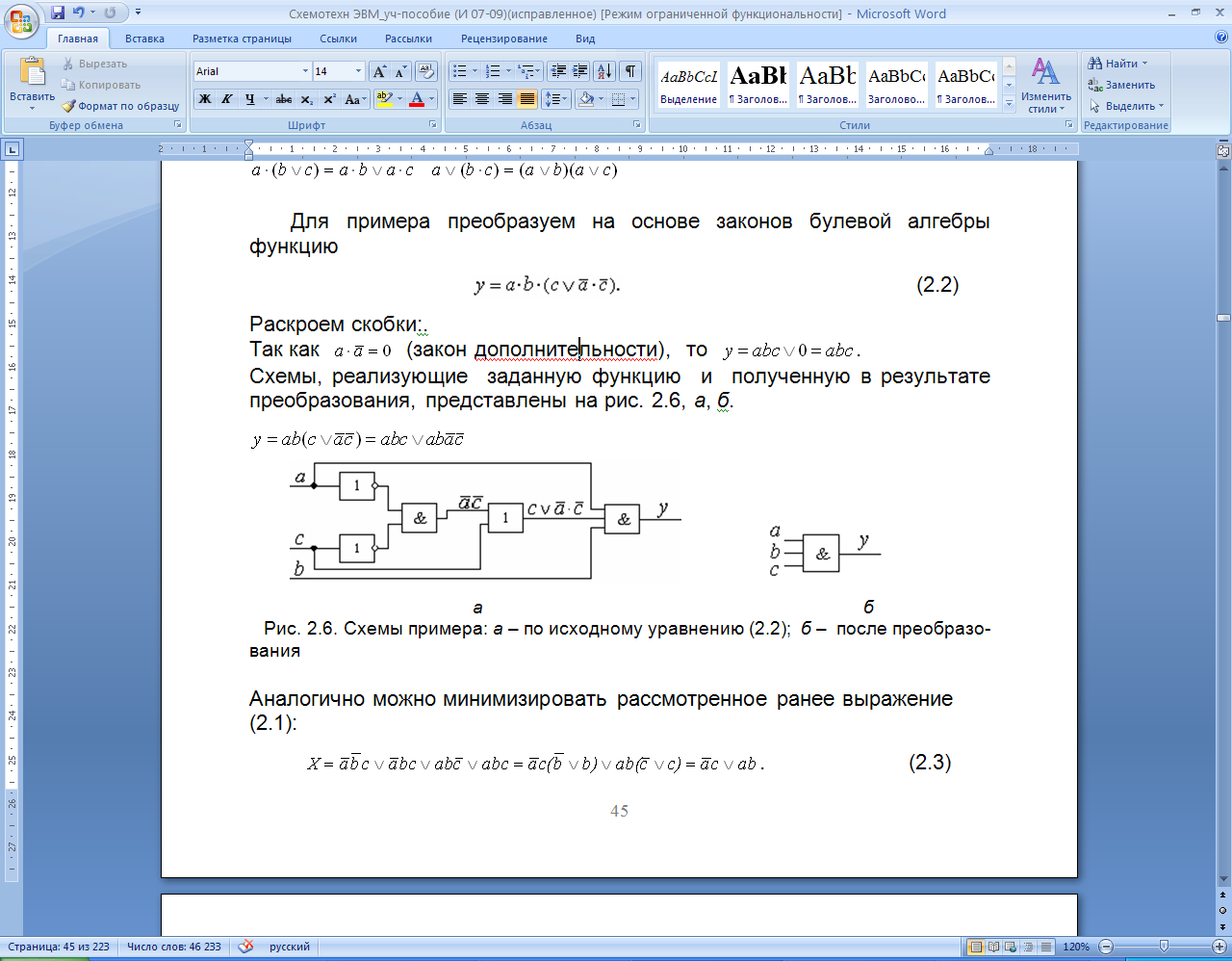

Рис. 2.6. Схемы примера: а по исходному уравнению; б после преобразования

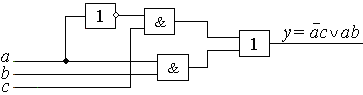

Рис. 2.7. Схема, полученная в результате минимизации уравнения (2.1)

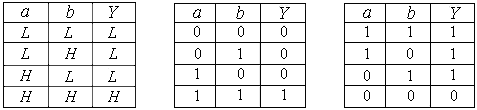

|

Таблица 2.5 |

Таблица 2.6 |

Таблица 2.7 |

|

Уровни сигналов |

Логические сигналы |

Логические сигналы |

в положительной логике в отрицательной логике

Положительная логика Отрицательная логика

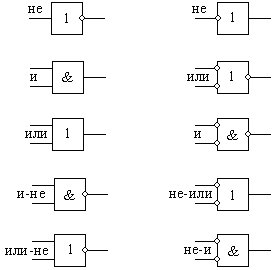

Рис. 2.8. Графическое обозначение элементов в двух видах логик

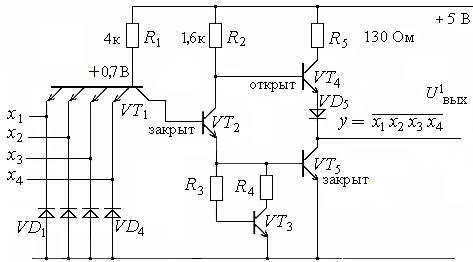

3. Цифровые интегральные микросхемы

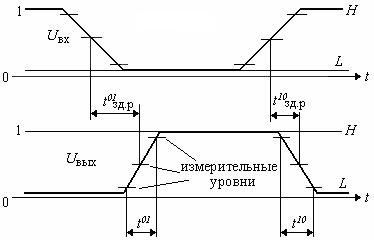

Рис. 3.1. Реакция инвертирующего логического элемента на изменение входного сигнала

Рис. 3.2. Оценка времени задержки: а – схема цепи, б – переходный процесс

а б

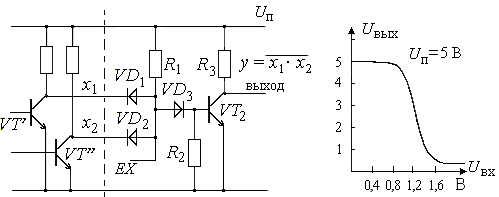

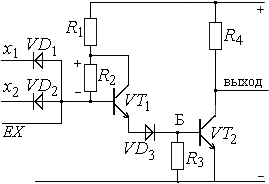

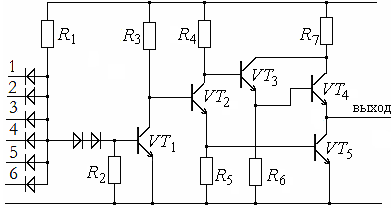

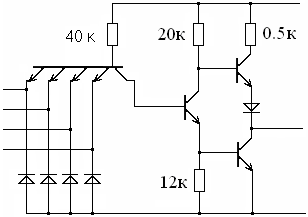

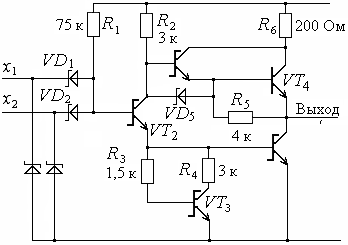

Рис. 3.3. Пример ДТЛ: а – схема, б – проходная характеристика

Рис. 3.4. Элемент ДТЛ с усовершенствованной входной цепью

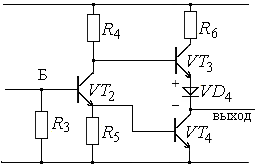

Рис. 3.5. Элемент ДТЛ с улучшенным выходным каскадом

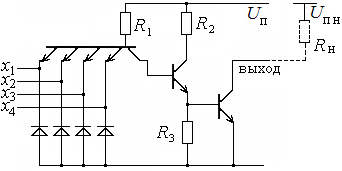

Рис. 3.6. Шестивходовый элемент И ДТЛ

Рис. 3.7. Базовый элемент высокопороговой логики

|

Таблица 3.1 | ||||||

|

Группы микросхем |

Номер серии |

Время задержки распространения на 1 элемент (нс) |

Потребляемая мощность (мВт) | |||

|

Универсальная (стандартная) |

133, К155 |

18 |

10 | |||

|

Быстродействующая |

130, К131 |

12 |

23 | |||

|

Микромощная |

134, КР134 |

66 |

1 | |||

|

На транзисторах Шотки |

530, К531 |

6 |

19 | |||

|

На транзисторах Шотки маломощная |

533, К555 |

19 |

2 | |||

|

FAST |

КР1531 |

3 |

4 | |||

|

ALS

|

КР1533

|

4

|

1,2

| |||

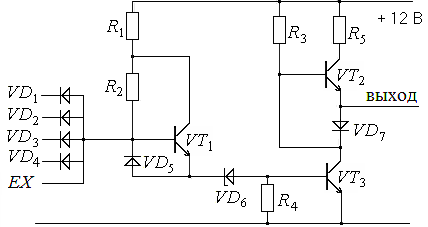

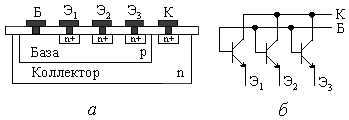

Рис. 3.8. Многоэмиттерный транзистор: а – физическая структура;

б – схема замещения

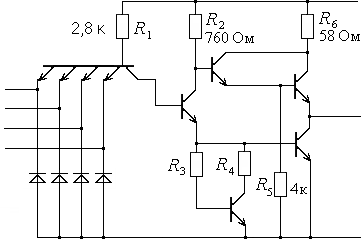

Рис. 3.9. Принципиальная схема базового элемента 155 (133) серии

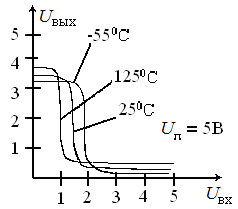

Рис. 3.10. Передаточная характеристика

Рис. 3.11. Эквивалентная схема микросхемы ТТЛ

а б

Рис. 3.12. Распределение токов во входной цепи элемента И–НЕ:

а – на вход подана логическая 1; б – на вход подан логический 0

Рис. 3.13. Включение резистора на входе микросхемы

Рис. 3.14. Схема базового элемента микромощных серий

Рис. 3.15. Базовый элемент микросхем ТТЛ повышенного быстродействия

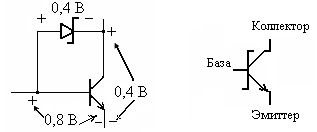

Рис. 3.16. Диод Шотки: а – структура диода; б – условное обозначение

а б

Рис. 3.17. Транзистор Шотки: а – структура транзистора; б – условное обозначение

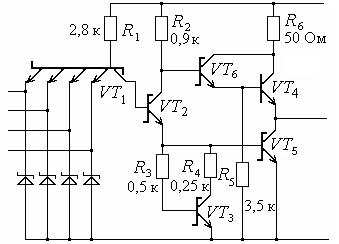

Рис. 3.18. Схема базового элемента ТТЛШ

Рис. 3.19. Схема маломощного базового элемента ТТЛШ

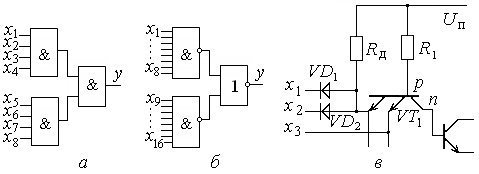

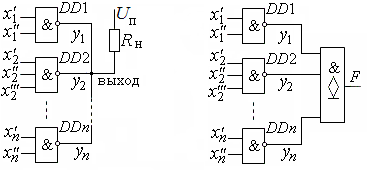

Рис. 3.20. Увеличение числа входов:

а – с помощью нескольких микросхем И; б – микросхем И–НЕ и ИЛИ–НЕ;

в– подключением внешнего диода и резистора

Рис. 3.21. Элемент И–ИЛИ–НЕ с возможностью расширения по ИЛИ:

а – принципиальная схема;

б – условное графическое обозначение схемы с расширением по ИЛИ

Рис. 3.22. Микросхема 155ЛР3

Рис. 3.23. Схема расширителя 155ЛД1

а б в

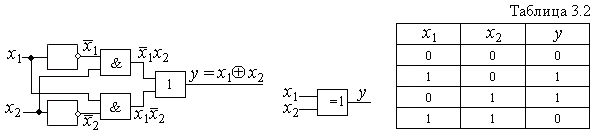

Рис. 3.24. Исключающее ИЛИ: а – структурная схема;

б – условное графическое обозначение; в – таблица истинности

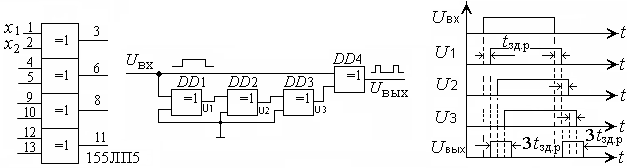

а б в

Рис. 3.25. Микросхема сумматора по модулю 2: а – условное обозначение;

б – пример применения; в – временная диаграмма

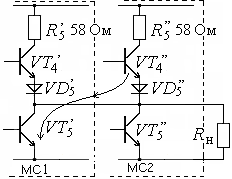

Рис. 3.26. Схема соединения выходов двух микросхем на общую нагрузку

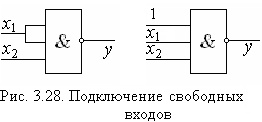

Рис. 3.27 Подключение входов неиспользуемых логических элементов

Рис. 3.28 Подключение свободных входов

Таблица 3.3

|

Серии нагружаемых микросхем |

Число входов подключаемых микросхем серий | ||||

|

155,133 |

130,131 |

134,734 |

530,531 |

533,535 | |

|

Универсальные (133,155) |

10 |

8 |

40 |

8 |

20 |

|

Быстродействующие 130,131 |

12 |

10 |

50 |

10 |

25 |

|

Микромощные 134,734 |

2 |

1 |

20 |

1 |

10 |

|

С транзист. Шотки 530, 531 |

12 |

10 |

100 |

10 |

50 |

|

Маломощн. Шотки 533,535 |

5 |

4 |

40 |

4 |

20 |

Рис. 3.29. Логический элемент с открытым коллектором

а б

Рис. 3.30. Псевдомонтажное И: а – схема соединения; б – условное обозначение

а б

Рис. 3.31. Микросхема с тремя состояниями: а – электрическая схема;

б – условное графическое обозначение

Рис. 3.32. Второй вариант перевода схемы в третье состояние

Рис. 3.33. Вариант схемы с тремя состояниями

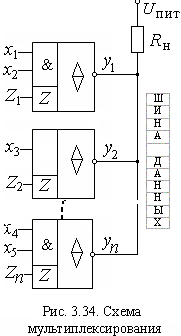

Рис. 3.34 Схема мультиплексирования

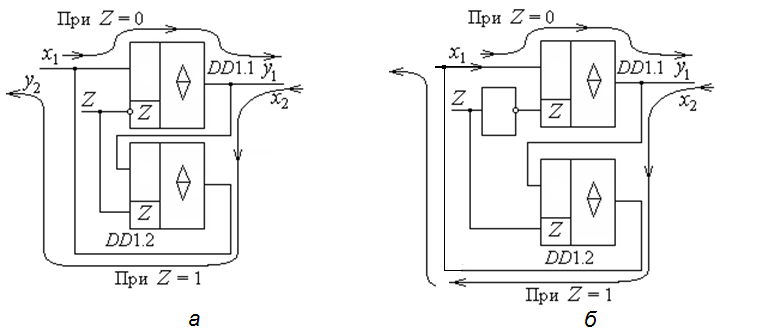

а б

Рис. 3.35. Функциональная схема двунаправленного шинного усилителя:

а – передача сигнала по одной линии в обоих направлениях; б – при передаче справа налево – выход на другую линию

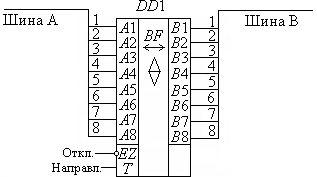

Рис. 3.36. Включение двунаправленного буфера