- •2. Основные понятия алгебры логики

- •3. Цифровые интегральные микросхемы

- •4. Логические элементы на кмоп-транзисторах

- •5. Схемотехника интегральных схем инжекционной логики и эсл

- •6. Триггеры

- •7. Счетчики

- •8. Регистры

- •9. Мультиплексоры и демультиплексоры

- •10. Шифраторы и дешифраторы

- •11. Арифметические устройства

- •12. Импульсные устройства на имс

- •13. Запоминающие устройства

- •14. Аналого-цифровые и цифро-аналоговые преобразователи

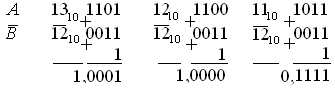

11. Арифметические устройства

Рис. 11.1 Условное обозначение (а, б) и схема реализации четвертьсумматора (в)

Таблица 11.1

-

A

B

S

0

0

0

0

1

1

1

0

1

1

1

0

Таблица 11.2

-

A

B

P

S

0

0

0

0

0

1

0

1

1

0

0

1

1

1

1

0

Рис. 11.2. Условное обозначение (а) и схема реализации полусумматора (б)

Рис. 11.3. Условное обозначение полного одноразрядного сумматора

Таблица 11.3

|

Номер |

a |

b |

p |

P |

S |

|

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

0 |

1 |

|

2 |

0 |

1 |

0 |

0 |

1 |

|

3 |

0 |

1 |

1 |

1 |

0 |

|

4 |

1 |

0 |

0 |

0 |

1 |

|

5 |

1 |

0 |

1 |

1 |

0 |

|

6 |

1 |

1 |

0 |

1 |

0 |

|

7 |

1 |

1 |

1 |

1 |

1 |

![]()

![]()

Рис. 11.4. Схема одноразрядного полного сумматора на полусумматорах

а б

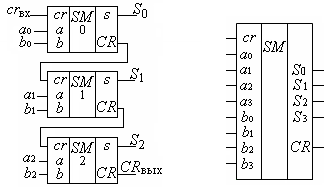

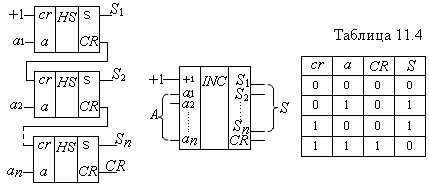

Рис. 11.5. Структурная схема (а) и условное обозначение сумматора (б)

а б в

Рис. 11.6. Структурная схема (а), условное обозначение (б)

и таблица истинности инкрементора (в)

Таблица 11.5

|

Уменьшаемое |

Вычитаемое |

Разность |

Заем | |

|

0 |

0 |

0 |

0 | |

|

0 |

1 |

1 |

1 | |

|

1 |

0 |

1 |

0 | |

|

1 |

1 |

0 |

0 | |

Рис. 11.7. Структура полусубтрактора

Компаратор аналоговых сигналов

Рис. 11.8. Условное обозначение операционного усилителя

Рис. 11.9. Структурная схема и характеристика нуль-органа

Рис. 11.10. Односторонний нуль – орган

Рис. 11.11. Схема сравнения одноразрядных чисел

Рис. 11.12. Схема определения неравенства двухразрядных чисел

Рис. 11.13. Схема сравнения многоразрядных чисел

Рис. 11.14. Условное графическое обозначение микросхемы 555СП1

Таблица 11.6

-

№

п.п.

Сравниваемые данные

Входы наращивания каскадов

Выходы

а3, b3

а2, b2

а1, b1

а0, b0

A>B

A<B

A=B

A>B

A<B

A=B

1

а3>b3

X

X

X

X

X

X

B

H

H

2

а3<b3

X

X

X

X

X

X

H

B

H

3

а3=b3

а2>b2

X

X

X

X

X

B

H

H

4

а3=b3

а2<b2

X

X

X

X

X

H

B

H

5

``

а2=b2

а1>b1

X

X

X

X

B

H

H

6

``

а2=b2

а1<b1

X

X

X

X

H

B

H

7

``

``

а1=b1

а0>b0

X

X

X

B

H

H

8

``

``

а1=b1

а0<b0

X

X

X

H

B

H

9

``

``

``

а0=b0

B

H

H

B

H

H

10

``

``

``

а0=b0

H

B

H

H

B

H

11

``

``

``

``

H

H

B

H

H

B

12

``

``

``

``

X

X

B

H

H

B

13

``

``

``

``

B

B

H

H

H

H

14

``

``

``

``

H

H

H

B

B

B

Рис. 11.15. Последовательная схема объединения компараторов

Рис. 11.16. Параллельная схема увеличения разрядности для оценки равенства чисел

А > В А = В А < В

Рис. 11.17. Схема компаратора на базе сумматора

Рис. 11.18. Обобщенная структура АЛУ

Рис 11.19. Условное обозначение АЛУ К155ИП3

Таблица 11.7

-

Состояние входов

Состояние выхода С4

С0

А и В

Н

А < B

H

L

A < B

H

H

A > B

L

L

A > B

L

Рис. 11.20. Увеличение разрядности АЛУ применением блока ускоренного переноса К155ИП4