- •2. Основные понятия алгебры логики

- •3. Цифровые интегральные микросхемы

- •4. Логические элементы на кмоп-транзисторах

- •5. Схемотехника интегральных схем инжекционной логики и эсл

- •6. Триггеры

- •7. Счетчики

- •8. Регистры

- •9. Мультиплексоры и демультиплексоры

- •10. Шифраторы и дешифраторы

- •11. Арифметические устройства

- •12. Импульсные устройства на имс

- •13. Запоминающие устройства

- •14. Аналого-цифровые и цифро-аналоговые преобразователи

4. Логические элементы на кмоп-транзисторах

Рис. 4.1. Поперечное сечение p-канального полевого транзистора

а б

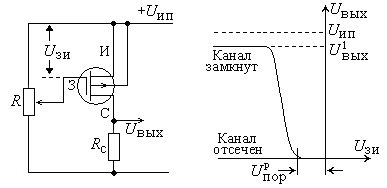

Рис. 4.2. Схема для снятия передаточной характеристики (а)

и характеристика р-канального транзистора (б)

Рис. 4.3. Схема включения п-канального полевого транзистора (а)

и его передаточная характеристика (б)

а б

Рис. 4.4. Схема для снятия передаточной характеристики (а)

и характеристика инвертора (б)

Рис. 4.5. Полная схема инвертора с защитными цепями

Рис. 4.6. Принципиальная схема инвертора КМОП с буферными каскадами

а б в

Рис. 4.7. Логический элемент И–НЕ КМОП:

а – принципиальная схема; б – таблица истинности; в – условное обозначение

а б в

Рис. 4.8. Логический элемент ИЛИ–НЕ КМОП:

а – принципиальная схема; б – таблица истинности; в – условное обозначение

а б в

Рис. 4.9. Инвертор КМОП с тремя состояниями:

а – принципиальная схема; б – таблица истинности; в – условное обозначение

5. Схемотехника интегральных схем инжекционной логики и эсл

Рис. 5.1. Схемы элементов с непосредственными связями

Рис. 5.2. Подключение двух нагрузок к общему выходу

Рис. 5.3. Схема выделения базового элемента ИИЛ

а б

Рис. 5.4. Схема инвертора инжекционной логики:

а – задание режима; б – типовая схема инвертора

а б

Рис. 5.5. Логические элементы логики И2Л:

а – упрощенная схема инвертора; б – логический элемент И–НЕ с диодами Шотки

а б

Рис. 5.6. Базовые элементы ЭСЛ:

а – переключатель тока; б – простейший одновходовый элемент ЭСЛ

Рис. 5.7. Элемент ЭСЛ с эмиттерными повторителями

Рис. 5.8. Элемент ЭСЛ с несколькими входами и с простейшим

источником порогового напряжения

Рис. 5.9. Схема логического элемента ЭСЛ 500-й серии

Рис. 5.10. Схема элемента Э2СЛ

6. Триггеры

а б

Рис. 6.1. Триггер на логических элементах ИЛИ–НЕ:

а – принципиальная схема; б – условное графическое обозначение

|

Таблица 6.1 | |||||

|

S |

R |

Qt |

|

Qt+1 |

|

|

0 |

1 |

0 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

1 |

0 |

|

0 |

0 |

0 |

1 |

0 |

1 |

|

1 |

1 |

0 |

1 |

* |

* |

|

0 |

1 |

1 |

0 |

0 |

1 |

|

1 |

0 |

1 |

0 |

1 |

0 |

|

0 |

0 |

1 |

0 |

1 |

0 |

|

1 |

1 |

1 |

0 |

* |

* |

|

Таблица 6.2 | ||

|

|

Tакт tn |

Tакт tn+1 |

|

Rn |

Sn |

Qn+1 |

|

0 |

0 |

Qn |

|

0 |

1 |

1 |

|

1 |

0 |

0 |

|

1 |

1 |

* |

Рис. 6.2. Временные диаграммы триггера

а б

Рис. 6.3. Триггер на логических элементах И–НЕ:

а – принципиальная схема;

б – условное графическое обозначение

|

Таблица 6.3 | |||||

|

|

|

Qt |

|

Qt+1 |

|

|

0 |

1 |

0 |

1 |

1 |

0 |

|

1 |

0 |

0 |

1 |

0 |

1 |

|

0 |

0 |

0 |

1 |

* |

* |

|

1 |

1 |

0 |

1 |

0 |

1 |

|

0 |

1 |

1 |

0 |

1 |

0 |

|

1 |

0 |

1 |

0 |

0 |

1 |

|

0 |

0 |

1 |

0 |

* |

* |

|

1 |

1 |

1 |

0 |

1 |

0 |

|

Таблица 6.4 | ||

|

Sn |

Rn |

Qn+1 |

|

0 |

0 |

* |

|

0 |

1 |

1 |

|

1 |

0 |

0 |

|

1 |

1 |

Qn |

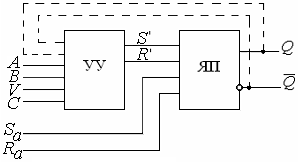

Рис. 6.4. Триггерная система

а б

Рис. 6.5 Синхронный (тактируемый) RS-триггер:

а – принципиальная схема; б – условное графическое обозначение

|

Таблица 6.5 | |||

|

Такт n |

Такт n+1 | ||

|

С |

Rn |

Sn |

Qn+1 |

|

0 |

0 |

0 |

Qn |

|

0 |

1 |

0 |

Qn |

|

0 |

0 |

1 |

Qn |

|

0 |

1 |

1 |

Qn |

|

1 |

0 |

0 |

Qn |

|

1 |

1 |

0 |

0 |

|

1 |

0 |

1 |

1 |

|

1 |

1 |

1 |

* |

а б

Рис. 6.7. Тактируемый D-триггер:

а – принципиальная схема; б – условное графическое обозначение

|

Таблица 6.6 | ||

|

D |

Qn |

Qn+1 |

|

0 |

0 |

0 |

|

0 |

1 |

0 |

|

1 |

0 |

1 |

|

1 |

1 |

1 |

Рис. 6.8. Диаграмма работы D-триггера

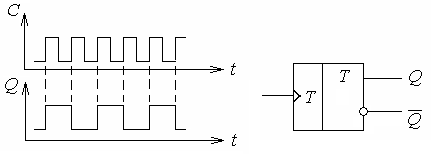

а б

Рис. 6.8. Временная диаграмма (а) и условное обозначение счетного триггера (б)

а б

Рис. 6.9. Схемы счетного триггера на базе D-триггера (а) и RS-триггера (б)

Рис. 6.10. Счетный триггер с преобразованием входного сигнала в импульс и с задержкой в цепи обратной связи

Таблица 6.7

а б

Рис. 6.11. Таблица состояний TV-триггера (а) и его условное обозначение (б)

Рис. 6.12. Схема MS-триггера

Рис. 6.13. Временная диаграмма работы MS-триггера

|

Таблица 6.8 | ||

|

Такт n |

Такт n+1 | |

|

Jn |

Kn |

Qn+1 |

|

0 |

0 |

Qn |

|

0 |

1 |

0 |

|

1 |

0 |

1 |

|

1 |

1 |

|

Рис. 6.14. Структура JK-триггера с элементами временной задержки

Рис. 6.15. Двухступенчатый JK-триггер с инвертором в цепи синхронизации

Рис. 6.16. Временная диаграмма работы JK-триггера в счетном режиме

|

Таблица 6.9 | |||||

|

Режим |

Входы |

Выходы | |||

|

С |

J |

K |

Q |

| |

|

Хранения |

|

0 |

0 |

Q |

|

|

Сброс |

` ë |

0 |

1 |

0 |

1 |

|

Установка |

` ë |

1 |

0 |

1 |

0 |

|

Счетный |

` ë |

1 |

1 |

|

Q |

Рис. 6.17 Условное обозначение JK-триггера K155TB1

Рис. 6.18 Внутренняя структура JK-триггера K155TB1