- •13.1. Классификация микропроцессоров и особенности их использования в цифровой аппаратуре.

- •13.2. Типовые структуры микропроцессорных систем.

- •13.3. Принцип программного управления в микропроцессорной системе.

- •13.4. Организация ввода-вывода в микропроцессорной системе.

- •13.5. Интерфейсы микропроцессорных систем.

- •13.5.1. Интерфейс rs-232.

- •13.5.2. Интерфейс usb.

- •13.5.3. Интерфейс i2c.

- •13.5.4. Интерфейс spi.

- •13.6. Управляющие сигналы типового микропроцессора.

- •13.7. Структура типового микропроцессора.

- •13.8. Способы адресации данных.

- •13.9. Типовая система команд микропроцессора.

- •13.9.1. Команды пересылки данных.

- •13.9.2. Команды выполнения арифметических операций.

- •13.9.3. Команды выполнения логических операций.

- •13.9.4. Команды передачи управления.

- •13.9.5. Команды специальные.

13.7. Структура типового микропроцессора.

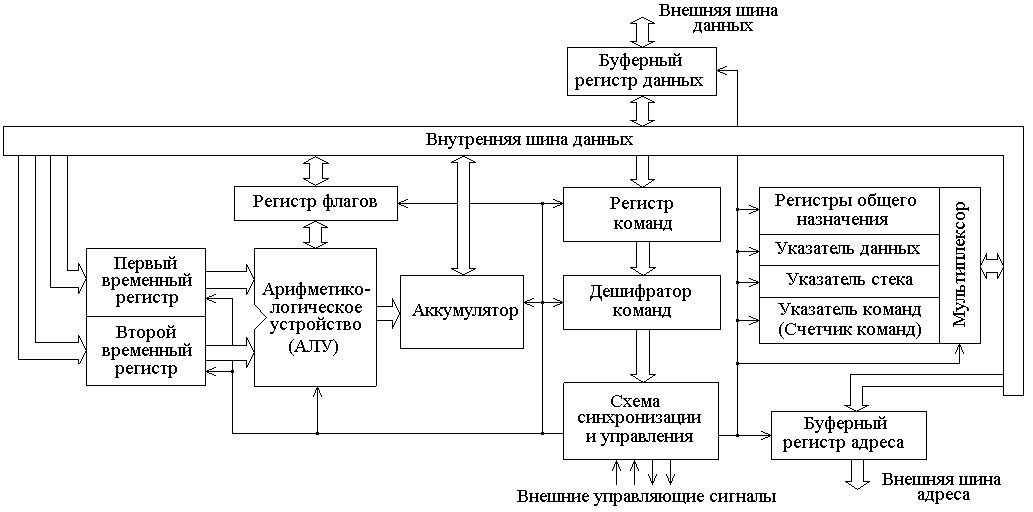

Микропроцессоры с момента своего появления интенсивно совершенствуются. Главные изменения касаются важнейшей составляющей архитектуры, а именно их структуры. Появляются возможности параллельных вычислений в следствии организации конвейерной и многопотоковой обработки, увеличения количества микропроцессорных ядер в кристалле, реализации принципов Гарвардской модели памяти и пр. Поэтому изобразить структуру микропроцессора, отражающую все новейшие достижения в области микропроцессорной техники, в силу сложности, в рамках данного учебника не представляется возможным. Приведем пример типовой структуры, отражающей общие принципы построения CISC-микропроцессора Фон-Неймановской организации и позволяющей понять общие принципы функционирования микропроцессора (рис.13.11).

Рис.13.11. Структурная схема типового микропроцессора Фон-Неймановского типа.

В приведенной на рисунке структуре микропроцессора использован магистральный принцип организации связи между узлами, заключающийся в том, что все узлы микропроцессора работают поочередно на общую внутреннюю шину данных. Обмен информацией между внутренней шиной данных и внешней шиной данных осуществляется через двунаправленный буферный регистр данных. Буферный регистр адреса фиксирует адреса активизируемых внешних устройств на внешней шине адреса. Оба этих регистра являются трехстабильными, благодаря чему микропроцессор может быть отключен от внешних шин. Это может быть необходимо, например, при организации ввода-вывода в режиме прямого доступа к памяти или при организации многопроцессорной системы. Напомним, что шины данных и адреса в некоторых типах микропроцессоров могут быть мультиплексированы. Это значит, что одни и те же линии связи могут служить и для передачи данных, и для передачи адреса в различные моменты времени. В этом случае функции буферного регистра данных и буферного регистра адреса совмещаются в одном буферном регистре адреса/данных.

Основным операционным блоком является арифметико-логическое устройство (АЛУ), выполняющее арифметические и логические операции, а также операции сдвига. С АЛУ связан регистр, называемый аккумулятором. В большинстве универсальных микропроцессоров, особенно не высокой разрядности, аккумулятор используется для фиксации результата выполненного в АЛУ действия. Для многих восьмиразрядных микропроцессоров и микроконтроллеров так же характерно то, что аккумулятор используется и для фиксации одного из участвующих в операции операндов. Таким образом, один из операндов нужно занести предварительно в аккумулятор. В самой команде действия нужно указать источник второго операнда. Во время выполнения команды один операнд из аккумулятора запишется в первый временный регистр, освободив тем самым аккумулятор для результата, а второй – из источника, определенного командой, во второй временный регистр. АЛУ выполнит действие, предписанное командой, и результат разместится в аккумуляторе. Через аккумулятор для большинства микропроцессоров реализуется обмен информацией с внешними устройствами ввода-вывода.

Регистр флагов фиксирует признаки результата выполненной операции. Признак – это характеристика результата, формулируемая значением одного бита – «да» или «нет». Регистр флагов – это тот узел микропроцессора, который делает его «думающим», способным выбирать тот или иной путь в алгоритме решения задачи. Именно регистр флагов отличает микропроцессор от обычного калькулятора. С помощью регистра флагов становится возможным программировать условные операции. Содержимое этого регистра используется в тех случаях, когда выполнение операции ставится в зависимость от значений каких-либо признаков результата предыдущей операции. Типичным набором регистра флагов являются следующие флаги (признаки):

СF (carry flag) - перенос. Указанный разряд устанавливается в единицу, если в результате сложения двух двоичных чисел длиной в одно слово возникает перенос в старший разряд или в результате вычитания возникает заем из старшего разряда. В противном случае разряд признака переноса устанавливается в ноль. Этот признак используется, например, для организации выполнения арифметических операций с повышенной точностью, т.е. с числами длиной более одного слова;

АF (auxiliary flag) – вспомогательный перенос. Разряд этого признака устанавливается в единицу при наличии переноса из четвертого в пятый разряд результата или при заеме единицы из пятого разряда в четвертый. Этот признак позволяет реализовывать арифметику в двоично-десятичных кодах;

РF (parity flag) - четность. Разряд этого признака устанавливается в единицу, если в полученном коде результата общее число единиц является четным. В противном случае данный признак устанавливается в ноль. Этот признак используется при контроле данных на четность при формировании посылок по интерфейсам или при записи/чтении данных на внешние носители;

ZF (zero flag) – нулевой результат. При нулевом значении результата разряд этого признака устанавливается в единицу, при ненулевом - в ноль. Этот признак используется, например, для организации циклических структур;

SF (sign flag) – знак результата. Разряд этого признака дублирует содержимое старшего разряда результата. При выполнении арифметических операций в дополнительных кодах ноль в старшем знаковом разряде результата соответствует положительному числу, а единица – отрицательному;

OF (overflow flag) – переполнение. Разряд этого признака устанавливается в единицу при выходе знакового результата за границы диапазона.

Во многих моделях микропроцессоров регистр флагов содержит также разряды, указывающие на режим работы микропроцессора, разрешающие или запрещающие определенные режимы (например, флаг IF разрешения прерывания в микропроцессоре с архитектурой x86), указывающие на вид адресации и пр.

Регистры общего назначения (РОН) используются в микропроцессорах для хранения промежуточных данных в процессе обработки. РОН рассматриваются программистом как сверхоперативное запоминающее устройство, т.е. небольшой объем памяти, расположенный непосредственно на кристалле микросхемы микропроцессора. Для микроконтроллеров в качестве РОН обычно используются ячейки внутренней памяти данных с младшими адресами и с символическими обозначениями. Также можно отметить, что количество РОН в микроконтроллерах обычно значительно больше, чем в микропроцессорах. РОН характеризуются быстрым обращением к ним короткими командами. Поэтому в критических к быстродействию участках программы желательно в качестве хранилища промежуточных данных использовать именно РОН. Для микропроцессоров и микроконтроллеров небольшой разрядности отдельные РОН могут объединяться в группы, называемые регистровыми парами, а для микропроцессоров более высокой разрядности – наоборот разбиваться на однобайтовые составляющие.

Указатель команд или, как его еще называют, счетчик команд (program counter PC) представляет собой регистр, содержащий адрес ячейки памяти, в которой хранится подлежащая выполнению команда. Команды одной программы размещаются в последовательно расположенных ячейках памяти с соседними адресами. Поэтому для перехода к следующей команде содержимое счетчика команд автоматически инкрементируется на количество единиц, соответсвующее количеству занимаемых ею ячеек в памяти. При необходимости изменения естественного порядка следования команд в счетчик заносится адрес команды, к которой необходимо произвести переход. После перехода команды снова будут выполняться в естественном порядке.

Указатель стека (stak pointer SP) также как и счетчик команд представляет собой регистр, содержащий адрес, по которому осуществляется обращение к области памяти ОЗУ, называемой стеком. Стеком называется область оперативной памяти, ячейки которой заполняются последовательно друг за другом по принципу LIFO (Last Input First Output), т.е последний вошедший выходит первым. Стековые ячейки памяти имеют соседние адреса. Поэтому при обращении к стековым ячейкам памяти не нужно указывать адреса этих ячеек. Достаточно один раз в начале программы определить адрес первой ячейки стековой области. И в последствии отслеживать только последовательнойсть загрузки и выгрузки из стека. Адрес первой стековой ячейки заносится в указатель стека SP. Далее при записи или считывании каждого слова из стека указатель стека будет автоматически инкрементироваться или декрементироваться в зависимости от типа микропроцессора. Стековая адресация удобна тем, что команды обращения к стеку короткие и быстро извлекаются из памяти, а, следовательно, и быстро выполняются. В стек может отправляться на временное сохранение содержимое всех программно доступных регистров микропроцессора. Это может быть полезно при организации подпрограмм, когда содержимое этих регистров нужно временно сохранить в оперативной памяти, чтобы освободить сами регистры для выполнения подпрограммы. После того, как подпрограмма будет выполнена, все сохраненные в стеке данные на момент обращения к подпрограмме в обратном порядке будут извлечены из стека и восстановлены в своих первоначальных источниках.

Указатель данных используется для хранения адресов ячеек памяти, в которых хранятся обрабатываемые операнды. Указатель данных в этом случае является регистром-указателем адреса ячейки памяти. Микропроцессор читает содержимое этого регистра, рассматривает его содержимое как адрес ячейки памяти, по которому необходимо обратиться для чтения/записи операнда. Команды обращение к памяти через регистр-указатель данных также являются короткими и быстро исполняемыми.

Схема синхронгизации и управления служит для формирования внешних и внутренних управляющих сигналов всех узлов микропроцессора. Именно схема синхронизации и управления отвечает за последовательность действий микропроцессора по тактам при отработке каждой команды, т.е. определяет состав машинных циклов и циклов команды. Существуют микропроцессоры, в которых схема синхронизации и управления построена по принципу жесткой логики, и те, в которых эта схема представляет собой ПЛИС.

Выполнение любой команды начинается со считывания первого слова команды, которое содержит код операции, из памяти в регистр команд, где оно хранится в течение всего времени выполнения команды. Дешифрация кода операции производится в дешифраторе команд. По результатам работы дешифратора и под воздействием тактовых сигналов вырабатывается нужная последовательность управляющих сигналов схемой синхронизации и управления. Это приводит к считыванию из памяти остальных слов команды, если они имеются, а также к собственно выполнению операции, предписанной командой.