- •13.1. Классификация микропроцессоров и особенности их использования в цифровой аппаратуре.

- •13.2. Типовые структуры микропроцессорных систем.

- •13.3. Принцип программного управления в микропроцессорной системе.

- •13.4. Организация ввода-вывода в микропроцессорной системе.

- •13.5. Интерфейсы микропроцессорных систем.

- •13.5.1. Интерфейс rs-232.

- •13.5.2. Интерфейс usb.

- •13.5.3. Интерфейс i2c.

- •13.5.4. Интерфейс spi.

- •13.6. Управляющие сигналы типового микропроцессора.

- •13.7. Структура типового микропроцессора.

- •13.8. Способы адресации данных.

- •13.9. Типовая система команд микропроцессора.

- •13.9.1. Команды пересылки данных.

- •13.9.2. Команды выполнения арифметических операций.

- •13.9.3. Команды выполнения логических операций.

- •13.9.4. Команды передачи управления.

- •13.9.5. Команды специальные.

13.5.4. Интерфейс spi.

Другим примером широко используемого в микропроцессорной технике интерфейса для стыковки микросхем является интерфейс SPI. Изначально этот интерфейс был придуман компанией Motorola, а в настоящее время используется в продукции многих производителей. Его наименование является аббревиатурой от «Serial Peripheral Bus», что отражает его предназначение - шина для подключения внешних устройств. Шина SPI организована по принципу «ведущий-ведомый». В качестве ведущего устройства обычно выступает микроконтроллер (или микропроцессор с контроллером указанного интерфейса в системе), но им также может быть ПЛИС или специализированная микросхема. Подключенные к ведущему шины внешние устройства являются ведомыми. В их роли выступают различного рода микросхемы, в т.ч. запоминающие устройства (ОЗУ, ПЗУ, ППЗУ, Flash-ROM), часы реального времени, АЦП или ЦАП и др.

Главным составным блоком интерфейса SPI является обычный регистр сдвига, сигналы синхронизации и ввода/вывода которого образуют интерфейсные сигналы. Протокол SPI является протоколом обмена данными между двумя сдвиговыми регистрами, каждый из которых одновременно выполняет и функцию приемника, и функцию передатчика. Непременным условием передачи данных по шине SPI является генерация сигнала синхронизации. Этот сигнал имеет право генерировать только ведущее устройство. От этого сигнала полностью зависит работа ведомого устройства.

Стандартом шины SPI определены четыре сигнала:

MOSI (от англ. Master Output Slave Input) – выходной сигнал передачи последовательных данных для ведущего устройства, входной сигнал приема последовательных данных для ведомого устройства;

MISO (от англ. Master Input Slave Output) - входной сигнал приема последовательных данных для ведущего устройства, выходной сигнал передачи последовательных данных для ведомого устройства;

SCLK (от англ. Select Clock) – выходной сигнал синхронизации для ведущего устройства и аналогичный входной сигнал для ведомого устройства;

![]() (от англ. Select

Slave)

– выходной сигнал выбора одного из

ведомых устройств для ведущего устройства,

входной сигнал активизации для ведомого

устройства.

(от англ. Select

Slave)

– выходной сигнал выбора одного из

ведомых устройств для ведущего устройства,

входной сигнал активизации для ведомого

устройства.

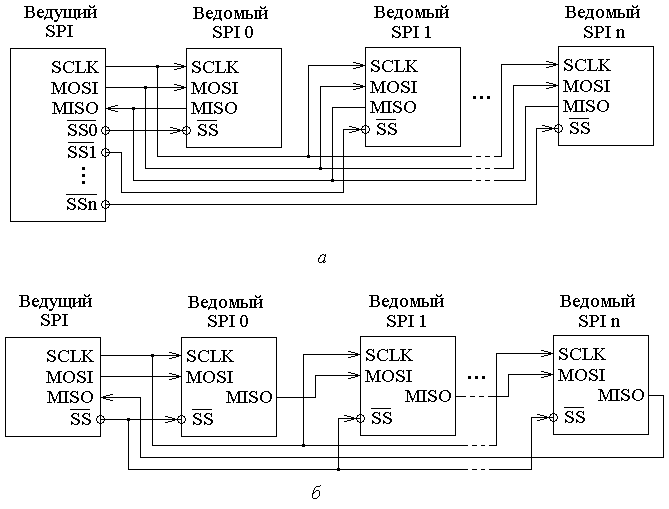

Существует

два типа подключения нескольких устройств

к шине SPI – параллельное и последовательное.

Параллельное подключение (рис. 13.9,а)

более распространено, т.к. позволяет

организовывать подключение любых

SPI-совместимых устройств. При таком

подключении все линии, кроме линии

сигнала выбора

![]() ,

соединены параллельно. Ведущее устройство

переводом того или иного сигнала

,

соединены параллельно. Ведущее устройство

переводом того или иного сигнала

![]() в низкое состояние задает, с каким

ведомым устройством оно будет обмениваться

данными. Главным недостатком такого

подключения является необходимость в

дополнительных линиях

в низкое состояние задает, с каким

ведомым устройством оно будет обмениваться

данными. Главным недостатком такого

подключения является необходимость в

дополнительных линиях

![]() для адресации нескольких ведомых

устройств, что существенно неудобно в

случае большого их количества.

для адресации нескольких ведомых

устройств, что существенно неудобно в

случае большого их количества.

Рис.13.9. Варианты одключения устройств по стандарту интерфейса SPI.

Самое

простое подключение, в котором участвуют

только два устройства – ведущее и

ведомое, требует всего одной линии

сигнала

![]() .

Ведущее устройство передает данные по

линии MOSI синхронно со сгенерированным

им же сигналом SCLK, а ведомое захватывает

переданные биты данных по определенным

фронтам принятого сигнала синхронизации.

Одновременно с этим ведущее устройство

отправляет свою посылку данных.

Представленную схему можно упростить

исключением одной из линий MISO или MOSI,

если в процессе передачи предполагается

только односторонняя связь. Одностороннюю

передачу данных можно встретить у таких

микросхем как ЦАП, АЦП, цифровые

потенциометры, программируемые усилители

и аналогичные по смыслу. Чтобы ведомое

устройство принимало и передавало

данные, помимо наличия сигнала

синхронизации необходимо также, чтобы

линия

.

Ведущее устройство передает данные по

линии MOSI синхронно со сгенерированным

им же сигналом SCLK, а ведомое захватывает

переданные биты данных по определенным

фронтам принятого сигнала синхронизации.

Одновременно с этим ведущее устройство

отправляет свою посылку данных.

Представленную схему можно упростить

исключением одной из линий MISO или MOSI,

если в процессе передачи предполагается

только односторонняя связь. Одностороннюю

передачу данных можно встретить у таких

микросхем как ЦАП, АЦП, цифровые

потенциометры, программируемые усилители

и аналогичные по смыслу. Чтобы ведомое

устройство принимало и передавало

данные, помимо наличия сигнала

синхронизации необходимо также, чтобы

линия

![]() была переведена в низкое состояние.

Когда используется только одно ведомое

устройство, может возникнуть соблазн

исключения и линии

была переведена в низкое состояние.

Когда используется только одно ведомое

устройство, может возникнуть соблазн

исключения и линии

![]() за счет жесткой установки низкого уровня

на входе выбора ведомого устройства.

Такое решение крайне нежелательно и

может привести к сбоям или вообще к

невозможности передачи данных, т.к. вход

выбора ведомого устройства служит для

перевода его в исходное состояние и

иногда инициирует вывод первого бита

данных.

за счет жесткой установки низкого уровня

на входе выбора ведомого устройства.

Такое решение крайне нежелательно и

может привести к сбоям или вообще к

невозможности передачи данных, т.к. вход

выбора ведомого устройства служит для

перевода его в исходное состояние и

иногда инициирует вывод первого бита

данных.

Каскадное

включение избавлено от недостатка

необходимости большого количества

линий

![]() в случае большого количества ведомых

устройств, т.к. при данном подключении

из нескольких микросхем образуется

один большой сдвиговый регистр. Для

этого выход передачи данных MISO

текущего ведомого устройства соединяется

с входом приема данных MOSI

последующего, как показано на рис.13.9,б.

Входы выбора

в случае большого количества ведомых

устройств, т.к. при данном подключении

из нескольких микросхем образуется

один большой сдвиговый регистр. Для

этого выход передачи данных MISO

текущего ведомого устройства соединяется

с входом приема данных MOSI

последующего, как показано на рис.13.9,б.

Входы выбора

![]() всех устройств соединяются параллельно

и, таким образом, общее число линий связи

сохраняется равным четырем. Однако

использование последовательного

подключения возможно только в том

случае, если оно обеспечивается

характеристиками всех ведомых устройств.

В технической документации на подключаемые

в шину устройства по последовательной

схеме должна стоять отметка «daisy-chaining».

всех устройств соединяются параллельно

и, таким образом, общее число линий связи

сохраняется равным четырем. Однако

использование последовательного

подключения возможно только в том

случае, если оно обеспечивается

характеристиками всех ведомых устройств.

В технической документации на подключаемые

в шину устройства по последовательной

схеме должна стоять отметка «daisy-chaining».

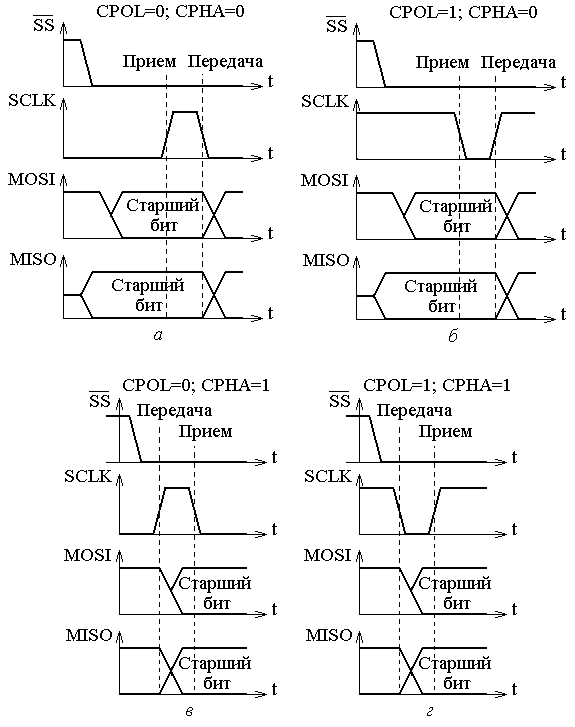

Протокол передачи по интерфейсу SPI отражает логику работы сдвигового регистра, которая заключается в выполнении операции сдвига и, соответственно, побитного ввода и вывода данных по определенным фронтам сигнала синхронизации. Установка данных при передаче и выборка при приеме всегда выполняются по противоположным фронтам импульсов синхронизации (рис.13.10).

Импульсы синхронизации SCLK могут иметь как положительную, так и отрицательную полярность. При этом передача или прием могут осуществляться как по переднему, так и по заднему его фронту. Таким образом, возможно четыре варианта логики работы интерфейса SPI. Эти варианты получили название режимов SPI и описываются двумя параметрами:

CPOL - исходный уровень сигнала синхронизации (если CPOL=0, то линия синхронизации до начала цикла передачи и после его окончания имеет низкий уровень, иначе, если CPOL=1, - высокий);

CPHA - фаза синхронизации (если CPHA=0, то по переднему фронту в цикле синхронизации будет выполняться прием данных, а затем, по заднему фронту, - передача данных; если же CPHA=1, то передача данных будет выполняться по переднему фронту в цикле синхронизации, а прием - по заднему).

Рис.13.10. Временная диаграмма протокола интерфейса SPI.

Ведущее и ведомое устройства, работающие в различных режимах SPI, являются несовместимыми. Поэтому необходимо обращать внимание на характеристики ведомых устройств при подключении их в шину. Аппаратные модули SPI, интегрированные в микроконтроллеры, в большинстве случаев поддерживают возможность выбора любого режима SPI. По аналогичному с протоколом SPI подключаются карты флэш-носителей SD и MMC форматов.