- •ВВЕДЕНИЕ

- •1. ЦЕЛИ, ЗАДАЧИ И СТРУКТУРА КУРСОВОГО ПРОЕКТИРОВАНИЯ

- •2. СОСТАВЛЕНИЕ ТЕХНИЧЕСКОГО ЗАДАНИЯ

- •2.1. Назначение и структура технического задания

- •2.2. Условия эксплуатации, классификация по условиям эксплуатации

- •2.2.1. Климатические факторы

- •2.2.2. Механические факторы

- •2.2.3. Радиационные факторы

- •2.2.4. Классы ЭПУ по условиям эксплуатации

- •2.2.5. Система классификации степеней защиты оболочки электрооборудования

- •2.2.6. Класс защиты от поражения электрическим током

- •2.3. Пример составления технического задания

- •3. СИНТЕЗ И РАСЧЕТ ФУНКЦИОНАЛЬНОЙ СХЕМЫ

- •3.1. Задачи синтеза и расчета функциональной схемы

- •3.2. Пример синтеза и расчета функциональной схемы

- •4. РАЗРАБОТКА ПРИНЦИПИАЛЬНОЙ СХЕМЫ

- •4.1. Порядок расчета принципиальной схемы

- •4.2. Выбор элементной базы и расчет электрической принципиальной схемы

- •4.2.1. Рекомендации по выбору конденсаторов

- •4.2.2. Особенности применения электролитических конденсаторов

- •4.2.2. Рекомендации по выбору резисторов

- •4.3. Особенности проектирования схем с микроконтроллерами

- •4.4. Повышение надежности за счет выбора щадящих режимов работы устройств

- •5. Проектирование печатной платы

- •5.1. Проектирование цепей заземления

- •5.3. Частотные характеристики пассивных компонентов

- •5.5. Паразитные эффекты печатной платы

- •5.6. Развязка сигналов

- •5.7. Общие рекомендации по проектированию печатных плат

- •ЗАЩИТА ПРОЕКТА

- •Приложение А

- •Приложение Б

- •Приложение В

17

3.СИНТЕЗ И РАСЧЕТ ФУНКЦИОНАЛЬНОЙ СХЕМЫ

3.1.Задачи синтеза и расчета функциональной схемы

Разработку устройства следует начинать с синтеза функциональной схемы. На основе проведенного литературного обзора и разработанного ТЗ необходимо определить метод реализации требуемых функций и принцип аппаратурной реализации. На основе этой информации разрабатывается функциональная схема. Процесс разработки функциональной схемы является итерационным, т.е. при разработке принципиальной схемы придется несколько раз возвращаться и вносить коррективы в исходную схему.

Рассмотрим более подробно понятие структурной и функциональной схемы.

Схемы электрические функциональные предназначены для пояснения определенных процессов, протекающих в изделии. Эти схемы используются при изучении принципов работы изделия, его настройке, регулировке, контроле (приемке) и ремонте. По сравнению со структурной схемой, функциональная схема более подробно раскрывает функции отдельных элементов и устройств. Графическое построение функциональной схемы должно давать наиболее наглядное представление о процессах, отображаемых на схеме. Обычно функциональные схемы используются совместно с принципиальными, поэтому перечень элементов для функциональной схемы обычно не разрабатывают. На функциональных схемах полезно указывать технические характеристики функциональных частей (например, коэффициент усиления усилителя, полосу и порядок фильтра и т.п.), помещать диаграммы и таблицы, параметры в характерных точках.

Схемы электрические структурные определяют основные части изделия, их назначения и служат для общего ознакомления с изделием. На структурной схеме раскрывается не принцип работы отдельных функциональных частей, а только взаимодействие между ними. Поэтому составные части изделия изображаются в виде прямоугольников различной формы, однако допускается также применять условные графические обозначения элементов. На линиях взаимосвязи стрелками указывают направление хода процессов, протекающих в изделии. На структурной схеме в виде таблицы обычно указываются наименования функциональных частей изделия. Кроме того, допускается на структурной схеме помещать поясняющие надписи, диаграммы, таблицы, а также указывать электрические параметры (токи, уровни напряжений) и формы сигналов в определенных точках схемы.

Особое внимание, как уже было сказано выше, следует обратить на проектирование функциональной схемы. Структурную схему достаточно просто построить на завершающем этапе проектирования. А функциональная схема является исходной при разработке принципиальной электрической схемы. Проектные решения, принимаемые на этапе разработки функциональной схемы, во многом определяют успех проектирования.

На этом этапе решаются такие вопросы как метод обработки сигнала (аналоговый, цифровой), аппаратурная реализация (дискретные элементы, микроконтроллер, ПЛИС и др.), организация внутрисхемных каналов передачи информации (последовательная шина, параллельная шина, стандарт шины, скорость передачи и др.).

Для получения полной исходной информации для начала разработки принципиальной схемы необходимо провести расчет основных блоков функциональной схемы, т.е. определить их внешние параметры.

3.2. Пример синтеза и расчета функциональной схемы

Для того что бы лучше понять задачи синтеза и расчета функциональной схемы рассмотрим пример. В качестве такого примера используем цифровой генератор синусоидального напряжения, техническое задание на проектирование которого было приведено в предыдущей главе.

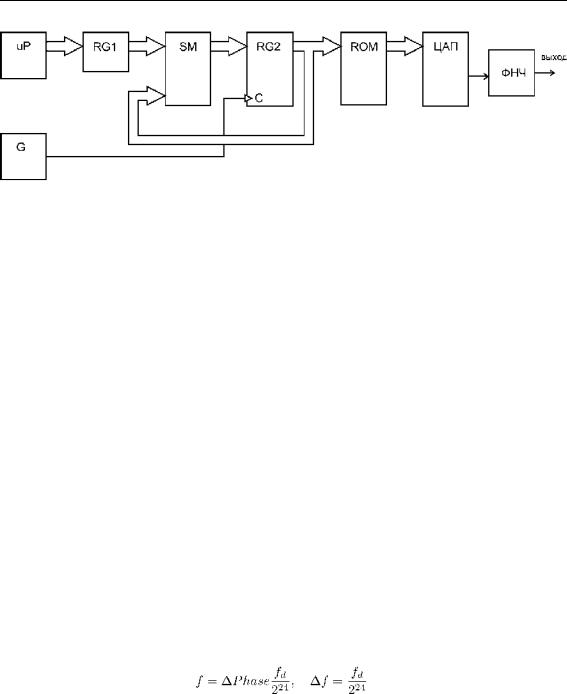

Предварительно рассмотрим метод формирования синусоидального напряжения. Функциональная схема метода показана на рисунке 3.1.

18

Рисунок 3.1. Функциональная схема метода генерации синусоиды

В отличие от метода прямого цифрового синтеза в этом методе сигнал подается на вход ЦАП мгновенные значения функции sin с постоянной частотой дискретизации. Непосредственное вычисление значений функции sin затруднено, так как закон, по которому она изменяется, нелинеен и непосредственно трудно реализуем. Намного проще вычислять мгновенные значения фазы (аргумент функции sin), которая изменяется линейно, а затем преобразовывать их в значения функции с помощью перекодировочной таблицы в ПЗУ (ROM). Поскольку фаза изменяется линейно, ее вычисление сводится к прибавлению в каждом такте некоторой добавки к текущему значению фазы. Величина приращения фазы определяет частоту сигнала:

,

,

где - частота дискретизации.

- частота дискретизации.

Схематически реализация этого метода показана на рисунке 3.1. Имеется регистр фазы RG2, содержимое которого в каждом такте увеличивается на величину приращения фазы. Величина приращения фазы хранится в регистре RG1, значение фазы записывается в регистр со схемы управления uP. В каждом такте к содержимому регистра RG2 с помощью сумматора SМ прибавляется содержимое регистра RG1. Таким образом, происходит линейное увеличение (накопление) мгновенной фазы. Увеличение фазы не может происходить бесконечно, так как любое реальное цифровое устройство имеет конечную разрядность и, соответственно, ограниченный диапазон представления чисел. Например, если накопитель фазы имеет разрядность 24 бита, то код фазы может принимать значения в диапазоне от 0 до 224 - 1. При формировании синусоидального сигнала имеет смысл вычислять фазу только в диапазоне от 0 до  . За пределами этого диапазона синусоида периодически повторяется. Поэтому диапазон изменения кода фазы от 0 до 224 - 1 поставлен в соответствие с диапазоном изменения фазы от 0 до

. За пределами этого диапазона синусоида периодически повторяется. Поэтому диапазон изменения кода фазы от 0 до 224 - 1 поставлен в соответствие с диапазоном изменения фазы от 0 до  . Тогда частота сигнала

. Тогда частота сигнала  и шаг ее пере-

и шаг ее пере-

стройки  соответственно равны:

соответственно равны:

,

где  .

.

Значение мгновенной фазы преобразуется в мгновенное значение синусоидального сигнала с помощью перекодировочной таблицы, хранящейся в ПЗУ. Код мгновенной фазы используется как адрес ROM, а выходной код ROM представляет собой мгновенное значение синусоидального сигнала. Этот код подается на вход ЦАП. Нет необходимости использовать все 24 бита мгновенного значения фазы, потому что в ошибке значений выходного сигнала доминирует составляющая ошибки квантования DAC. Максимальное требуемое число разрядов адреса ROM - это число разрядов примененного DAC плюс два. При дальнейшем увеличении объема РОМ качество сигнала

19

практически не улучшается. На выходе DAC формируется синусоидальный сигнал, который после низкочастотной фильтрации поступает на выход генератора.

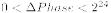

Первой задачей является выбор частоты дискретизации. В соответствии с теоремой Котельникова в проектируемом устройстве частота дискретизации  должна быть не менее 200 кГц (в соответствии с ТЗ максимальная частота генератора

должна быть не менее 200 кГц (в соответствии с ТЗ максимальная частота генератора  . Однако, выбор низкой частоты приведет к проблеме фильтрации выходного сигнала. На рисунке 3.2 приведен фрагмент низкочастотной области спектра сигнала на выходе ЦАП.

. Однако, выбор низкой частоты приведет к проблеме фильтрации выходного сигнала. На рисунке 3.2 приведен фрагмент низкочастотной области спектра сигнала на выходе ЦАП.

Рисунок 3.2. Спектр сигнала на выходе ЦАП.

Для обеспечения эффективного подавления гармоник  ,

,  и

и  необходимо отнести частоту

необходимо отнести частоту  как можно дальше от

как можно дальше от  . Однако слишком высокая частота

. Однако слишком высокая частота  потребует применение достаточно высокочастотных элементов и большой объем ПЗУ.

потребует применение достаточно высокочастотных элементов и большой объем ПЗУ.

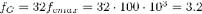

Зададимся кратностью частоты  , т. е. при максимальной частоте 100 кГц на один период синусоиды будет приходиться 32 отсчета. Теперь несложно вычислить частоту тактового генератора G (рисунок 3.1):

, т. е. при максимальной частоте 100 кГц на один период синусоиды будет приходиться 32 отсчета. Теперь несложно вычислить частоту тактового генератора G (рисунок 3.1):  МГц.

МГц.

Несложно посчитать, что объем ПЗУ при такой тактовой частоте должен составлять не менее 3.2 МБ. Однако, реализация такого объема памяти ПЗУ вызовет проблемы (как правило микросхемы PROM и EPROM имеют объем до 2 МБ). Снизим кратность частоты  , тогда

, тогда

МГц, а объем требуемой памяти для перекодировочной таблицы составит 2 МБ. Разрядность регистра фазы RG2 (рисунок 3.1)

МГц, а объем требуемой памяти для перекодировочной таблицы составит 2 МБ. Разрядность регистра фазы RG2 (рисунок 3.1)  (

( ).

).

Величину  в соответствии с МЭК 60027-2 ( ГОСТ 8.417-2002) правильно называть мебибайт, и обозначать MiB.

в соответствии с МЭК 60027-2 ( ГОСТ 8.417-2002) правильно называть мебибайт, и обозначать MiB.

Разрядность регистра приращения фазы RG1 определяется из условия  , наиболее близкое значение будет 10. Разрядность АЦП 16 бит, кроме того, АЦП должен биполярный выходной сигнал.

, наиболее близкое значение будет 10. Разрядность АЦП 16 бит, кроме того, АЦП должен биполярный выходной сигнал.

Рисунок 3.3. Функциональная схема генератора (эскизный проект).

20

Таким образом основные параметры метода рассчитаны, далее можно переходить к составлению функциональной схемы генератора синусоиды. Следует отметить, что существует несколько вариантов аппаратной реализации метода, в частности метод может реализован на микроконтроллере (алгоритмически), или на основе FPGA. В данном примере рассмотрим промежуточный вариант, накопитель фазы реализуем на дискретной логике, управление схемой на микроконтроллере.

Опуская дальнейшие рассуждения приведем функциональную схему генератора (рисунок 3.3). Данную схему нельзя считать завершенной и в процессе проектирования в нею будут вноситься изменения.