- •Содержание

- •1. Введение

- •2. Представление информации в эвм

- •2.1. Системы счисления

- •2.1.1. Основные понятия

- •2.1.2. Системы счисления, используемые в вычислительной технике

- •2.1.3. Перевод чисел из одной системы счисления в другую

- •2.2. Типы данных

- •2.2.1. Типы данных, используемых в эвм

- •2.2.2. Константы

- •2.2.3. Логические величины

- •2.2.4. Символьные величины

- •2.2.5. Целые числа

- •2.2.6. Вещественные числа

- •2.3. Форматы команд

- •3. Основы построения эвм

- •3.1. Немного истории

- •3.2. Особенности архитектуры современной вычислительной машины

- •3.2.1. Основные понятия

- •3.2.2. Структурная организация машины

- •3.3. Вариант структуры микроЭвм

- •3.3.1. Общая структура машины

- •3.3.2. Процессор

- •3.3.3. Оперативная память

- •3.3.4. Системная память

- •3.3.5. Система адресации

- •3.3.6. Виртуальная память

- •3.3.7. Таймер

- •3.3.8. Внешние устройства

- •3.3.9. Принципы обмена информацией с внешними устройствами

- •Некоторые вопросы программного обеспечения

- •4.1. О программном обеспечении

- •4.2. Процесс компиляции

- •4.3. Компиляция с языка Ассемблера

- •5. Особенности архитектуры эвм типа ibm-рс

- •5.1. Введение

- •5.2. Исторический обзор процессоров клона 80х86

- •5.3. Классификация процессоров Intel 80х86

- •5.4. Особенности периферийных устройств ibm-pc

- •5.5. Характеристики компьютера

- •5.6. Сегментная адресация

- •5.7. Особенности распределения адресного пространства в компьютерах ibm-pc

- •5.7.1. Стандартная оперативная память (Conventional memory)

- •5.7.2. Область верхней памяти (Upper Memory Area ‑ uma)

- •5.7.3. Область высшей памяти (High Memory Area ‑ hma)

- •5.7.4. Расширенная память (eXtended Memory Specification — xms)

- •5.7.5. Дополнительная память (Expanded Memory Specification — ems)

- •5.8. Обмен информацией с периферийными устройствами

- •5.8.1. Порты ввода/вывода

- •5.8.2. Использование адресного пространства памяти

- •5.8.3. Прямой доступ к памяти

- •5.9. Прерывания

- •5.10. Начальный запуск эвм

- •5.11. Регистры процессора

- •5.11.1. Регистры общего назначения

- •5.11.2. Указатель инструкций

- •5.11.3. Регистр флагов и управляющие регистры

- •5.11.4. Регистры сегментов и селекторов

- •5.11.5. Системные адресные регистры

- •5.11.6. Регистры отладки

- •5.11.7. Регистры тестирования и модельно-специфические регистры

- •6. Debug — средство непосредственной коррекции и отладки загрузочного кода программ

- •6.1. Введение

- •6.1.1. Команды без аргумента

- •Input I порт

- •6.1.2. Команды обращения к ячейкам

- •15D0:010c bfffff mov di,ffff

- •15D0:010f 57 push di

- •6.1.3. Команды запуска программы

- •6.1.4. Команды просмотра и модификации регистров

- •7. Методы адресации

- •7.1. Введение

- •7.2. Регистровый метод адресации

- •159B:0101 1e push ds

- •159B:0101 1e push ds

- •159B:0101 1e push ds

- •7.3. Непосредственный метод адресации

- •7.4. Прямая адресация

- •7.5. Косвенная регистровая адресация

- •159B:0100 not word ptr [bx]

- •159B:0102 e000 loopnz 0104

- •7.6. Адресация по базе

- •7.7. Косвенная регистровая адресация с индексированием

- •159B:0102 0e push cs

- •7.8. Адресация по базе с индексированием

- •7.9. Относительная адресация

- •7.10. Косвенная регистровая адресация с масштабированием

- •7.11. Адресация по базе с индексированием и масштабированием

- •8. Синтаксис ассемблера

- •8.1. Директивы определения данных

- •8.1.1. Определение переменных

- •Cимвольные строки

- •Числовые данные

- •Примеры:

- •8.2. Выражения

- •8.3. Непосредственные операнды

- •8.4. Структуры

- •8.5. Сегменты

- •8.6. Модели памяти и упрощенные директивы определения сегментов

- •8.7. Упрощенные директивы описания сегментов

- •8.8. Создание программы на ассемблере

- •8.9. Получение выполняемого файла

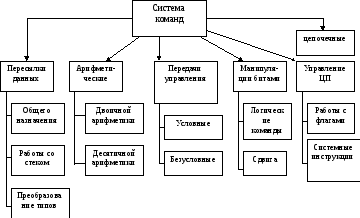

- •9. Система команд

- •9.1. Классификация команд по операндам

- •9.2. Классификация команд по действию

- •9.2.1. Команды пересылки данных

- •9.2.2. Арифметические команды

- •8.2.3. Команды манипуляции битами

- •9.2.4. Управление центральным процессором

- •9.2.4. Команды передачи управления

- •Iret, iretd

- •9.3. Краткий список команд с используемыми операндами

- •9.3.1. Условные обозначения:

- •9.3.2. Инструкции пересылки данных

- •9.3.3. Арифметические, логические и инструкции сдвига

- •9.3.4. Инструкции обработки строк

- •9.3.5. Инструкции передачи управления

- •9.3.6. Инструкции управления процессором

- •Литература

9. Система команд

Машинная команда представляет собой инструкцию процессору, в которой указано: что делать; объекты, над которыми выполняется действие (операнды); как делать (зависит от типа операнда). Также могут присутствовать один или несколько префиксов, указывающих на особенности выполнения команды.

В этой главе мы рассмотрим только команды ЦП, исключив из рассмотрения команды сопроцессора, таким образом, исключив всевозможные расширения: MMX, 3DNow!, SSE, SSE2 и т.д.

9.1. Классификация команд по операндам

Команды имеют переменный формат, каждая команда имеет свою структуру. Команды могут быть:

безадресные — операнд задан неявно на микропрограммном уровне;

одноадресные — операнд рассматривается как источник или получатель;

двухадресные — в двухадресных командах первый операнд является приемником, второй — источником. Содержимое приемника изменяется в зависимости от типа команды. В двухадресной команде операнды имеют одинаковый размер. Возможные сочетания операндов в двухадресных командах:

регистр регистр;

регистр память;

память регистр;

непосредственный операнд регистр;

непосредственный операнд память.

Операнд может располагаться:

в самой команде (непосредственный операнд), например: MOV AX, 0C24, здесь 0C24 — непосредственный операнд;

в одном из регистров процессора или сопроцессора;

в сегменте данных;

в порту ввода/вывода. Номер порта может быть задан и непосредственным операндом (если он <100), и может находиться в регистре DX;

в сегменте стека.

9.2. Классификация команд по действию

9.2.1. Команды пересылки данных

Команды

этой группы пересылают данные из одного

места компьютера в другое: между

регистрами и памятью. Ниже перечислены

основные команды этой группы.

Команды

этой группы пересылают данные из одного

места компьютера в другое: между

регистрами и памятью. Ниже перечислены

основные команды этой группы.

Команда MOV осуществляет пересылку (регистр-регистр или регистр-память) данных между регистрами общего назначения и ячейками памяти.

В процессорах 80686 и выше введены команды условной пересылки CMOVcc. Эти команды производят передачу данных только в случае установленного условия (cc), которое задается различными значениями признаков, установленных в регистре флагов. В этом же процессоре появились команды условной установки бит: SETcc — при выполнении заданного условия значение операнда устанавливается равным 1, в противном случае — 0.

BSWAP производит обмен байтов внутри регистра.

PUSH копирует операнд в вершину стека и сдвигает указатель стека вниз.

РОР берет верхний элемент из стека, помещает в операнд и сдвигает указатель стека вверх. Используются в паре с предыдущей командой.

PUSHA, PUSHAD, РОРА, POPAD выполняют запись в стек и извлечение из него восьми регистров общего назначения. При этом последовательно заполняются или освобождаются восемь 16- или 32-разрядных ячеек стека. При этом PUSHA, РОРА оперируют с 16-разрядными регистрами, а PUSHAD POPAD с 32-разрядными.

IN/OUT производят пересылку данных между аккумулятором ЕАХ (АХ, AL) и адресуемым портом. Адрес порта может задаваться непосредственно операндом или содержимым регистра DX.

Команда MOVSX пересылает данные из меньшего (по числу бит) операнда в больший с расширением знакового разряда.

Команда MOVZX — аналогично, без расширения знакового разряда.

XCHG предназначена для обмена содержимым двух регистров или регистра и ячейки памяти.

В литературе часто упоминается, что команда XCHG обязательно захватывает системную шину на время своего выполнения, но редко объясняется, что это означает и почему это важно.

Рассмотрим двухпроцессорную систему. Допустим, в ячейке A находится число 4, в регистре AX первого процессора число 5 и в регистре AX второго процессора число 2. Оба процессора почти одновременно начали выполнять команду XCHG AX, A. Ее выполнение, с точки зрения шины, состоит из двух операций: чтения из ячейки А и записи в ячейку. Если шина не монополизируется, последовательность операций может быть такой:

|

Операция на шине |

После выполнения операции | ||||

|

T1 |

T2 |

AX1 |

AX2 |

A | |

|

|

x |

x |

5 |

2 |

4 |

|

T1 ← A |

4 |

x |

5 |

2 |

4 |

|

T2 ← A |

4 |

4 |

5 |

2 |

4 |

|

A ← AX1 |

4 |

4 |

5 |

2 |

5 |

|

A ← AX2 |

4 |

4 |

5 |

2 |

2 |

|

AX1 ← T1 |

4 |

4 |

4 |

2 |

2 |

|

AX2 ← T2 |

4 |

4 |

4 |

4 |

2 |

Здесь T1, T2 — программно недоступные промежуточные регистры процессоров.

В результате такой последовательности получился слегка неожиданный результат: в регистрах AX обоих процессоров одно и то же значение, в то время как подобное не могло бы произойти, если бы любой из процессоров выполнил свою команду за один раз, не давая другому возможность модифицировать в это время память. Монопольный захват шины исключение доступа к памяти параллельных процессоров. В этом случае последовательность действий была бы такой:

|

Операция на шине |

После выполнения операции | ||||

|

T1 |

T2 |

AX1 |

AX2 |

A | |

|

|

x |

x |

5 |

2 |

4 |

|

T1 ← A |

4 |

x |

5 |

2 |

4 |

|

A ← AX1 |

4 |

x |

5 |

2 |

5 |

|

AX1 ← T1 |

4 |

x |

4 |

2 |

5 |

|

T2 ← A |

4 |

5 |

4 |

2 |

5 |

|

A ← AX2 |

4 |

5 |

4 |

2 |

2 |

|

AX2 ← T2 |

4 |

5 |

4 |

5 |

2 |

Эта особенность команды XCHG особенно важна, например, при организации семафоров в многопроцессорной системе.

Многие другие команды, в которых приемник является одновременно источником, также могут работать с монопольным захватом шины, если перед ними стоит команда-префикс LOCK.