- •Вопросы по курсу тсис для группы 0032

- •1. Информационная система. Информация.

- •Классификации информационных систем Классификация по архитектуре

- •Классификация по степени автоматизации

- •Классификация по характеру обработки данных

- •Классификация по сфере применения

- •Классификация по охвату задач (масштабности)

- •2. История развития компьютеров и информационных систем.

- •3. Позиционные системы счисления. Перевод чисел из одной системы счисления в другую.

- •4. Арифметика эвм. Представление чисел в форме с фиксированной точкой.

- •5. Сложение в формате с фиксированной точкой. Переполнение.

- •6. Операция вычитания с фиксированной точкой. Дополнительный код числа.

- •7. Умножение и деление чисел в формате с фиксированной точкой.

- •8. Представление чисел в форме с плавающей точкой. Мантисса числа. Характеристика числа.

- •4,72 Х 105; 472 X 103; 4720 X 102микрон или 4,72 х 10-4; 47,2 X 10-5;472 X 10-6км.

- •9. Нормализованные и денормализованные числа.

- •10. Арифметические операции в формате с плавающей точкой.

- •11. Стандарт ieee 754.

- •12. Формат bcd. Представление текстовой информации. Ascii.

- •13. Алгебра логики. Переменные и константы алгебры логики.

- •14. Законы и аксиомы алгебры логики. Логические функции.

- •1. Закон одинарных элементов

- •2. Законы отрицания

- •3. Комбинационные законы.

- •4. Правило поглощения (одна переменная поглощает другие)

- •5. Правило склеивания (выполняется только по одной переменной)

- •15. Конъюнкция. Дизъюнкция. Инверсия. Функционально полная система лф. Функции и-не, или-не, Исключающее или.

- •1. Логическое или (логическое сложение, дизъюнкция):

- •17. Преобразование логических выражений. Склеивание. Минимизация логических выражений.

- •18. Логический элемент. Логическая (комбинационная) схема. Лэ как физическое устройство.

- •19. Обратная связь. Бистабильная ячейка — триггер. Rs-триггер, d-триггер, т-триггер.

- •20. Синхронный триггер. Понятие о синхронизации.

- •21. Узлы эвм. Регистры. Счетчики. Сумматоры. Шифраторы и дешифраторы. Мультиплексоры. Алу.

- •22. Буферные элементы. Шинная организация современного компьютера.

- •23. Понятие архитектуры компьютера. Структура компьютера. Понятие о cisc и risc.

- •24. Регистры общего назначения и их особенности у Intel.

- •25. Команда. Формат команды. Классификация команд. Особенности состава команд у Intel.

- •26. Адресация памяти и ввода-вывода. Циклы обмена между процессором и памятью.

- •27. Абсолютная, прямая и косвенная адресация.

- •28. Автоинкрементная и автодекрементная адресация.

- •29. Стек. Работа стека и его использование.

- •30. Ввод-вывод: программный, по прерываниям и пдп.

- •31. Режимы работы процессора Intel, rm, vm, pm, smm.

- •32. Сегментная и страничная организация доступа к памяти.

- •33. Сегментация памяти в реальном режиме.

- •34. Страничная организация — реализация виртуальной памяти.

- •35. Управление сегментами в защищенном режиме. Дескрипторные таблицы. Дескрипторы сегментов.

- •36. Повышение производительности процессора. Конвейеризация команд и данных. Предсказание переходов. Кэш. Суперскалярность. Многоядерность.

- •37. Понятие шины расширения. Шины pci, pci-X, pci-e.

- •38. Внешние интерфейсы пк. Интерфейс usb.

- •39. Устройства ввода информации.

- •40. Устройства вывода информации.

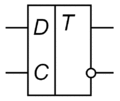

19. Обратная связь. Бистабильная ячейка — триггер. Rs-триггер, d-триггер, т-триггер.

RS-триггер – бистабильная ячейка

D

-Триггер

(Delay

или Data

Триггер) для запоминания. Когда на С

приходит импульс, на выход идет то же,

что стоит на входе, подача импульса на

С прекращается, состояние на выходе

больше не может меняться, т. е. он

«запоминает» состояние и сохраняет его

до следующего импульса на С

-Триггер

(Delay

или Data

Триггер) для запоминания. Когда на С

приходит импульс, на выход идет то же,

что стоит на входе, подача импульса на

С прекращается, состояние на выходе

больше не может меняться, т. е. он

«запоминает» состояние и сохраняет его

до следующего импульса на С

Т

-Триггер

(счетчик). При приходе 0 на Т хранение

информации, при приходе 1 — переворот.

-Триггер

(счетчик). При приходе 0 на Т хранение

информации, при приходе 1 — переворот.

20. Синхронный триггер. Понятие о синхронизации.

Синхронный RS-Триггер

И

зменение

на выходе происходит только при подаче

сигнала на вход С

зменение

на выходе происходит только при подаче

сигнала на вход С

делятся на статические и динамические

Статические — изменение выхода происходит при наличии сигнала на С (разрешение записи)

Динамические — изменение выхода происходит в момент изменения сигнала на С с 0 на 1 и обратно.

21. Узлы эвм. Регистры. Счетчики. Сумматоры. Шифраторы и дешифраторы. Мультиплексоры. Алу.

Регистр — последовательное или параллельное логическое устройство, используемое для хранения n-разрядных двоичных чисел и выполнения преобразований над ними.

Регистр представляет собой упорядоченную последовательность триггеров, обычно D, число которых соответствует числу разрядов в слове. С каждым регистром обычно связано комбинационное цифровое устройство, с помощью которого обеспечивается выполнение некоторых операций над словами.

Ф актически

любое цифровое устройство можно

представить в виде совокупности

регистров, соединённых друг с другом

при помощи комбинационных цифровых

устройств.

актически

любое цифровое устройство можно

представить в виде совокупности

регистров, соединённых друг с другом

при помощи комбинационных цифровых

устройств.

Типичными являются следующие операции:

-приём слова в регистр;

-передача слова из регистра;

-поразрядные логические операции;

-сдвиг слова влево или вправо на заданное число разрядов;

-преобразование последовательного кода слова в параллельный и обратно;

-установка регистра в начальное состояние (сброс).

Счетчики

Счётчик числа импульсов — устройство, на выходах которого получается двоичный (двоично-десятичный) код, определяемый числом поступивших импульсов. Счётчики могут строиться на двухступенчатых D-триггерах, T-триггерах и JK-триггерах.

Сумматоры

Сумматор — устройство, преобразующее информационные сигналы (аналоговые или цифровые) в сигнал, эквивалентный сумме этих сигналов

Накапливающий сумматор

Шифраторы

Шифратор (кодер) — (англ. encoder) логическое устройство, выполняющее логическую функцию (операцию) - преобразование позиционного n-разрядного кода в m-разрядный двоичный, троичный или k-ичный код.

Д воичный

шифратор выполняет логическую функцию

преобразования унарно n-ичного однозначного

кода в двоичный. При подаче сигнала на

один из n входов (обязательно на один,

не более) на выходе появляется двоичный

код номера активного входа.

воичный

шифратор выполняет логическую функцию

преобразования унарно n-ичного однозначного

кода в двоичный. При подаче сигнала на

один из n входов (обязательно на один,

не более) на выходе появляется двоичный

код номера активного входа.

Дешифраторы

Дешифратор (декодер) — комбинационное устройство, преобразующее n-разрядный двоичный, троичный или k-ичный код в -ичный одноединичный код, где - основание системы счисления. Логический сигнал появляется на том выходе, порядковый номер которого соответствует двоичному, троичному или k-ичному коду.

Дешифраторы являются устройствами, выполняющими двоичные, троичные или k-ичные логические функции (операции).

Д воичный

дешифратор работает по следующему

принципу: пусть дешифратор имеет N

входов, на них подано двоичное слово xN

− 1xN − 2...x0, тогда на выходе будем иметь

такой код, разрядности меньшей или

равной 2N, что разряд, номер которого

равен входному слову, принимает значение

единицы, все остальные разряды равны

нулю. Очевидно, что максимально возможная

разрядность выходного слова равна 2N.

Такой дешифратор называется полным.

Если часть входных наборов не используется,

то число выходов меньше 2N, и дешифратор

является неполным.

воичный

дешифратор работает по следующему

принципу: пусть дешифратор имеет N

входов, на них подано двоичное слово xN

− 1xN − 2...x0, тогда на выходе будем иметь

такой код, разрядности меньшей или

равной 2N, что разряд, номер которого

равен входному слову, принимает значение

единицы, все остальные разряды равны

нулю. Очевидно, что максимально возможная

разрядность выходного слова равна 2N.

Такой дешифратор называется полным.

Если часть входных наборов не используется,

то число выходов меньше 2N, и дешифратор

является неполным.

Mультиплексор — устройство, имеющее несколько сигнальных входов, один или более управляющих входов и один выход. Мультиплексор позволяет передать сигнал с одного из входов на выход; при этом выбор желаемого входа осуществляется подачей соответствующей комбинации управляющих сигналов.

М ультиплексоры

могут использоваться в делителях

частоты, триггерных устройствах,

сдвигающих устройствах и др. Мультиплексоры

часто используют для преобразования

параллельного двоичного кода в

последовательный. Для такого преобразования

достаточно подать на информационные

входы мультиплексора параллельный

двоичный код, а сигналы на адресные

входы подавать в такой последовательности,

чтобы к выходу поочередно подключались

входы, начиная с первого и заканчивая

последним.

ультиплексоры

могут использоваться в делителях

частоты, триггерных устройствах,

сдвигающих устройствах и др. Мультиплексоры

часто используют для преобразования

параллельного двоичного кода в

последовательный. Для такого преобразования

достаточно подать на информационные

входы мультиплексора параллельный

двоичный код, а сигналы на адресные

входы подавать в такой последовательности,

чтобы к выходу поочередно подключались

входы, начиная с первого и заканчивая

последним.

АЛУ

А

рифме́тико-логи́ческое

устро́йство (АЛУ) (англ. arithmetic and logic unit,

ALU) — блок процессора, который под

управлением устройства управления (УУ)

служит для выполнения арифметических

и логических преобразований (начиная

от элементарных) над данными, представляемыми

в виде машинных слов, называемыми в этом

случае операндами.

рифме́тико-логи́ческое

устро́йство (АЛУ) (англ. arithmetic and logic unit,

ALU) — блок процессора, который под

управлением устройства управления (УУ)

служит для выполнения арифметических

и логических преобразований (начиная

от элементарных) над данными, представляемыми

в виде машинных слов, называемыми в этом

случае операндами.

Все выполняемые в АЛУ операции являются логическими операциями (функциями), которые можно -разделить на следующие группы:

-операции двоичной арифметики для чисел с фиксированной точкой;

-операции двоичной (или шестнадцатеричной) арифметики для чисел с плавающей точкой;

-операции десятичной арифметики;

-операции индексной арифметики (при модификации адресов команд);

-операции специальной арифметики;

-операции над логическими кодами (логические операции);

-операции над алфавитно-цифровыми полями.