- •Вопросы по курсу тсис для группы 0032

- •1. Информационная система. Информация.

- •Классификации информационных систем Классификация по архитектуре

- •Классификация по степени автоматизации

- •Классификация по характеру обработки данных

- •Классификация по сфере применения

- •Классификация по охвату задач (масштабности)

- •2. История развития компьютеров и информационных систем.

- •3. Позиционные системы счисления. Перевод чисел из одной системы счисления в другую.

- •4. Арифметика эвм. Представление чисел в форме с фиксированной точкой.

- •5. Сложение в формате с фиксированной точкой. Переполнение.

- •6. Операция вычитания с фиксированной точкой. Дополнительный код числа.

- •7. Умножение и деление чисел в формате с фиксированной точкой.

- •8. Представление чисел в форме с плавающей точкой. Мантисса числа. Характеристика числа.

- •4,72 Х 105; 472 X 103; 4720 X 102микрон или 4,72 х 10-4; 47,2 X 10-5;472 X 10-6км.

- •9. Нормализованные и денормализованные числа.

- •10. Арифметические операции в формате с плавающей точкой.

- •11. Стандарт ieee 754.

- •12. Формат bcd. Представление текстовой информации. Ascii.

- •13. Алгебра логики. Переменные и константы алгебры логики.

- •14. Законы и аксиомы алгебры логики. Логические функции.

- •1. Закон одинарных элементов

- •2. Законы отрицания

- •3. Комбинационные законы.

- •4. Правило поглощения (одна переменная поглощает другие)

- •5. Правило склеивания (выполняется только по одной переменной)

- •15. Конъюнкция. Дизъюнкция. Инверсия. Функционально полная система лф. Функции и-не, или-не, Исключающее или.

- •1. Логическое или (логическое сложение, дизъюнкция):

- •17. Преобразование логических выражений. Склеивание. Минимизация логических выражений.

- •18. Логический элемент. Логическая (комбинационная) схема. Лэ как физическое устройство.

- •19. Обратная связь. Бистабильная ячейка — триггер. Rs-триггер, d-триггер, т-триггер.

- •20. Синхронный триггер. Понятие о синхронизации.

- •21. Узлы эвм. Регистры. Счетчики. Сумматоры. Шифраторы и дешифраторы. Мультиплексоры. Алу.

- •22. Буферные элементы. Шинная организация современного компьютера.

- •23. Понятие архитектуры компьютера. Структура компьютера. Понятие о cisc и risc.

- •24. Регистры общего назначения и их особенности у Intel.

- •25. Команда. Формат команды. Классификация команд. Особенности состава команд у Intel.

- •26. Адресация памяти и ввода-вывода. Циклы обмена между процессором и памятью.

- •27. Абсолютная, прямая и косвенная адресация.

- •28. Автоинкрементная и автодекрементная адресация.

- •29. Стек. Работа стека и его использование.

- •30. Ввод-вывод: программный, по прерываниям и пдп.

- •31. Режимы работы процессора Intel, rm, vm, pm, smm.

- •32. Сегментная и страничная организация доступа к памяти.

- •33. Сегментация памяти в реальном режиме.

- •34. Страничная организация — реализация виртуальной памяти.

- •35. Управление сегментами в защищенном режиме. Дескрипторные таблицы. Дескрипторы сегментов.

- •36. Повышение производительности процессора. Конвейеризация команд и данных. Предсказание переходов. Кэш. Суперскалярность. Многоядерность.

- •37. Понятие шины расширения. Шины pci, pci-X, pci-e.

- •38. Внешние интерфейсы пк. Интерфейс usb.

- •39. Устройства ввода информации.

- •40. Устройства вывода информации.

22. Буферные элементы. Шинная организация современного компьютера.

Буферный логический элемент

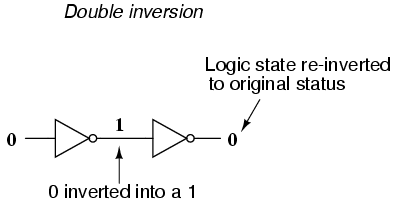

Несмотря на то, что на первый взгляд такое соединение инверторов может выглядеть бессмысленным, у подобной схемы есть практическое применение. Вспомним, что логические элементы являются усилителями сигнала, в независимости от выполняемой ими логической функции. Слабый сигнал (который не может обеспечить достаточного втекающего или вытекающего тока на нагрузку) может быть усилен посредством двух инверторов (как на рисунке выше). Логический уровень останется прежним, однако втекающий или вытекающий ток последнего инвертора будут достаточны для включения нагрузки.

С этой целью применяется особая логическая схема, называемая буферным элементом, действие которой аналогично действию двух инверторов. Символически он изображается треугольником без «кружка» на выходе, обозначающего инвертирование:

Условное обозначение для буферного элемента с открытым коллектором не сильно отличается от условного обозначения простого инвертора: здесь добавлен ещё один включённый по схеме с общим эмиттером транзистор, который осуществляет обратное инвертирование выходного сигнала.

Давайте проанализируем эту схему с точки зрения двух возможных условий: высокий логический уровень на входе и низкий логический уровень на входе. Сначала рассмотрим случай логической единицы:

Как и в случае со схемой инвертора, высокий уровень на входе, левый входной «диод» транзистора Q1 (p-n переход эмиттер-база) не будет проводить. Весь ток с резистора R1 будет течь через базу транзистора Q2, что приведёт к его насыщению:

Это, в свою очередь, введёт в режим насыщения транзистор Q3, в результате чего падение напряжение база-эмиттер выходного транзистора Q4 будет очень малым. Таким образом, транзистор Q4 будет находиться в режиме отсечки, а следовательно не будет проводить. Его выход будет «плавающим» (не соединён ни с землёй ни с Vcc), и это будет эквивалентно «высокому» состоянию на входе следующего элемента ТТЛ. Таким образом, высокий уровень на входе даёт высокий уровень на выходе.

При низком логическом уровне входного сигнала (вход заземлён), анализ будет таков:

Весь ток R1 теперь отводится через входной переключатель, что исключает ток базы на транзисторе Q2. Теперь транзистор Q2 будет закрыт, следовательно ток базы на Q3 будет также отсутствовать. Если транзистор Q3 находится в режиме отсечки, то транзистор Q4 будет находиться в режиме насыщения через резистор R4, замыкая вывод на землю, и теперь здесь будет низкий логический уровень. Таким образом низкий уровень на входе даёт низкий уровень на выходе.

Схема буферного логического элемента с каскадным выходом несколько сложнее, однако основные принципы её функционирования, и естественно, таблица истинности, такие же как и для схемы с открытым коллектором.

РЕЗЮМЕ: Два инвертора (элемента НЕ), соединённые последовательно, проводящие инвертирование и последующее обратное инвертирование двоичного разряда называются буферным логическим элементом.

Буферные элементы применяются для простого усиления сигнала: принимают слабый сигнал на входе и усиливают втекающий или вытекающий ток до уровня, необходимого для работы нагрузки. На схемах буферные элементы изображаются в виде треугольника.

П

одобно

инверторам, существуют буферные элементы

двух типов: с открытым коллектором и

каскадным выходом.

одобно

инверторам, существуют буферные элементы

двух типов: с открытым коллектором и

каскадным выходом.

К омпьютерная

ши́на (от англ. computer bus, bidirectional universal

switch — двунаправленный универсальный

коммутатор) — в архитектуре компьютера

подсистема, которая передаёт данные

между функциональными блоками компьютера.

Обычно шина управляется драйвером. В

отличие от связи точка-точка, к шине

можно подключить несколько устройств

по одному набору проводников. Каждая

шина определяет свой набор коннекторов

(соединений) для физического подключения

устройств, карт и кабелей.

омпьютерная

ши́на (от англ. computer bus, bidirectional universal

switch — двунаправленный универсальный

коммутатор) — в архитектуре компьютера

подсистема, которая передаёт данные

между функциональными блоками компьютера.

Обычно шина управляется драйвером. В

отличие от связи точка-точка, к шине

можно подключить несколько устройств

по одному набору проводников. Каждая

шина определяет свой набор коннекторов

(соединений) для физического подключения

устройств, карт и кабелей.

Ранние компьютерные шины представляли собой параллельные электрические шины с несколькими подключениями, но сейчас данный термин используется для любых физических механизмов, предоставляющих такую же логическую функциональность, как параллельные компьютерные шины. Современные компьютерные шины используют как параллельные, так и последовательные соединения и могут иметь параллельные (multidrop) и цепные (daisy chain) топологии. В случае USB и некоторых других шин могут также использоваться хабы (концентраторы).