- •Содержание введение

- •Задание 1.1.10, 18

- •Условие задачи

- •Краткие теоретические сведения

- •Синтез принципиальной схемы

- •Задание 1.2.6, 142

- •Условие задачи

- •Краткие теоретические сведения

- •Синтез принципиальной схемы

- •Задание 1.3.3, д

- •Условие задачи

- •Краткие теоретические сведения

- •Синтез принципиальной схемы

- •Задание 1.4.7, в

- •Условие задачи

- •Краткие теоретические сведения

- •Синтез принципиальной схемы

- •Задание 1.5.3

- •Условие задачи

- •Краткие теоретические сведения

- •Синтез принципиальной схемы

- •Параметры используемой элементной базы

- •Заключение

- •Список использованных источников

- •Приложение а

- •(Обязательное)

- •Схемы электрические принципиальные

-

Задание 1.5.3

-

Условие задачи

Построить 12-разрядный сумматор с параллельным переносом на микросхемах КР1533ИП3, КР1533ИП4. Обеспечить правильность формирования сигналов P и G на выходе КР1533ИП4 для дальнейшего наращивания 12-разрядных секций. Определить быстродействие.

-

Краткие теоретические сведения

Комбинационным двоичным сумматором называется КС, производящая вычисление суммы двух двоичных n-разрядных чисел. Поскольку при сложении двух n-разрядных двоичных чисел существует вероятность переполнения (результат – n+1-разрядное число), количество выходов сумматора всегда на единицу больше количества разрядов входных входов. Этот дополнительный разряд носит название выхода переноса.

Основой арифметико-логического устройства (АЛУ) служит сумматор, схема которого дополнена логикой, расширяющей функциональные возможности АЛУ и обеспечивающей его перестройку с одной операции на другую.

Сумматоры являются основными вычислительными устройствами, на основе которых могут быть построены схемы, выполняющие другие арифметические операции. Скорость выполнения вычислений в ЭВМ существенно зависит от быстродействия сумматоров, поэтому при проектировании многоразрядных сумматоров должны использоваться методы, позволяющие увеличить их быстродействие.

-

Синтез принципиальной схемы

При высоком уровне напряжения на входе М0 (Mode) отключается блок ускоренного переноса из разряда в разряд и микросхема выполняет логические операции, при низком уровне напряжения выполняются арифметические операции.

Возможность каскадирования микросхем

для работы со словами разрядностью

более четырех обеспечивается наличием

входа переноса  ,

выхода переноса четырехразрядного

каскада

,

выхода переноса четырехразрядного

каскада

,

выхода распространения переноса Х (

,

выхода распространения переноса Х ( и выхода образования переноса Y

(

и выхода образования переноса Y

( ,

при этом выходы Х и Y

используются при необходимости обеспечить

ускоренный перенос с применением

специально спроектированной микросхемы

КР1533ИП4.

,

при этом выходы Х и Y

используются при необходимости обеспечить

ускоренный перенос с применением

специально спроектированной микросхемы

КР1533ИП4.

При выполнении арифметических операций АЛУ представляет собой 4-разрядный сумматор с параллельным переносом. Для того, чтобы АЛУ реализовывало функцию сумматора, необходимо подать комбинацию 1001 на входы выбора (согласно таблице 6.15).

Для сокращения длительности вычислений при суммировании многоразрядных двоичных чисел, пользуются логикой параллельного переноса (принцип предварительного просмотра в схеме ускоренного переноса). При таком способе все переносы рассчитываются непосредственно по входным переменным.

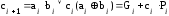

Формула (5.1) выражает функцию распространения переноса.

.

(5.1)

.

(5.1)

Формула (5.2) выражает функцию генерации переноса:

Gi = ai·bi . (5.2)

Формула (5.3) выражает общее соотношение для переноса с уровня i:

. (5.3)

. (5.3)

Значения Pi и Gi, введенные для краткости, фигурируют в полном сумматоре как промежуточный результат, их расчет не требует дополнительных затрат. Определим их смысл. Величина Gi сигнализирует о том, что в данном разряде произошел перенос вследствие комбинации переменных ai и bi на входе, поэтому ее называют переменной генерации переноса. Величина Pi показывает, передается ли далее сигнал переноса, полученный от младшего разряда; ее именуют переменной распространения переноса. По уравнению (5.3) последовательно составим систему равенств для отдельных переносов, приведенную в системе формул (5.4):

c1=G0+c0·P0,

c2=G1+c1·P1= G1+G0·P1+c0·P0·P1, (5.4)

c3=G2+c2·P2= G2+G1·P2+ G0· P2 ·P1+c0·P0·P1·P2,

c4=G3+c3·P3= G3+G1·P2 P3+ G0·P3· P2 ·P1+G2·P3+ c0·P0·P1·P2·P3.

Очевидно, выражения хотя и усложняются с переходом к старшим разрядам, но при каждом переносе длительность формирования вспомогательных переменных равна времени задержки сигнала двух логических элементов.

Вводя ради сокращения переменные генерации переноса для группы G и распространения переноса для группы P, получаем формулу (5.5):

c4=G+c0·P. (5.5)

Представленное выражение формально совпадает с уравнением c4, приведенном выше в раскрытой форме (формула 5.4). Таким образом, достаточно дополнительно сформировать вспомогательные переменные G и P в каждом 4-разрядном блоке сумматора, чтобы воспользоваться алгоритмом межразрядного переноса (приведенная выше система уравнений) для параллельного межгруппового переноса. По этому принципу построим наш 12-разрядный сумматор с параллельным переносом.

А значит, наше целевое устройство будет состоять из трёх 4-разрядных секций (МС КР1533 ИП3) и одной схемы ускоренного переноса (МС КР1533ИП4).

Помимо синтеза схемы, в задании требуется определить быстродействие нашего устройства. Для этого мы используем таблицу динамических параметров микросхемы КР1533ИП3 (таблица 6.15).

Время задержки распространения сигнала

при включении для P и G

tPLH по выходу образования

переноса

вывод

№17) при сложении равно 31 нс, а по выходу

распространения переноса

вывод

№17) при сложении равно 31 нс, а по выходу

распространения переноса

вывод

№15) при сложении равно 34 нс. Поскольку

мы используем схему параллельного

переноса, логично предположить, что

общее быстродействие будет равняться

максимальному времени задержки любого

из наших АЛУ. Итого, быстродействие

равно max(31, 34) = 34 нс.

вывод

№15) при сложении равно 34 нс. Поскольку

мы используем схему параллельного

переноса, логично предположить, что

общее быстродействие будет равняться

максимальному времени задержки любого

из наших АЛУ. Итого, быстродействие

равно max(31, 34) = 34 нс.

Схема приведена на чертеже ГУИР 431231.005 в приложении А.