Тема№5 комп’ютерна схемотехніка

Лабораторне заняття №5/12 Дослідження суматорів та перетворювачів кодів.

Дослідження однорозрядних суматорів.

Дослідження багаторозрядних суматорів.

Дослідження шифраторів та дешифраторів.

1. Дослідження однорозрядних суматорів (напівсуматорів).

Ціль роботи:

вивчити методи проектування суматорів;

придбати практичні навички в побудові однорозрядних та багаторозрядних суматорів;

придбати практичні навички в визначенні роботаздатності суматорів та значень параметрів, які характеризують ефективність їх побудови.

Завдання для підготовки до лабораторної роботи

В ході підготовки до лабораторної роботи необхідно:

Вивчити:

особливості технічної реалізації однорозрядних суматорів комбінаційного типу в різних базисах;

принципи побудови та роботи комбінаційних суматорів паралельного типу;

організацію ланцюгів переносу в суматорах різних видів.

Повторити:

методи синтезу комбінаційних схем;

особливості синтезу схем в різних базисах;

порядок роботи з пакетом Electronics Workbench Pro..

Знайти:

1. Побудувати схему однорозрядного суматора на півсуматорах.

2. Побудувати схему 4-х розрядного суматора:

– з послідовним переносом;

– з паралельним переносом;

– з наскрізним переносом.

3. Побудувати комбінаційні схеми по наступним варіантам:

однорозрядний комбінаційний суматор на елементах І, АБО, НІ (МДНФ);

однорозрядний комбінаційний суматор на елементах І, АБО, НІ (МКНФ);

однорозрядний комбінаційний суматор на елементах І–НІ;

однорозрядний комбінаційний суматор на елементах АБО–НІ;

однорозрядний комбінаційний суматор на елементах 2І–НІ;

однорозрядний комбінаційний суматор на елементах 2АБО–НІ;

однорозрядний комбінаційний суматор на елементах І–АБО– НІ;

однорозрядний комбінаційний суматор на елементах АБО–І– НІ;

напівсуматор на елементах І, АБО, НІ (МДНФ);

напівсуматор на елементах І, АБО, НІ (МКНФ);

напівсуматор на елементах І–НІ;

напівсуматор на елементах АБО–НІ;

однорозрядний суматор на напівсуматорах на елементах І, АБО, НІ (МДНФ);

однорозрядний суматор на напівсуматорах на елементах І, АБО, НІ (МКНФ);

однорозрядний суматор на напівсуматорах на елементах І–НІ;

однорозрядний суматор на напівсуматорах на елементах АБО–НІ;

однорозрядний комбінаційний суматор на елементах І–НІ;

однорозрядний комбінаційний суматор на елементах АБО–НІ;

однорозрядний комбінаційний суматор на елементах 2І–НІ;

однорозрядний комбінаційний суматор на елементах 2АБО–НІ;

однорозрядний комбінаційний суматор на елементах І–АБО– НІ;

однорозрядний комбінаційний суматор на елементах АБО–І– НІ;

напівсуматор на елементах І, АБО, НІ (МДНФ);

напівсуматор на елементах І, АБО, НІ (МКНФ);

напівсуматор на елементах І–НІ;

напівсуматор на елементах АБО–НІ;

однорозрядний суматор на напівсуматорах на елементах І, АБО, НІ (МДНФ);

однорозрядний суматор на напівсуматорах на елементах І, АБО, НІ (МКНФ);

однорозрядний суматор на напівсуматорах на елементах І–НІ;

однорозрядний суматор на напівсуматорах на елементах АБО–НІ;

напівсуматор на елементах АБО–НІ;

Порядок виконання роботи

Запустити пакет Electronics Workbench Pro.

Синтезувати схеми суматорів відповідно до індивідуального завдання.

Набрати на екрані комбінаційну схему суматора, згідно виданому індивідуальному завданню.

Виконати аналіз функціонування схеми суматора (дослідження схеми в статичному режимі).

Відповісти на контрольні запитання викладача.

Відпрацювати звіт на лабораторну роботу.

Зміст звіту

тему, ціль роботи;

таблицю істинності суматора;

діаграми Вейча з занесеними в них значеннями функцій виходів і контурами склеювання;

логічні рівняння, що відображають реалізацію комбінаційної схеми;

функціональну схему розробленого суматора, накреслену з виконанням вимог ЕСКД та ЕСПД;

висновки по роботі (відповідність теорії та практики, причини невідповідності при наявності розходжень).

Контрольні питання

1. Призначення та класифікація суматорів.

2. Побудувати схему повного 1-го суматора на елементах Булевого базису.

3. Побудувати схему повного 1-ого суматора на елементах базису І-АБО-НІ.

4. Пояснити логіку роботи напівсуматора.

5. Побудувати напівсуматор на логічних елементах.

6. Побудувати схему однорозрядного суматора на напівсуматорах.

7. Вивести рівняння для побудови паралельного суматора з паралельним (наскрізним) переносом.

8. Дати порівняну характеристику різних переносів паралельних суматорів.

9. Побудувати схему однорозрядного суматора накопичуючого типу.

Теоретичні відомості

Основною операцією при виконанні арифметичних дій в сучасних ЕОМ є додавання. Операції множення і ділення реалізуються виконанням операції додавання і зсуву кодів чисел, а операція віднімання виконується через додавання із застосуванням додаткових чи зворотних кодів. Тому основним вузлом операційних приладів звичайно є суматор.

С

SM

В основу побудови схем суматорів покладена звичайна ідея додавання двох багаторозрядних чисел, яке виконується вручну:

додавання виконується порозрядно, починаючи з молодшого розряду;

на i-му кроці додаються цифри i-го розряду доданків з урахуванням одиниці можливого переносу з молодшого (i–1)-го розряду.

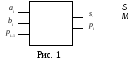

Для реалізації цієї ідеї необхідний пристрій, який має три входи і два виходи. На входи надходять цифри двох доданків aі i bі одного і того ж i-го розряду доданків і цифра переносу із попереднього (i–1)-го розряду. На виході цього пристрою з’являється цифра sі суми даного розряду і перенос pі в наступний старший розряд (рис.1). Такі пристрої називають однорозрядними суматорами. Схеми n-розрядних суматорів звичайно будуються з однорозрядних суматорів.

SM

В основу класифікації суматорів покладені наступні характерні ознаки:

спосіб обробки багаторозрядних чисел;

спосіб організації ланцюжків переносу;

тип однорозрядного суматора, який використовується.

По способу обробки багаторозрядних чисел розрізнюють послідовні, паралельні та послідовно-паралельні суматори.

По способу організації ланцюжків переносів розрізнюють паралельні суматори з послідовним, наскрізним, паралельним та груповим переносами.

По типу однорозрядного суматора, який використовується розрізняють комбінаційні та накопичуючі суматори.

Комбінаційні суматори будуються на базі логічних елементів. В таких суматорах логічний стан виходів залежить тільки від комбінації логічних сигналів на входах в даний момент часу, тобто вони не володіють пам’яттю.

Суматори накопичуючого типу будуються на базі T-тригерів, тому вони володіють функцією зберігання.

Як правило, в сучасних ЕОМ застосовують суматори комбінаційного типу. При цьому функція зберігання реалізується за допомогою регістрів. Суматори накопичуючого типу застосовуються тільки в деяких спеціалізованих ЕОМ.

Основними характеристиками суматорів є швидкодія, тобто максимальний час, необхідний для додавання двох чисел і кількість обладнання, необхідне для їх реалізації.

Синтез однорозрядного суматора

Однорозрядний суматор комбінаційного типу представляє собою комбінаційну схему з трьома входами (ai, bi, pi–1) і двома виходами (si, pi). В таблиці істинності суматора (табл.1) відображені всі можливі комбінації значень ai, bi і pi–1 та відповідні їм значення si і pi, які отримуються при виконанні операції додавання в і-му розряді. Тут ai і bi – відповідно двійкові коди першого і другого доданків в і-му розряді, а pi–1 – перенос з (і–1)-го в і-й розряд, si – код суми, а pi – перенос з і-го в (і+1)-й розряд.

Використовуючи

діаграми Вейча (рис.2), знаходимо мінімальні

диз’юнктивні нормальні форми функційsi

і pi:

Використовуючи

діаграми Вейча (рис.2), знаходимо мінімальні

диз’юнктивні нормальні форми функційsi

і pi:

Таблиця 1

-

№ наб.

ai

bi

pi–1

si

pi

0

0

0

0

0

0

1

0

0

1

1

0

2

0

1

0

1

0

3

0

1

1

0

1

4

1

0

0

1

0

5

1

0

1

0

1

6

1

1

0

0

1

7

1

1

1

1

1

si = ai bi pi–1 ai bi pi–1 ai bi pi–1 ai bi pi–1;

pi = ai bi ai pi–1 bi pi–1.

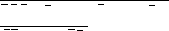

Згідно з отриманими рівняннями легко будується схема однорозрядного комбінаційного суматора (рис.3). З урахуванням інверторів, використовуємих для отримання ai, bi i pi–1 схема має глибину 3. Час виконання операції додавання в такому суматорі визначається виразом

Тдод = 3tле,

де tле – час затримання розповсюдження сигналу в одному логічному елементі.

Ця схема однорозрядного суматора володіє найбільшою швидкодією, хоча і не є оптимальною з точки зору апаратних затрат.

Схема однорозрядного суматора може бути побудована на елементах ІАБО–НI. Для цього з діаграм Вейча (рис.2) знаходимо мінімальні кон’юнктивні нормальні форми функцій si i pi:

s i

= (ai

bi

pi–1)

( ai

bi

pi–1)

(ai

bi

pi–1)

(ai

bi

pi–1);

i

= (ai

bi

pi–1)

( ai

bi

pi–1)

(ai

bi

pi–1)

(ai

bi

pi–1);

pi = (ai bi) (ai pi–1) (bi pi–1).

Після перетворення цих виразів отримаємо:

si = ai bi pi–1 ai bi pi–1 ai bi pi–1 ai bi pi–1;

pi = ai bi ai pi–1 bi pi–1.

Схема однорозрядного суматора, побудованого згідно з останніми виразами, наведена на рис.4. Таку структуру мають ІС однорозрядних суматорів 133ІМ1 і 155ІМ1, а також однорозрядні суматори, з яких побудовані більш складні ІС суматорів.

Якщо до швидкодії суматора не пред’являються дуже високі вимоги, то схема може бути побудована з меншими апаратурними затратами. Розглянемо варіант побудови схеми з використанням логічних елементів, які реалізують логічну функцію “додавання по модулю 2”. Такі елементи входять в склад сучасних серій ІМС. Для цього перетворимо рівняння (1) наступним чином:

si = (ai bi ai bi) pi–1 (ai bi ai bi) pi–1.

Так як

ai bi ai bi = ai bi і ai bi ai bi = ai bi,

отримаємо

si = (ai bi) pi–1 (ai bi) pi–1 = (ai bi) pi–1.

Якщо в діаграмі Вейча для pi (див. рис.2) не проводити об’єднання одиниць в клітинах 3-го і 5-го наборів, отримаємо наступне рівняння для функції переносу:

p i

= ai

bi

ai

bi

pi–1

ai

bi

pi–1

= ai

bi

(ai

bi)

pi–1.

i

= ai

bi

ai

bi

pi–1

ai

bi

pi–1

= ai

bi

(ai

bi)

pi–1.

Остаточно можна записати

si = (ai bi) pi–1;

pi = ai bi (ai bi) pi–1.

Схема однорозрядного суматора, побудованого згідно з рівнянням (2), наведена на рис.5.

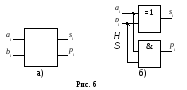

Однорозрядний суматор можна побудувати з більш простих схем (півсуматорів). Півсуматором називається вузол, призначений для додавання двійкових цифр одноіменних розрядів двох чисел без урахування переносу з сусіднього молодшого розряду. Однорозрядний півсуматор здійснює реалізацію функції нерівнозначності, яка описує складання двох або більше двійкових змінних по модулю два. Умовне зображення такого півсуматора наведено на рис. 6а.

С

HS

При синтезі півсуматора отримуються наступні функції si i pi:

si

= (ai

bi),

si

= (ai

bi),

pi = ai bi.

Згідно цим рівнянням на рис.6б наведена схема реалізації півсуматора.

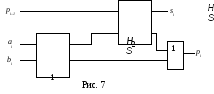

Порівняв схеми однорозрядного суматора (рис.5) і півсуматора (рис.6б) неважко помітити, що однорозрядний суматор можна реалізувати на двох півсуматорах (рис.7).

HS

HS