- •Министерство образования рф

- •1. Цели работы.

- •2. Исходные данные.

- •2.1. Общие исходные данные.

- •2.2. Индивидуальные исходные данные.

- •3. Разработка структурной схемы.

- •Системная шина

- •4. Система прерываний.

- •4.1. Последовательная структура.

- •4.2. Прерывания на микроуровне.

- •5. Основная память эвм.

- •6. Схема контроля.

- •Input/Output по паритету.

- •7. Блок синхронизации.

- •8. Монитор.

- •9. Таймер.

- •10. Клавиатура.

- •11. Контроллер пдп.

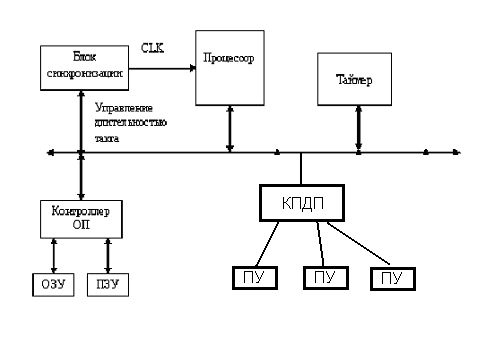

3. Разработка структурной схемы.

Структура ЭВМ – шинная (магистральная) (рис.1) Состав шин: шина адреса и данных (AD) и шина управления (CB). Двухшинная организация предполагает передачу адреса и данных по одним и тем же физическим проводникам в разные моменты времени. Например, адрес передается по фронту синхросигнала, данные по спаду или же специальный сигнал определяет, что в данном такте находится на шине. Возможны комбинированные варианты: информация “готова” и на фронте и на спаде, а качество (данные/адрес) определяется селектирующим сигналом. Разрядность шины адреса/данных – 32 бита.

Шина управления предназначена для управления работой ЭВМ и содержит такие сигналы, как: запрос памяти MEMRQ, запрос регистров ввода-вывода IORQ, сигналы вывода-ввода информации RD/WR, запрос прерывания INT, подтверждение прерывания INTA, синхросигнал, сигнал сброса RST, сигнал, определяющий информацию на шине AD как адрес, или как данные и т.д.

Системная шина

При включении питания (и пока активенRST)

процессор, чтобы избежать, гонок на шине

адрес/данные, должен держать сигналы

MEMRQ

и IORQ

неактивными (это запретит устройствам

вывод на шину адрес/денные, а что твориться

в это время в конкретном устройстве –

забота самого устройства). Внутри

процессора выходы всех регистров

переведены в третье состояние. Далее

процессор секвенсер выбирает микрокоманду,

и ЭВМ уже работает в обычном режиме.

Рис. 1 Структурная схема ЭВМ.

В состав ЭВМ входят следующие блоки:

Процессор – основной блок (рис. 2.) В его состав входят: адресный сопроцессор, операционный блок (ОБ) и микропрограммное устройство управления (МУУ). ОБ – средство выполнения арифметических, логических, сдвиговых операций, адресный сопроцессор – средство формирования адреса (фактически такой же процессор, только целочисленный), а МУУ – средство управления ОБ, адресным сопроцессором и всей ЭВМ в целом.

В состав ОБ входят:

регистровое ЗУ (РЗУ);

арифметико-логическое устройство (АЛУ);

статусный регистр;

средства связи с внешней шиной адрес/данные;

В состав МУУ входят:

Регистр команд;

Преобразователь начального адреса (ПНА);

Секвенсер микрокоманд;

Микропрограммная память (ММП);

Регистр микрокоманд.

Код операции из регистра команд поступает на ПНА. Преобразованный адрес с ПНА идет на секвенсор. Секвенсор выбирает источник адреса и выдает его на вход МПП. На выходах последней появляется микрокоманда и фиксируется в регистре микрокоманд. В момент, когда микрокоманда начинает выполняться, секвенсор формирует адрес следующей микрокоманды.

На границе инструкций контроллер прерываний при активном INT выдает инструкцию вызова прерываний. Далее все штатным образом: выполняется микропроцедура обработки прерывания, которая сохраняет словосостояние процессора, активирует INTA, получат вектор процессора, выполняет обработчик.

Управляемый блок синхронизации. Формирует временные диаграммы, необходимые для функционирования ЭВМ. Управляемость подразумевает возможность приостановления такта, изменения длительности, что бывает необходимо, например, для обмена информацией процессора с “медленными” внешними устройствами.

Контроллеры ввода-вывода (адаптер дисплея, контроллеры клавиатуры, магнитных накопителей и др.) необходимы для обеспечения сопряжения внешних устройств, работающих по своим протоколам, с устройствами системной шины (здесь протоколы обмена совершенно другие).

К внешним устройствам относятся такие устройства как:

дисплей – средство вывода информации;

клавиатура, мышь – средства ввода информации;

«флоп», «винчестер» – внешние ЗУ.

Таймер – устройство отсчёта времени. Представляет собой кварцевые часы, которые можно программно опрашивать, устанавливать, использовать в качестве будильника, в определённое время выдающего сигнал в процессор, или в качестве секундомера при замерах интервалов времени между внешними событиями и т.д.

Рис. 2 Структурная схема процессора.