Дмитриев Универсалный лабораторный стенд. Аппаратные средства проектирования встраиваемых систем 2009

.pdf

подключать источники сигналов ПЛИС к внешней шине МК только при чтении по выделенным для ПЛИС адресам. На рис. 3.3 показана временная диаграмма цикла внешней шины МК при выполнении следующей последовательности команд:

MOVDPTR,#7FFBh

MOVXA,@DPTR

Рис. 3.3. Цикл внешней шины при чтении из ПЛИС

На рис. 3.4 приведен вариант схемы для чтения по двум выделенным для ПЛИС адресам. В схеме используются буферные элементы с сигналами управления низкого и высокого уровня. На элементах BUFT8 и BUFE8 реализован мультиплексор шины данных для выбора одного из двух возможных источников.

Рис. 3.4. Вариант схемы для чтения данных из ПЛИС

61

3.2.ОРГАНИЗАЦИЯ ОБМЕНА ПО ПРЕРЫВАНИЯМ МЕЖДУ МК И УСТРОЙСТВОМ НА ПЛИС

Одним из способов организации обмена данными МК с внешними устройствами, является использование прерываний. Такую возможность можно реализовать для обмена данными МК с устройством, реализованным на ПЛИС. Как уже говорилось, в УЛС пользователю доступно для этих целей только одно внешнее прерывание INT0. Это прерывание может быть сконфигурировано либо по низкому уровню (активное значение – «0»), либо по перепаду 1/0. Напомним, что флаг IE0 в обоих случаях устанавливается аппаратно, а сбрасывается аппаратно только при конфигурировании прерывания по изменению 1/0 (при входе в обработчик прерывания). При конфигурировании по уровню обработчик прерывания должен сформировать воздействие на источник прерывания с тем, чтобы его запрос был снят и, соответственно, сброшен флаг IE0, до момента выхода из обработчика. Проиллюстрируем эти способы работы с прерыванием INT0.

Рассмотрим пример, в котором INT0 сконфигурировано по низкому уровню. На рис. 3.5 показана схема, которая вырабатывает сигнал прерывания INT0 c активным низким уровнем.

Рис. 3.5. Схема генерации внешнего прерывания по низкому уровню сигнала INT0

62

При нажатии кнопки ГОИ2 триггер, который собственно и является источником сигнала прерывания устанавливается в исходное состояние «0». На линии INT0 устанавливается пассивное значение «1». При нажатии кнопки ГОИ1 триггер переключается в состояние «1», а на линии INT0 устанавливается активный уровень «0». Если прерывание INT0 разрешено, то в МК управление передается подпрограмме обработки прерывания.

Пример текста обработчика внешнего прерывания по низкому уровню сигнала INT0:

|

ORG 8000H |

|

||

; |

LJMP M1 |

|

||

ORG |

8003H |

;обработчик прерывания INT0 |

||

|

||||

|

INC |

R0 |

|

|

|

MOV |

R1,#00H |

|

|

M3: |

INC |

R1 |

|

|

|

CLR |

TR0 |

;выключение таймера |

|

|

CLR |

TF0 |

;сброс флага переполнения таймера Т0 |

|

|

MOV |

TL0,#00H |

|

|

|

MOV |

TH0,#00H |

|

|

|

MOV |

TMOD,#00H |

;таймер T0 режим 0 |

|

|

SETB |

TR0 |

;включение таймера |

|

M2: |

JNB |

TF0,M2 |

|

|

|

CJNE R1,#0FFH,M3 |

|

||

|

MOV DPTR,#7FFAH |

|

||

|

MOVX |

@DPTR,A |

; сброс триггера |

|

|

MOV A,R0 |

|

||

|

SWAP |

A |

|

|

|

MOV 0C0H,A |

;вывод счетчика в порт Р4 |

||

; |

RETI |

|

|

|

|

|

|

||

M1: |

MOV IE,#81H |

;разрешение прерывания INT0 |

||

|

MOV TCON,#00H |

;конфигурирование прерывания INT0 |

||

|

|

|

;низкому уровню |

|

|

MOV |

|

R0,#00H |

|

|

LJMP $ |

|

||

|

END |

|

|

|

Для сброса активного низкого значения сигнала прерывания в схеме применяются элементы для сброса триггера в нулевое состояние при выполнении обработчиком команды записи по адресу 7FFAh. Кроме этого, в обработчике реализован программный счет-

63

чик на регистре R0, содержимое которого выводится для индикации в порт Р4 (светодиодные шкалы А и В). С использованием таймера Т0 реализовано формирование задержки длительностью, достаточной для наблюдения в третьем разряде светодиодной шкалы С появления и сброса сигнала прерывания.

Проанализируем второй способ работы с прерыванием INT0. Для этого рассмотрим схему, приведенную на рис. 3.6.

Рис. 3.6. Схема генерации внешнего прерывания по изменению 1/0 сигнала INT0

На рис. 3.7 приведена временная диаграмма ее работы. Из диаграммы видно, что данная схема при нажатии кнопки ГОИ2 на линии INT0 генерирует сигнал низкого уровня в течение 16 периодов генератора тактовых сигналов. Следует заметить, что при этом генератор ГОИ1 должен работать в непрерывном режиме. Тем самым выполняется требование по длительности сигнала прерывания, которая должна быть не менее 12 периодов. Для установки схемы в исходное состояние используется разряд 0 клавишного регистра Р1.

64

Рис. 3.7. Временная диаграмма схема генерации внешнего прерывания по изменению 1/0 сигнала INT0

Ниже приведен текст обработчика прерывания по изменению

1/0 сигнала INT0:

ORG8000H |

|

|

LJMP |

M1 |

|

;-------------------------------------------------------------------------------------------------- |

|

|

ORG |

8003H |

;обработчик прерывания INT0 |

INC |

R0 |

|

MOV |

R1,#00H |

|

M3: INC |

R1 |

|

CLR |

TR0 |

;выключение таймера |

CLR |

TF0 |

;сброс флага переполнения таймера Т0 |

MOV |

TL0,#00H |

|

MOV |

TH0,#00H |

|

MOV |

TMOD,#00H |

;таймер T0 режим 0 |

SETB |

TR0 |

;включение таймера |

M2: JNB |

TF0,M2 |

|

CJNE |

R1,#0FFH,M3 |

|

MOV |

A,R0 |

|

MOV |

0C0H,A |

; вывод счетчика в порт Р4 |

RETI |

|

|

;------------------------------------------------------------------------------------------------- |

|

|

M1: MOV IE,#81H |

;разрешение прерывания INT0 |

|

MOV TCON,#00H |

;конфигурирование прерывания INT0 по |

|

MOV R0,#00H |

;низкому уровню |

|

|

||

LJMP $

END

65

Отличие от предыдущей программы состоит в том, что из программы удалены команды для выполнения записи по адресу 7FFAh и переконфигурировано прерывание INT0.

Как и в предыдущем случае, на индикацию выводятся сигнал прерывания и программный счетчик, реализуемый обработчиком. Но в этом случае из-за того, что сигнал прерывания имеет длительность 1,5 мкс, визуальному наблюдению он не поддается. Зато вывод на индикацию состояния программно формируемого счетчика на регистре R0 осуществляется с заметной задержкой, формируемой, как и прежде, на таймере Т0.

3.3.ОРГАНИЗАЦИЯ ПРОГРАММНОГО ОБМЕНА ПО ФЛАГУ ГОТОВНОСТИ ВНЕШНЕГО УСТРОЙСТВА

Данный тип обмена поясним на примере выполнения чтения данных из устройства, реализованного на ПЛИС. Рассмотрим случай, когда устройство на ПЛИС подключено к внешней шине МК. Положим, что МК только читает данные из ПЛИС. При программном обмене необходимо использовать флаг готовности данных для чтения в МК. Этот флаг автоматически устанавливается устройством при наличии готовых данных и сбрасывается после их чтения в МК. Очередные данные могут быть считаны в МК, если установлен флаг их готовности. Таким образом, перед чтением данных необходимо дождаться появления флага готовности. Очередные данные могут быть выставлены устройством, если этот флаг сброшен. Эти условия обеспечивают целостность передаваемых данных. В этом случае ни одна посылка данных не может быть потеряна. Так как обмен идет через внешнюю шину МК, и читаться должны не только данные, но и флаг их готовности, то при организации обмена необходимо задействовать две адресные линии, подключенные к ПЛИС. Выделим адрес 7FFAh для чтения флага готовности данных, а адрес 7FFBh для чтения самих данных. Флаг готовности, читаемый в МК, будет отображаться в разряде D0 шины данных.

Рассмотрим организацию программного обмена по флагу готовности на примере следующей схемы, изображенной на рис. 3.8.

66

Рис. 3.8. Схема для реализации программного обмена по флагу готовности

Схема содержит 8-разрядный буферный регистр, куда внешнее устройство помещает данные для чтения в МК (шина INT_WE[7-0] и сигнал разрешения записи INT_WE) и триггер флага готовности. Для обеспечения условия корректности передачи данных, флаг должен быть доступен для проверки как со стороны МК, так и внешнего устройства. Так как для сброса триггера используется асинхронное управление, то логика анализа флага во внешнем устройстве должна учитывать не только состояние триггера, а и сигнала чтения RD_RG на его входе CLR. Это связано с тем, что сигнал чтения MKRD, формируемый МК, имеет минимальную длительность в 5 периодов тактового генератора, в течение которых флаг удерживается в сброшенном состоянии, что в принципе может разрешать внешнему устройству записывать новые данные, когда предыдущие еще несчитаны. Если этого не сделать, то к моменту снятия сигнала MKRD устройство может записать в буферный регистр несколько посылок данных. МК при этом считает

67

только последнюю из них, так как фиксация считанных в МК данных осуществляется при изменении 0/1 сигнала MKRD.

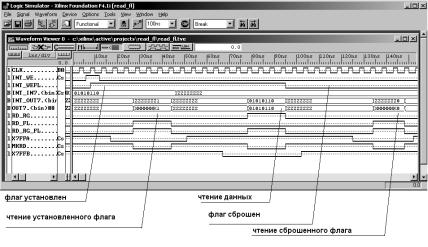

Временная диаграмма, иллюстрирующая работу данной схемы при чтении данных, приведена на рис. 3.9. В начальном состоянии флаг готовности INT_WEFL сброшен, что разрешает запись в буферный регистр. После установки сигнала (INT_WE) и с приходом тактового импульса по линии CLK осуществляются запись значения 01010110b в буферный регистр и установка флага готовности данных для чтения в МК. При выполнении команды чтения по адресу 7FFAh (сигналы низкого уровня по линиям X7FFA и MKRD) этот флаг передается в МК (состояние шины OUT7 – XXXXXXX1b, то есть в младшем разряде шины данных D0 фиксируется значение «1»). После этого МК выполняет чтение данных (сигналы низкого уровня по линиям X7FFВ и MKRD), при котором состояние шины OUT7 - 01010110b. Из диаграммы видно, что сразу после снятия сигнала MKRD устанавливается флаг готовности INT_WEFL. Действительно, при выполнении команды чтения по адресу 7FFAh в младшем разряде шины данных D0 фиксируется значение «0» (состояние шины OUT7 – XXXXXXX0b).

Рис. 3.9. Временная диаграмма реализации программного обмена по флагу готовности

68

Сброс флага свидетельствует об отсутствии новых данных в буферном регистре внешнего устройства. Ниже приведен текст программы для приема из внешнего устройства блока данных из 32 байт и записи его в массив во внутренней памяти данных с адреса 80h. После завершения приема блока программа выводит в порт Р4 контрольный код 33:

ORG 8000h |

|

|

MOV |

R0,#7Fh |

|

M2: INC |

R0 |

;указатель массива |

MOV |

DPTR,#7FFAh |

|

M1: MOVX |

A,@DPTR |

;чтение флага |

ANL |

A,#01h |

;выделение маской разряда D0 |

JZ |

M1 |

;ожидание флага |

MOV |

DPTR,#7FFBh |

|

MOVX |

A,@DPTR |

;чтение данных |

MOV |

@R0,A |

;запись данных в массив |

CJNE |

R0,#9Fh,M2 |

;контроль длины блока ;данных |

MOV |

0C0h,#33h |

;вывод контрольного кода |

END |

|

|

3.4.ОРГАНИЗАЦИЯ ПРОГРАММНОГО ОБМЕНА С ИСПОЛЬЗОВАНИЕМ БУФЕРА FIFO

Данный вид обмена используется для передачи данных между устройствами, которые работают с различной скоростью. Одно из устройств записывает данные, а другое читает их в том же порядке, в каком они были записаны. При записи в FIFO анализируется флаг FULL (буфер заполнен). Если этот флаг установлен, то это говорит о заполненности буфера и невозможности помещения в него очередных данных. В этом случае следует дождаться сброса этого флага после очередного чтения. Если емкость буфера FIFO выбрана правильно, то такая необходимость возникает достаточно редко. В этом случае проявляется преимущество FIFO, которое состоит в том, что после записи каждой новой порции данных проверяется только флаг FULL, и нет необходимости каждый раз дожидаться флага, свидетельствующего об извлечении из буфера данных читающим устройством. Аналогичная ситуация возникает при чтении данных. Чтение возможно, только если сброшен флаг EMPTY (буфер пустой).

69

Рассмотрим пример организации обмена через FIFO, Когда осуществляется передача данных из устройства, выполненного на ПЛИС, в МК. Будем использовать буфер синхронного FIFO емкостью 16 восьмиразрядных слов. Управление буфером осуществляется сигналами RESET – синхронного сброса, RE – разрешения чтения и WE – разрешения записи. Выполнение данных операций осуществляется по изменению 0/1 синхросигнала. FIFO построено с использованием двухпортового ОЗУ, и допускает одновременное выполнение записи и чтения. На рис. 3.10 дана схема реализации обмена через FIFO, в которой показаны все необходимые элементы для чтения данных в МК. В схеме используются два адресных сигнала: X7FFВ – для чтения состояния флага EMPTY (разряд D0 шины данных МК) и X7FFА – для чтения данных из FIFO, а также сигнал чтения MKRD.

Рис. 3.10. Схема реализации обмена через FIFO

В данной схеме для обеспечения обмена FIFO и МК через внешнюю шину последнего используется схема выделения полного периода на двухразрядном счетчике и 8-разрядный буферный регистр. Это связано со следующими особенностями работы FIFO. Во-первых, запись и чтение выполняются синхронно по изменению 0/1 синхросигнала, если установлены сигналы разрешения WE и RE соответственно. Минимальная длительность строба чтения

70