Сысоев Информационные технологии в физических исследованиях Лабораторный практикум 2009

.pdf

Коэффициент передачи Kп характеризует усреднённый наклон передаточной характеристики и имеет размерность, определяемую как размерность входного сигнала/бит.

Погрешность коэффициента передачи Kп – разность между идеальными и реальными значениями коэффициента передачи (или значениями предела шкалы).

Погрешность смещения нуля Iсм.0 – выходной сигнал, соответствующий нулевому входному цифровому коду.

Дифференциальная нелинейность Nдиф=Nдиф макс – отклонение разности двух аналоговых сигналов, соответствующих последовательной смене кодов от значения, соответствующего единице младшего значащего разряда. Измеряется в процентах или долях шага квантования

Характеристики и параметры, описывающие динамиче-

ские свойства ЦАП. Время установления выходного сигнала tуст (см. рис. 1.4) – интервал времени от момента изменения входного цифрового кода на 50 % до момента, при котором выходной сигнал окончательно войдёт в зону установившегося состояния Iвых=I0±∆I, соответствующего допустимому отклонению от номинального значения.

Рис. 1.4. График установления выходного сигнала

10

Время задержки tзд – интервал времени от момента изменения входного цифрового кода на 50 % до момента изменения выходного сигнала на 10 % от его установившегося значения.

Время нарастания tн – интервал времени от момента достижения выходным сигналом уровня 10 % от его установившегося значения до момента достижения уровня, наименьшего номинального значения. Типичные значения этого параметра для микросхем различных серий следующие: 572ПА2 – tн = 15 мкс; Л1108ПА1 – tн = = 0,4 мкс; К118ПА1 – tн= 20 нс.

Одним из важнейших элементов ЦАП является токовый «ключ», представленный на рис. 1.5. От скорости его срабатывания зависят такие характеристики ЦАП, как время задержки tзд, время нарастания tн и время установления стационарного состояния tуст. Опорное напряжение на базе VT2 создается цепочкой VD1, R3. Резистор Rэ выполняет функцию генератора тока, так как Rэ >> R1,

R2. Когда напряжение Uу, подаваемое на базу VT1, меньше опорного ток протекает по цепи R3, VT2, Rэ. Если напряжение Uу больше опорного происходит коммутация тока, и ток протекает по цепи R1, VT1, Rэ. Время переключения токового ключа обычно меньше аналогичной величины для ключа напряжения, так как транзисторы VT1 и VT2 не насыщаются.

1.1.2. Аналого-цифровые преобразователи сигналов

АЦП преобразуют непрерывный (аналоговый) электрический сигнал в дискретную цифровой форму. В процессе преобразования аналогового сигнала можно выделить несколько этапов:

1) дискретизация аналогового сигнала – выделение из непрерывного временного интервала временных точек, разделяющих время на периоды (шаги) дискретизации . Этим точкам соответствует ряд определенных (дискретных) значений аналогового сигнала;

11

2) квантование сигналов (выборка значений) – все сигналы указанного в п. 1 ряда квантуются (делятся) с заданным шагом квантования, причем в случае нецелочисленного деления производится округление с потерей остатка. Максимальное число квантов ставят в соответствие заранее заданному напряжению (например, 5 В). Потеря остатка от деления является максимальной неустранимой погрешностью – погрешность квантования;

3) кодирование в двоичный код – преобразование полученного числа квантов, соответствующих каждому измеряемому сигналу/напряжению в двоичный код.

Классификация АЦП. К настоящему времени известны различные методы преобразования электрического сигнала/напряжения в цифровой код. В основу одного из вариантов классификации АЦП положен принцип, по которому происходит обработка аналогового сигнала (рис. 1.6). В соответствии с этим принципом все АЦП делятся на три группы, в которых используется: 1) параллельное преобразование– получение всего цифрового кода одновременно, 2) последовательное и 3) последовательно-параллельное

– поочередное получение кода или его частей.

Рис. 1.6. Классификация АЦП

12

Циклический АЦП последовательного счета. АЦП включает в себя генератор тактовых импульсов (ГТИ), элемент логического умножения «&», двоичный счетчик, ЦАП, компаратор напряжений

K (рис. 1.7).

Рис. 1.7. Структурная схема циклического АЦП последовательного счета

При подаче импульса «пуск» на вход счетчика его содержание обнуляется, а подаваемый со счетчика нулевой код формирует на выходе ЦАП нулевой сигнал Uпреобр = 0. Данный сигнал на входе операционного усилителя, работающего в режиме компаратора, при ненулевом входном напряжении на другом его входе приводит к формированию на выходе компаратора высокого уровня (логическая «1»). При подаче логической «1» на один из входов микросхемы «И» прямоугольные импульсы от ГТИ проходят на выход микросхемы, а следовательно, поступают на вход счетчика импульсов. Счетчик производит счет этих импульсов и выдает на выходах Q0, Q1, …Qn-1 двоичный код числа сосчитанных на каждый момент времени импульсов. На выходе ЦАП значение Uпреобр ступенчато возрастает по мере счета импульсов (рис. 1.8.).

Когда Uпреобр превысит Uвх (Uпреобр ≥ Uвх), компаратор переходит в другое устойчивое состояние, а на его выходе появляется логический «0». В ответ элемент «&» прекращает пропускать импульсы с тактового генератора ГТИ, и показания счетчика фиксируются, т.е. выходы X0, X1, …, Xn-1 выдают код, соответствующий аналоговому значению Uвх. Новый цикл преобразования начинается при подаче импульса «пуск».

13

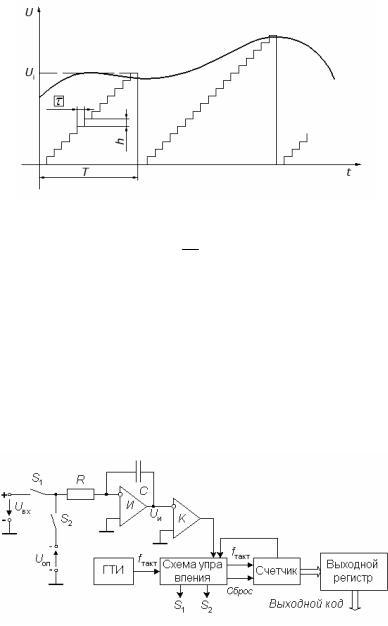

Рис. 1.8. Временная диаграмма циклического АЦП последовательного счета

Время дискретизации T Ui , где Ui – величина напряжения, h

соответствующая полученному двоичному коду, h – шаг квантования (напряжения). Максимальное значение (Ui/h)макс = 255 для восьмиразрядных АЦП, т. е. в неблагоприятных случаях T достаточно велико, что существенно замедляет оцифровку сигнала. Поэтому данная схема почти не используется, но, являясь самой простой реализацией АЦП, полезна для понимания принципа его работы.

Циклический интегрирующий АЦП. Особенностью интегри-

рующих АЦП (рис. 1.9) является высокая помехоустойчивость, которая достигается увеличением времени преобразования: составляющая помехи интегрируется за время, много большее ее периода.

Рис. 1.9. Структурная схема циклического интегрирующего АЦП

14

Но нежелательным следствием является снижение быстродействия АЦП, если помеха сетевая. Для представленной на рис. 1.9 схеме АЦП двойного интегрирования. преобразование осуществляется в два этапа: интегрирования и счета. В начале первой стадии ключ S1 замкнут, а ключ S2 разомкнут. На интегратор И поступает напряжение Uвх. Время интегрирования входного напряжения t1 постоянно; в качестве таймера используется кольцевой счетчик с коэффициентом пересчета Kсч – отношение времени интегрирования к периоду счетчика, то есть количество импульсов за время интегрирования:

K |

сч |

|

t1 |

t |

1 |

f |

такт |

N |

max |

. |

|

tтакт |

|||||||||||

|

|

|

|

|

|

Принцип данного АЦП мало отличается от предыдущего. Так как в схеме есть накопительная ёмкость, то сигнал, поступающий на один из входов интегратора на операционном усилителе, постепенно возрастает, как только он сравняется с аналоговым сигналом по величине, дальнейшие действия будут такими же, что и в предыдущем АЦП. По окончании времени интегрирования t1 на выходе интегратора И напряжение Uс составляет:

|

1 |

t1 |

Uвх.срKсч |

|

Uи(t1) |

|

Uвх(t)dt |

|

. |

RC |

fтактRC |

|||

|

|

0 |

|

|

В этот момент времени происходит переключение ключей (S1 размыкается, S2 замыкается), а на вход И подается Uоп (противоположное по знаку Uвх). Время интегрирования второй стадии t2 определяется уравнением:

|

1 |

t1 t2 |

|

Uи(t1) |

t Uоп(t)dt 0 , |

||

RC |

|||

|

|

1 |

то есть интегрирование заканчивается, когда Uс становится равным нулю.

На рис. 1.10 представлены два случая для двух значений Uвх (сплошная и пунктирная линии). Поскольку время зарядки от входного сигнала фиксировано (t1 = const), напряжение на емкости в конце этапа зарядки линейно связано с Uвх.

15

Рис. 1.10. Временная диаграмма интегрирующего АЦП

Вместе с тем, скорость перезарядки емкости от Uоп является константой, а следовательно, как это видно из рис. 1.10, время полной зарядки и разрядки линейно связано с Uвх. Так, при Uвх2 = = 0,5Uвх1 имеем t22 = 0,5t21. Время t2 определяется через показание счетчика (коэффициент пересчета для 2-й стадии):

t2 n2 ,

fтакт

где n2 – показания счетчика за период t2. В итоге зависимость показания счетчика на второй стадии от среднего значения анализируемого сигнала (Uвх.ср.) имеет вид:

n2 Uвх.срKсч . Uоп

Из этой формулы следует, что отличительной особенностью метода двойного интегрирования является то, что ни тактовая частота, ни постоянная интегрирования RC, ни порог срабатывания компаратора не влияют на результат. Необходимо только потребовать, чтобы тактовая частота в течение времени t1 + t2 оставалась

16

постоянной, что легко достижимо на временах преобразования, характерных для серийных АЦП.

Следящий АЦП последовательного счета (рис. 1.11). Заме-

ной обычного счетчика на реверсивный в схеме циклического АЦП удается уменьшить период дискретизации. Изменение в алгоритме преобразования сигнала наглядно видно из временной диаграммы этого типа АЦП (рис. 1.12).

Рис. 1.11. Структурная схема нециклического АЦП последовательного счета («следящий»)

Рис. 1.12. Временная диаграмма нециклического АЦП последовательного счета

17

Принцип действия такого АЦП следующий. На первом шаге квантования Т1 порядок его работы аналогичен циклическому АЦП (см. рис. 1.12), а затем при переключении компаратора за счет инвертора и второго логического элемента «И» направление счета реверсивного счетчика меняется на обратное. Таким образом, в отличие от обычного циклического АЦП, у реверсивного вход состоит из двух каналов, построенных на логических элементах 1«И» и 2«И». Если у обычного циклического АЦП после достижения соотношения Uпреобр = Uвх, происходит сброс показаний счетчика и процесс нарастания Uпреобр начинается от нулевого значения Uпреобр, то в нециклическом АЦП меняется только направление счета. В итоге схема «следит» за сигналом, что позволяет уменьшить период дискретизации для гладкой зависимости Uвх(t), что в случае слабо изменяющегося сигнала является очевидным преимуществом. Однако здесь нет строгой синхронизации во времени такой привязки по времени.

АЦП с поразрядным уравновешиванием. Число в системе исчисления с меньшей разрядностью может быть аналитически представлено в системе исчисления с большей разрядностью (например, двоичная в десятичной) как сумма вкладов каждого разряда в отдельности:

n

aili

i 0

где i – разряд, ai – значение весового коэффициента i-го разряда («0» или «1»), li – “вес” текущего разряда. Алгоритм перевода числа из одной системы (с большей разрядностью) в другую (с меньшей разрядностью) можно осуществить двумя способами (на примере числа 10112 = 1110, см. табл.1.1).

В первом способе мы сравниваем остаток от целочисленного деления числа на значение разрядов, начиная со старшего. Так, при делении числа 11 на 8 получаем 1 и 3 в остатке. Но 8 в двоичной системе исчисления есть 1 в четвертом разряде, которая и присваивается в двоичном числе. При делении остатка 3 на значение числа в старшем последующем разряде дает частное меньше единицы, поэтому в третьем разряде двоичного числа присваивается 0, и т.д.

18

|

|

|

Таблица 1.1 |

|

|

Пояснения к операциям, проводимым в АЦП по тактам |

|||

|

|

|

|

|

№ |

1-й способ |

2-й способ |

Двоичная |

|

такта |

система |

|||

|

|

|||

|

|

|

|

|

|

11/8 = 1 (3 в остатке) |

11/8 = 1 (3 в остатке) |

1 |

|

|

(11–8)/4 = 0 |

11/(8 + 4) = 0 |

0 |

|

|

(11-8)/2 = 1 (1 в остатке) |

11/(8 + 2) =1 (1 в остатке) |

1 |

|

|

(11–8–2)/1 = 1 (0 в остат- |

11/(8 + 2 + 1) = 1 (0 в ос- |

1 |

|

|

ке) |

татке) |

|

|

|

|

|

|

|

Во втором способе исходное число делится на сумму «весов»/значений разрядов (также в порядке убывания). Если сумма разрядов меньше исходного числа – к сумме прибавляется значение/вес следующего разряда, а если больше делимого, то результат деления обнуляется.

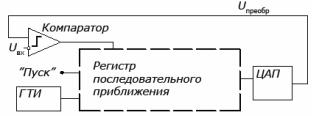

Рис. 1.13. Блок-схема АЦП с поразрядным уравновешиванием

Аналогичный 2-му способу алгоритм применяется для оцифровки аналогового сигнала. На рис. 1.13 представлена блок-схема, основным элементом которой является регистр последовательного приближения (РПП). РПП с каждым тактовым импульсом последовательно присваивает разрядам, начиная со старшего, значения «1». Так, для восьмиразрядного регистра первым двоичным числом будет 1000 0000. Если цифровой сигнал после преобразования в АЦП оказывается меньше аналогового, о чем будет свидетельствовать состояние компаратора, то «1» в текущем разряде сохраняется; в противном случае – заменяется на «0». Далее, при втором такто-

19