- •Л.С. Грошева, в.И. Плющаев

- •1. Архитектура систем управления и контроля

- •2. Аппаратная база для систем автоматического управления

- •2.1 Микроконтроллеры семейства mcs-51

- •Базовая архитектура микроконтроллеров семейства mcs-51

- •Блок управления

- •Блок счетчика команд

- •Арифметико-логическое устройство

- •Порты микроконтроллера

- •Внутренняя память данных.

- •Блок таймеров / счетчиков

- •Блок последовательного интерфейса

- •Блок прерываний

- •Система команд

- •2.2.Типовые периферийные устройства

- •3. Задание для контрольной работы

- •4. Пример выполнения контрольной работы

- •5. Задания для лабораторных работ

- •5.1 Обработка дискретной информации

- •5.2 Обработка аналоговой информации

- •Литература

- •Оглавление

- •Грошева Людмила Серафимовна Плющаев Валерий Иванович

- •Учебно-методическое пособие

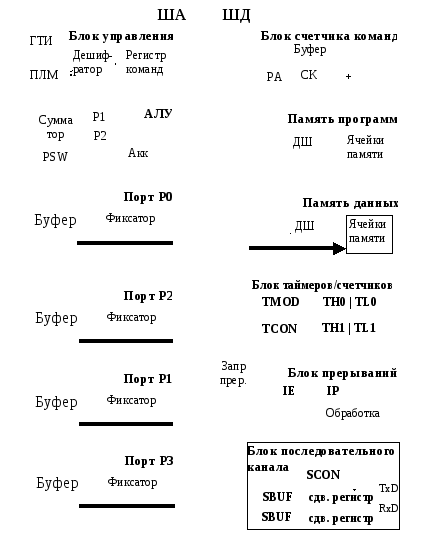

Базовая архитектура микроконтроллеров семейства mcs-51

Внутренняя структура микроконтроллера MCS-51 приведена на рис.2.

Блок управления предназначен для синхронизации работы всех блоков микроконтроллера, а также для приема, дешифрации кода команды и формирования управляющих воздействий для её выполнения.

Блок счетчика команд предназначен для хранения адреса очередного байта программы, а также формирования адреса для считывания кода из памяти программ с автоматическим увеличением адреса.

АЛУ (арифметико-логическое устройство) предназначено для выполнения арифметических, логических команд, команд сдвига и обнуления.

Порты Р0-Р3 предназначены для организации обмена данными между микроконтроллером и внешними устройствами. Кроме того, порты имеют специальные функции для обслуживания внутренних периферийных устройств, организации программирования внутренней памяти программ и реализации доступа к внешней памяти.

Память программ предназначена для хранения программного кода, в рабочем режиме доступна только для чтения, запись реализуется только в режиме программирования. Может быть реализована в виде ПЗУ или РПЗУ.

Память данных предназначена для хранения текущих данных, доступна для чтения и записи информации. Не сохраняет информацию при отключении питания.

Блок таймеров/счетчиков включает в свой состав два таймера/счетчика, регистр режимов TMOD и регистр управления TCON. Таймеры/счетчики предназначены для организации временных задержек, выполнения времязадающих функций и подсчета внешних событий.

Блок прерываний осуществляет обработку запросов прерываний в соответствии с настройками регистра разрешений IE и регистра управления приоритетностью прерываний IP.

Блок последовательного канала предназначен для организации приема и передачи информации в последовательном виде в соответствии с настройками регистра SCON.

Блок управления

Для формирования синхроимпульсов генератор тактовых импульсов, входящий в состав блока управления, использует сигналы с внешнего кварцевого генератора, подключенного к входам Х1 и Х2.

|

|

|

Рис.2.Внутренняя структура микроконтроллера MCS-51 |

В начале каждого цикла обращения к памяти программ блок управления формирует управляющие сигналы блоку счетчика команд для формирования адреса на шину адреса.

Затем считанный из памяти программ код команды по шине данных поступает в блок управления и записывается в регистр команд. После этого дешифратор преобразует восьмиразрядный код команды в 24-разрядный код для программируемой логической матрицы (ПЛМ), которая формирует управляющие сигналы для выполнения команды.

Блок счетчика команд

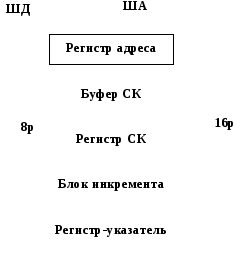

Структура блока счетчика команд приведена на рис.3

Регистр счетчика команд (СК) хранит адрес очередного байта программного кода.

При получении сигнала от блока управления содержимое регистра счетчика команд по внутренней 16-разрядной шине блока отправляется в регистр адреса, где хранится в течение цикла обращения к памяти и откуда выставляется на шину адреса микроконтроллера. Одновременно с этим содержимое регистра СК поступает в блок инкремента, увеличивается на 1, затем записывается обратно в регистр СК. Таким образом обеспечивается последовательное считывание программного кода из памяти программ.

|

|

|

Рис.3. Структура блока счетчика команд |

Буфер СК предназначен для согласования внутренней 16-разрядной шины блока и 8-разрядной шины данных микроконтроллера, используется при операциях чтения и записи содержимого регистра счетчика команд.

Регистр-указатель данных DPTR используется для формирования адреса внешней памяти данных.