- •Л.С. Грошева, в.И. Плющаев

- •1. Архитектура систем управления и контроля

- •2. Аппаратная база для систем автоматического управления

- •2.1 Микроконтроллеры семейства mcs-51

- •Базовая архитектура микроконтроллеров семейства mcs-51

- •Блок управления

- •Блок счетчика команд

- •Арифметико-логическое устройство

- •Порты микроконтроллера

- •Внутренняя память данных.

- •Блок таймеров / счетчиков

- •Блок последовательного интерфейса

- •Блок прерываний

- •Система команд

- •2.2.Типовые периферийные устройства

- •3. Задание для контрольной работы

- •4. Пример выполнения контрольной работы

- •5. Задания для лабораторных работ

- •5.1 Обработка дискретной информации

- •5.2 Обработка аналоговой информации

- •Литература

- •Оглавление

- •Грошева Людмила Серафимовна Плющаев Валерий Иванович

- •Учебно-методическое пособие

Внутренняя память данных.

Адресное пространство внутренней памяти данных складывается из 128 ячеек собственно ОЗУ и двадцати адресуемых регистров специального назначения, имеющих адреса со 128 по 255 (рис. 6 ).

|

|

|

Рис.6 Адресное пространство внутренней памяти данных. |

В ОЗУ размещается стек, используемый для хранения содержимого счетчика команд при вызове подпрограмм, а также для временного хранения данных. Глубина стека, определяемая восьмиразрядным указателем стека SP, ограничена только объемом внутреннего ОЗУ.

Первые 32 ячейки ОЗУ разбиты на 4 банка по 8 ячеек в каждом - регистры общего назначения. В каждом банке регистры имеют собственные имена, соответственно R0-R7.

Выбор нужного банка регистров осуществляется программно. Номер банка задается разрядами PSW.3 и PSW.4 регистра PSW.

Структура ОЗУ позволяет работать не только с отдельными ячейками памяти (байтовая адресация), но и с отдельными битами (побитовая адресация). Прямоадресуемые биты с адресами 0 – 127 (0 – 7FH) расположены в блоке из 32 ячеек внутреннего ОЗУ, имеющих адреса 20Н – 2FH.

Таким же образом можно работать с регистрами специального назначения. Адреса и названия регистров специального назначения указаны на рис.3.

Команды, оперирующие с битами, позволяют каждый бит установить в 1, сбросить в 0, проинвертировать и протестировать, организовать переходы по состоянию любого бита, реализовать побитные логические операции и т.п. Такая архитектура позволяет реализовывать оптимальные по объему и быстродействию программы.

Блок таймеров / счетчиков

Два 16-разрядных регистра (ТН0,TL0) и (TH1,TL1) выполняют функцию считающих элементов. Регистры TH0,TH1 – старшие, TL0, TL1 – младшие 8 разрядов 16-разрядных регистров. Каждый из 8-разрядных регистров имеет свой адрес и может использоваться как регистр общего назначения (РОН), если таймер/счетчики не используются.

Управление работой таймеров/счетчиков осуществляется с помощью регистров специального назначения – регистра режимов TMOD и регистра управления TCON, а также схемы управления.

Число, с которого начинается счет, заносится в регистры таймеров/счетчиков программно. В процессе счета содержимое регистров Т/С0 и Т/С1 инкрементируется. При переполнении регистров Т/С0 и Т/С1 (переход от состояния «все единицы» к состоянию «все нули») формируется флаг переполнения.

При работе в качестве таймера, содержимое Т/С0 и Т/С1 инкрементируется каждый машинный цикл, т.е. частота счета равна fQ/12 , где fQ – частота тактового генератора.

При работе Т/С0 и Т/С1 в качестве счетчиков внешних событий (сигналы поступают на входы Р3.4 и Р3.5) , содержимое счетчиков инкрементируется при переходе из «1» в «0» сигналов на счетных входах.

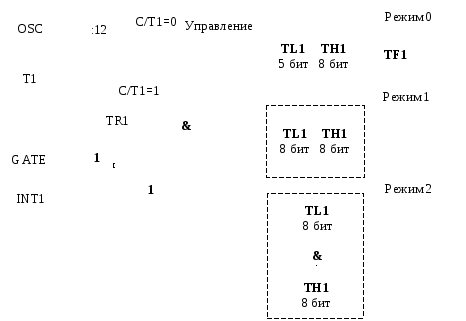

Логика работы таймера счетчика в режимах 0,1,2 приведена на рис.7.

|

|

|

Рис.7. Логика работы таймеров/счетчиков в режимах 0, 1 и 2. |

Регистр режимов TMOD определяет:

режим работы каждого таймера/счетчика – используемую разрядность считающего элемента;

источник импульсов для счета – работу в качестве таймера или счетчика;

разрешение управления запуском таймера / счетчика от внешнего входа.

Назначение разрядов регистра TMOD приведено в таблице 1. Биты 0-3 относятся к Т/С0,биты 4-7 – к Т/С1.

Табица.1

|

Биты |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

Обозн. |

GATE1 |

C/T1 |

M1.1 |

M0.1 |

GATE0 |

C/T0 |

M1.0 |

M0.0 |

Назначение битов М0,М1 (режим работы, отдельно для Т/С1 и Т/С0):

М1, М0=00 (режим 0), используется 13-разрядный считающий элемент 8рTH0+5рTL0;

М1, М0=01 (режим 1), используется 16-разрядный считающий элемент 8рTH0+8рTL0;

М1, М0=10 (режим 2), используется 8-разрядный считающий элемент TL0. TH0 хранит константу перезагрузки. При переполнении TL0 автоматически перезагружается;

М1, М0=11 (режим 3), для Т/С1 не используется. Т/С0 работает как два независимых 8-разрядных счетчика TH0 и TL0.

Биты С/Т0,С/Т1 определяют работу в качестве таймера (С/Т0 или С/Т1 = 0) или счетчика (С/Т0 или С/Т1 = 1).

Бит GATE разрешает управлять таймером от внешнего вывода INT0 – для Т/С0, INT1 – для Т/С1. Если GATE = 0 – управление запрещено;GATE = 1 – управление разрешено.

Регистр управления ТCON предназначен для приема и хранения управляющего слова. Обозначение и назначение разрядов регистра приведено в табл. 2.

Таблица 2

|

Биты |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

Обозн. |

TF1 |

TR1 |

TF0 |

TR0 |

IE1 |

IT1 |

IE0 |

IT0 |

Назначение битов:

TR0, TR1 – биты включения Т/С, отдельно для Т/С0 и Т/С1. Если TR = 0 - выключен, TR = 1 – включен. Биты устанавливаются и сбрасываются программно

TF0, TF1 – флаги переполнения Т/С. Биты сбрасываются и устанавливаются аппаратно и программно.

IT0, IT1 – биты, определяющие вид прерывания по входам INT0, INT1. IT=0 – прерывание по уровню (низкому); IT = 1 – прерывание по фронту (переход из «1» в «0»). Биты устанавливаются и сбрасываются программно.

IE0, IE1 – флаги запроса внешних прерываний по входам INT0, INT1 Биты сбрасываются и устанавливаются аппаратно и программно.

Все биты регистра ТCON доступны по чтению. Биты 4,5 относятся к Т/С0,биты 6,7 – к Т/С1.Биты 0,1 определяют внешние прерывания по входу INT0, биты 2,3 – по входу INT1.

Т/С1 аппаратно связан с блоком синхронизации последовательного интерфейса (ПИ), он используется для управления скоростью приема/передачи последовательных данных.