- •Л.С. Грошева, в.И. Плющаев

- •1. Архитектура систем управления и контроля

- •2. Аппаратная база для систем автоматического управления

- •2.1 Микроконтроллеры семейства mcs-51

- •Базовая архитектура микроконтроллеров семейства mcs-51

- •Блок управления

- •Блок счетчика команд

- •Арифметико-логическое устройство

- •Порты микроконтроллера

- •Внутренняя память данных.

- •Блок таймеров / счетчиков

- •Блок последовательного интерфейса

- •Блок прерываний

- •Система команд

- •2.2.Типовые периферийные устройства

- •3. Задание для контрольной работы

- •4. Пример выполнения контрольной работы

- •5. Задания для лабораторных работ

- •5.1 Обработка дискретной информации

- •5.2 Обработка аналоговой информации

- •Литература

- •Оглавление

- •Грошева Людмила Серафимовна Плющаев Валерий Иванович

- •Учебно-методическое пособие

Арифметико-логическое устройство

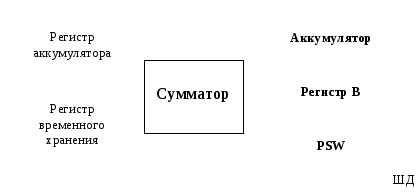

Структура арифметико-логического устройства приведена на рис.4.

Выполнение всех арифметических и логических операций осуществляется в сумматоре, в который подаются операнды из регистра аккумулятора и регистра временного хранения. Один из операндов операции поступает из аккумулятора, а второй из регистра или ячейки памяти по шине данных.

Результат арифметической или логической операции записывается в аккумулятор, в случае команд умножения также в регистр В (старшая часть), при делении в регистр В записывается остаток.

По результатам выполненной операции формируются признаки результата и записываются в слово состояния программы PSW. К признакам относятся такие флаги как Z – признак равенства нулю, С – разряд переноса и др. Кроме того, разряды RS0 и RS1 (PSW.3 и PSW.4) обеспечивают переключение банка регистров общего назначения.

|

|

|

Рис.4. Структура арифметико-логического устройства

|

Порты микроконтроллера

Порты Р0-Р3 могут работать как независимые порты ввода/вывода. Непосредственно к линиям портов могут подключаться периферийные устройства (регистры, некоторые элементы индикации и т.п.). Каждая линия может быть использована как для ввода, так и для вывода информации под управлением программного обеспечения. При подключении следует учитывать нагрузочную способность линий, т.е. величину тока, который может обеспечить микросхема в нагрузке. Для рассматриваемой микросхемы выходной ток линий составляет единицы миллиампер. Поэтому подключение более мощных потребителей необходимо производить через буферные схемы (например, микросхемы 1102АП5,6 обеспечивают выходной ток до 300 мА, регистр 580ВА86 – до 32 мА и т.д.).

При размещении управляющей программы во внутренней памяти программ и использовании портов для подключения периферийных устройств можно создавать очень компактные устройства управления и сбора информации с широкими функциональными возможностями.

Кроме того, все порты имеют целый ряд дополнительных функций.

Порт Р0 (Р0.0-Р0.7):

при работе с внешней памятью программ или данных в начале цикла обращения через Р0 выводятся младшие разряды адреса, затем по этим линиям передается байт данных;

при программировании микросхемы (записи программы во внутреннюю память программ) и проверке через линии порта Р0 производится чтение/запись данных.

Порт Р1 (Р1.0-Р1.7):

используется для передачи младших разрядов адреса при программировании и проверке микросхемы.

Порт Р2 (Р2.0-Р2.7):

используется для передачи старших разрядов адреса при работе с внешней памятью программ и внешней памятью данных;

при программировании микросхемы (записи программы во внутреннюю память программ) и проверке через линии порта Р2 производится передача старших разрядов адреса и управляющих сигналов.

Порт Р3 (Р3.0-Р3.7). Линии порта Р3 могут быть использованы для передачи сигналов управления:

RxD (линия Р3.0) - передача информации в последовательном коде;

TxD (линия Р3.1) - прием информации в последовательном коде;

INT0 (линия Р3.2) - вход внешнего сигнала прерывания 0;

INT1 (линия Р3.3) - вход внешнего сигнала прерывания 1;

Т0 (линия Р3.4) – вход таймера/счетчика 0 ;

Т1 (линия Р3.5) вход таймера/счетчика 1;

WR (линия Р3.6) – сигнал ЗАПИСЬ. Формируется при передаче байта информации через порт Р0 во внешнюю память данных;

RD (линия Р3.7) – сигнал ЧТЕНИЕ. Формируется при считывании байта через порт Р0 из внешней памяти данных.

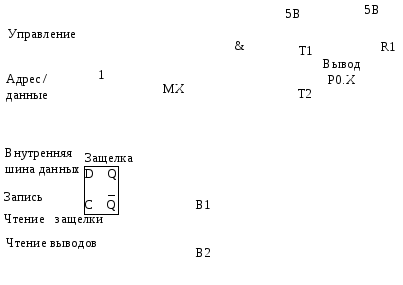

Структура разряда порта представлена на рис.5. Здесь видно, что выходные каскады порта (образованы транзисторами Т1 и Т2) через мультиплексор МХ могут подключаться либо к выходу защелок, либо к внутренним шинам Адрес/данные.

|

|

|

Рис.5. Структура разряда порта P0

|

При обращении к внешней памяти по линии Управление поступает 1, ключ мультиплексора замыкается вверх, вывод Р0.Х определяется состоянием линии Адрес/данные (при 1 открывается транзистор Т1, при 0 – транзистор Т2).

В режиме ввода/вывода общего назначения по линии Управление поступает 0, ключ мультиплексора МХ замкнут вниз, управление Т1 недоступно.

В режиме ввода через буфер В1 или В2 можно прочитать состояние защелки или внешнего вывода. Устройство чтения определяется типом используемой команды.

В режиме вывода при выдаче в защелку состояния 0, открывается транзистор Т2 и на выводе Р0.Х состояние 0.

Для формирования на выводе состояния 1, необходимо использовать внешний подтягивающий резистор R1, тогда при закрытии транзистора Т2 вывод Р0.Х примет состояние 1.