- •ГЕОФИЗИЧЕСКИЙ ФАКУЛЬТЕТ

- •ПРАКТИКУМ ПО КУРСУ

- •УЧЕБНОЕ ПОСОБИЕ

- •ВВЕДЕНИЕ

- •ЗАДАНИЕ 1

- •ЗАДАНИЕ 2

- •ЗАДАНИЕ 3

- •ЗАДАНИЕ 4

- •ЗАДАНИЕ 5

- •ЗАДАНИЕ 6

- •СПРАВОЧНИК Управление данными

- •ЗАДАНИЕ 7

- •СПРАВОЧНИК Финансовые функции

- •ЗАДАНИЕ 8

- •ЗАДАНИЕ 9

- •ЗАДАНИЕ 1

- •ЗАДАНИЕ 2

- •ЗАДАНИЕ 3

- •ЗАДАНИЕ 4

- •ЗАДАНИЕ 5

- •ЗАДАНИЕ 6

- •СИСТЕМА УПРАВЛЕНИЯ БАЗАМИ ДАННЫХ ACCESS

- •ЗАДАНИЕ 2

- •ТЕОРЕТИЧЕСКИЙ МАТЕРИАЛ

- •ЭЛЕКТРОННЫЕ ТАБЛИЦЫ

- •АЛГОРИТМ. СВОЙСТВА АЛГОРИТМОВ.

- •ЭТАПЫ РЕШЕНИЯ ЗАДАЧ НА КОМПЬЮТЕРЕ

- •ТЕХНОЛОГИИ ПРОГРАММИРОВАНИЯ

- •СТРУКТУРНОЕ ПРОГРАММИРОВАНИЕ

- •ОБЪЕКТНО-ОРИЕНТИРОВАННОЕ ПРОГРАММИРОВАНИЕ

- •ФУНКЦИОНАЛЬНОЕ ПРОГРАММИРОВАНИЕ

- •ЯЗЫКИ ПРОГРАММИРОВАНИЯ. КОМПИЛЯЦИЯ И ИНТЕРПРЕТАЦИЯ.

- •КЛАССИФИКАЦИЯ ЯЗЫКОВ ПРОГРАММИРОВНИЯ

- •ПРОГРАММИРОВАНИЕ НА ЯЗЫКЕ Visual Basic for Application (VBA)

- •ТИПЫ АЛГОРИТМОВ И ИХ РЕАЛИЗАЦИЯ НА VBA

- •АЛГЕБРА ЛОГИКИ. ЛОГИЧЕСКИЕ ФУНКЦИИ. БАЗОВЫЕ ЛОГИЧЕСКИЕ ОПЕРАЦИИ.

- •ОСНОВНЫЕ ЗАКОНЫ АЛГЕБРЫ ЛОГИКИ. ПРЕОБРАЗОВАНИЕ ЛОГИЧЕСКИХ ФУНКЦИИ.

- •ОСНОВНЫЕ ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

- •ОСНОВНЫЕ ЛОГИЧЕСКИЕ УСТРОЙСТВА КОМПЬЮТЕРА - СУММАТОР

- •ОСНОВНЫЕ ЛОГИЧЕСКИЕ УСТРОЙСТВА КОМПЬЮТЕРА - ТРИГГЕР

- •СИСТЕМА УПРАВЛЕНИЯ БАЗАМИ ДАННЫХ (СУБД). НАЗНАЧЕНИЕ И ОСНОВНЫЕ ВОЗМОЖНОСТИ.

- •ВОПРОСЫ ДЛЯ ПОДГОТОВКИ К ЭКЗАМЕНУ.

- •СПИСОК ЛИТЕРАТУРЫ

ОСНОВНЫЕ ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ

Базовые логические элементы.

Базовые логические элементы реализуют три основные логические операции.

Логический элемент «И» - логическое умножение. Логический элемент «ИЛИ» - логическое сложение. Логический элемент «НЕ» - инверсию.

Поскольку любая логическая операция может быть представлена в виде комбинации трех основных, любые устройства компьютера, позволяющие вести обработку или хранение информации, могут быть собраны из базовых логических элементов как из кирпичиков.

Логические элементы компьютера оперируют с сигналами, представляющими собой электрические импульсы. Есть импульс - логическое значение сигнала 1, нет импульса - значение 0. На вход логических элементов поступают сигналы-аргументы, на выходе появляется сигнал-функция.

Преобразование сигнала логическим элементом задается таблицей состояния, которая фактически является таблицей истинности, соответствующей логической функции.

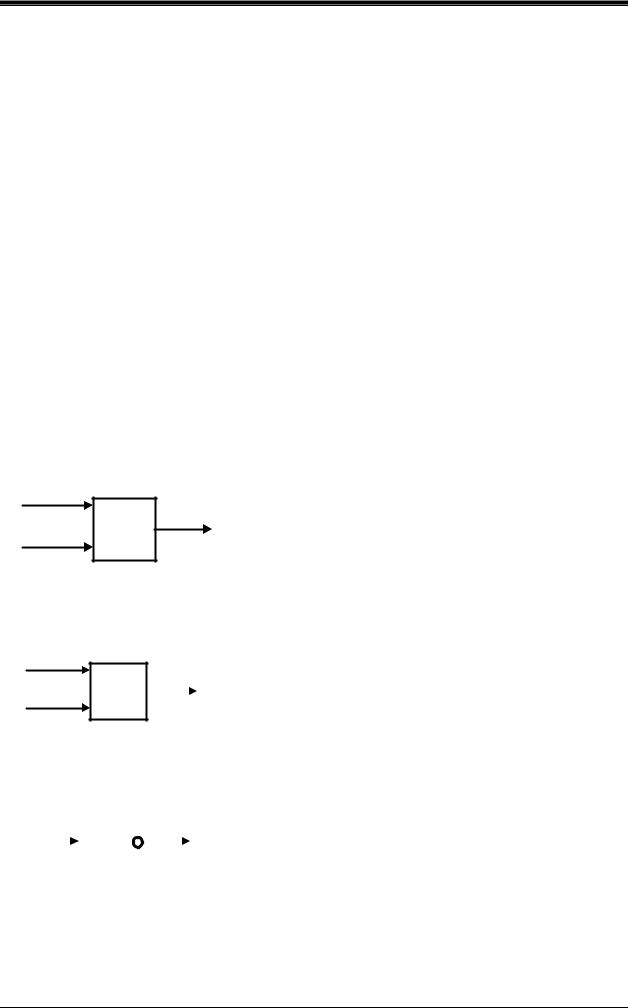

Логические элемент «И».

A (0,0,1,1)

&F (0,0,0,1)

B (0,1,0,1)

Обозначение этого элемента на логических схемах:

«И» - «&».

Логические элемент «ИЛИ».

A (0,0,1,1)

1 |

F (0,1,1,1) |

|

|

|

|

|

|

|

B (0,1,0,1)

Обозначение этого элемента на логических схемах:

«ИЛИ» - «1» «V».

Логические элемент «НЕ».

A (0,1) |

|

F (1,0) |

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

Обозначение: «НЕ» - «1» с кружочком на выходе.

На входы А и В логического элемента последовательно подаются четыре пары сигналов различных значений, на выходе получается последовательность из четырех сигналов, значения которых определяются в соответствии с таблицей истинности операции логического умножения.

На входы А и В логического элемента последовательно подаются четыре пары сигналов различных значений, на выходе получается последовательность из четырех сигналов, значения которых определяются в соответствии с таблицей истинности операции логического сложения.

На вход А логического элемента последовательно подаются два сигнала, на выходе получается последовательность из двух сигналов, значение которых определяются в соответствии с таблицей истинности логической инверсии.

108

Очень часто используются комбинированные логические элементы,

сформированные из элементов «И» и «ИЛИ» с отрицанием. Они называются функцией Шеффера – «И-НЕ» и функцией Пирса – «ИЛИ-НЕ».

Они также обладают свойством функциональной полноты.

Функция Шеффера: |

|

|

Функция Пирса: |

|

|

||||||

|

A (0,0,1,1) |

|

F (1,1,1,0) |

|

A (0,0,1,1) |

|

F (1,0,0,0) |

||||

|

|

|

& |

|

|

|

1 |

||||

|

B (0,1,0,1) |

|

|

|

B (0,1,0,1) |

|

|

||||

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Тестовые задания Задание 1

Данной схеме соответствует логическая функция ...

1.

2.

3.

4.

Задание 2

На входе логической схемы при F=1 возможна следующая комбинация сигналов (А, В, С, D) …

(1 1 0 0)

1(1 0 1 0)

2(1 1 1 0)

3(0 1 1 0)

ОСНОВНЫЕ ЛОГИЧЕСКИЕ УСТРОЙСТВА КОМПЬЮТЕРА - СУММАТОР

Сумматор двоичных чисел.

В целях максимального упрощения работы компьютера все многообразие математических операций в процессоре сводится к сложению двоич-

ных чисел. Поэтому главной частью процессора является сумматор, который и обеспечивает такое сложение.

Полусумматор. При сложении двоичных чисел образуется сумма, при этом возможен перенос в старший разряд. Обозначим слагаемые (А, В), перенос

109

(Р) и сумму (S). Таблица сложения одноразрядных двоичных чисел с учетом переноса в старший разряд выглядит следующим образом:

|

Слагаемые |

Перенос |

Сумма |

|

А |

|

В |

Р= А & В |

S=(A v B) & NOT(A&B) |

|

|

|

|

|

0 |

|

0 |

0 |

0 |

0 |

|

1 |

0 |

1 |

1 |

|

0 |

0 |

1 |

1 |

|

1 |

1 |

0 |

Из этой таблицы видно, что перенос можно реализовать с помощью операции логического умножения,

Р = А & В.

Получим теперь формулу для вычисления суммы. Значения суммы более всего совпадают с результатом операции логического сложения (кроме случая, когда на вход подаются две единицы, а на выходе должен получится нуль).

Нужный результат достигается, если результат логического сложения умножить на инвертированный перенос. Таким образом, для определения суммы можно применить следующее выражение:

S = (AVB) & NOT(A&B)

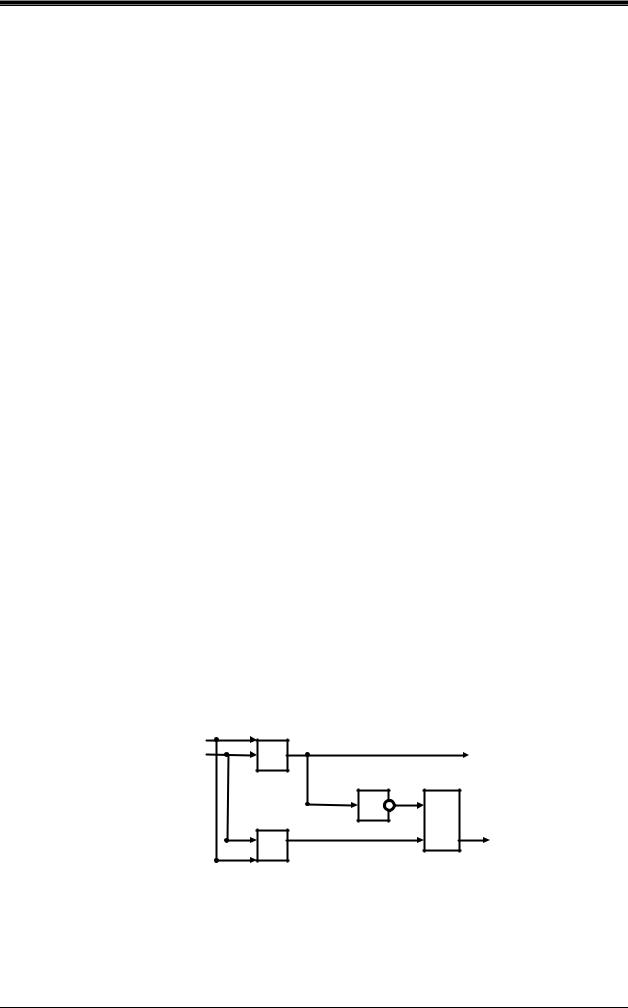

Теперь, на основе полученных логических выражений, можно построить из базовых логических элементов схему полусумматора.

По логической формуле переноса легко определить, что для получения переноса необходимо использовать логический элемент «И».

Анализ логической формулы для суммы показывает, что на выходе должен стоять элемент логического умножения «И», который имеет два входа. На один из входов подается результат логического сложения исходных величин

A v B , т. е. на него должен подаваться сигнал с элемента логического сложения «ИЛИ».

На второй вход требуется подать результат инвертированного логического умножения исходных сигналов А & В, то есть на второй вход подается сигнал с элемента «НЕ», на вход которого подан сигнал с элемента логического умножения «И».

A (0,0,1,1)

P (0,0,0,1)

&

B (0,1,0,1)

1

& S (0,1,1,0,)

1

Данная схема, называется полусумматором, так как реализует суммирование одноразрядных двоичных чисел без учета переноса из младшего разряда.

Полный одноразрядный сумматор. Полный одноразрядный сумматор должен иметь три входа, А, В - слагаемые и Р0 - перенос из предыдущего

110

разряда и два выхода, сумма S и перенос Р. Таблица сложения в этом случае будет иметь следующий вид:

А |

В |

Р0 |

Р |

S |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

Идея построения полного сумматора точно такая же, как и полусумматора. Перенос реализуется с помощью формулы для получения переноса:

P = (A & B) v (A & P0) v (B & P0)

Логическое выражение для вычисления суммы в полном сумматоре принимает следующий вид:

S = (A v B v P0) & NOT(P0) v (A & B & P0)

Многоразрядный сумматор процессора состоит из полных одноразрядных сумматоров. На каждый разряд ставится одноразрядный сумматор, причем выход (перенос) сумматора младшего разряда подключен к входу сумматора старшего разряда.

ОСНОВНЫЕ ЛОГИЧЕСКИЕ УСТРОЙСТВА КОМПЬЮТЕРА - ТРИГГЕР

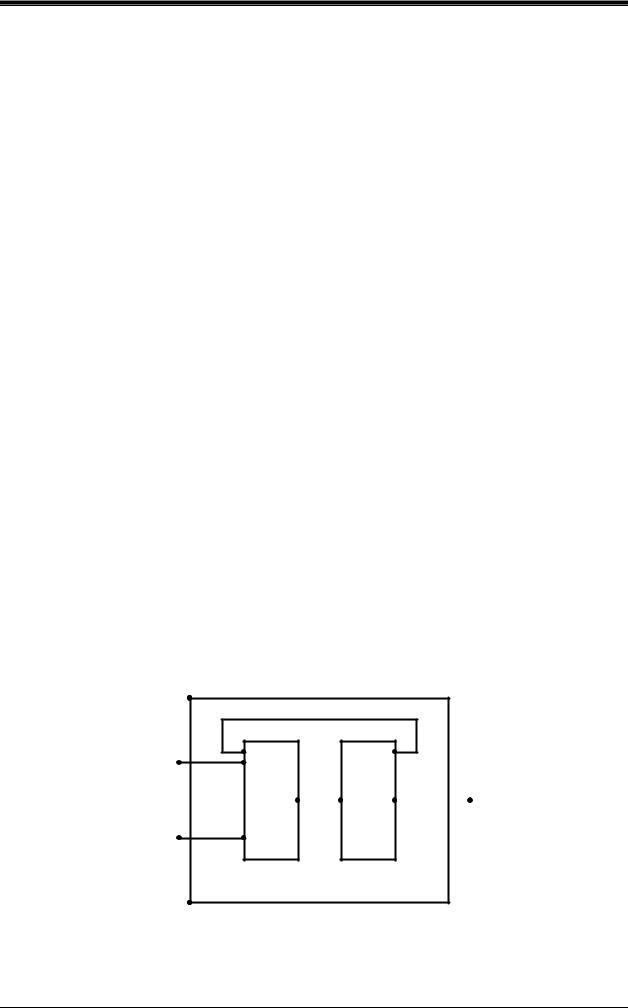

Важнейшей структурной единицей оперативной памяти компьютера, а также внутренних регистров процессора является триггер. Это устройство позволяет запоминать, хранить и считывать информацию (каждый триггер может хранить 1 бит информации).

Триггер имеет 2 состояния.

Импульс для триггера - изменение потенциала на входе.

Х1

Входная |

|

Запомина- |

|

|

|

ющая ячейка |

|

||

логическая |

|

У |

||

|

|

|

||

|

|

|

||

схема |

|

|

|

|

Хn

На информационные входы подаются 0 или 1, которые соответствуют тому, в какое состояние должен быть переведен триггер.

111

Установочные сигналы: S - 1, R - 0, поэтому триггер называют RSтриггер (так называется только простейший рассматриваемый нами триггер, а вообще триггеров очень много).

На выходе будем рассматривать 2 состояния Qn и Qn+i (прошел триггер за

Δt).

S |

R |

Qn |

Qn+i |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

Запрещенная ситуа- |

|

В обычном состоянии на входы триггера подан сигнал «0», и триггер хранит «0». Для записи «1» на вход S (установочный) подается сигнал «1». Последовательно рассмотрев прохождение сигнала по схеме, видно, что триггер переходит в это состояние и будет устойчиво находиться в нем и после того, как сигнал на входе S исчезнет. Триггер запомнил «1», т.е. с выхода триггера Q можно считать «1».

Для того чтобы сбросить информацию и подготовиться к приему новой, подается сигнал «1» на вход R (сброс), после чего триггер возвратится к исходному "нулевому" состоянию.

Триггер можно построить из двух логических элементов «ИЛИ» и ДВУХ элементов «НЕ».

|

|

|

|

|

0 |

|

|

S(1) |

1 |

1 |

1 |

||||

|

|

|

|

|

|

||

0 |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

1 |

|

|

|

|

1 |

1 |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

Q |

|||

|

|

|

|

|

|

||

R |

|

|

|||||

|

|

|

|

||||

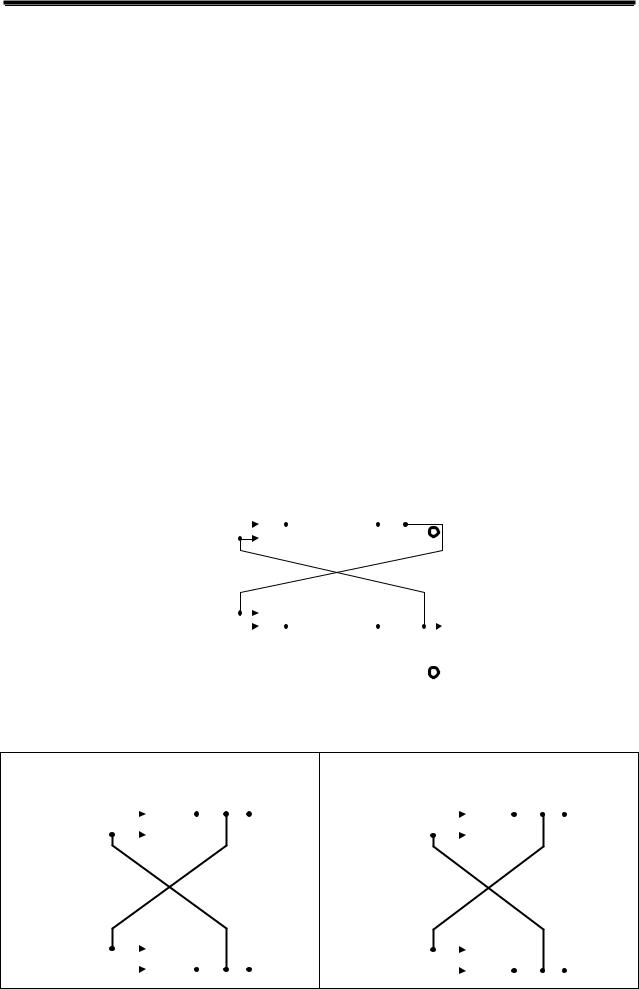

Также RS-триггер можно построить на элементах Шеффера и на элементах Пирса. При этом происходит существенная экономия материалов и упрощение схемы. Обозначение R, S и Q указывает на то, что это инверсный сигнал (противоположный).

На элементах Шеффера |

|

На элементах Пирса |

|

|||||||||

|

R |

Q |

|

R |

Q |

|||||||

|

|

|

|

& |

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

S |

|

|

& |

|

Q |

S |

|

1 |

|

Q |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

112