- •1. Основные понятия и определения мпс

- •2. Понятие об архитектуре мп. Классификация мп.

- •3.Обобщенная структура мп. Назначение элементов структуры.

- •4.Рабочий цикл мп. (цикл фон-Неймана).

- •8. Структурная схема к580вм80, назначение элементов

- •7. Уго к580вм80, назначение выводов

- •33) Алгоритм функционирования к580вм80

- •12. Организация памяти мпс.

- •11. Организация обмена информацией в мпс на базе к580вм80

- •10. Структура мпс на базе к580вм80, организация шин

- •9 Программная модель мп кр580вм80а имеет вид:

- •14 Режимы адресации к580вм80

- •13. Система команд микропроцессора к580.

- •15. Методика записи программ на ассемблере.

- •16. Структурная схема к1810вм86

- •17. Программная модель к1810вм86.

- •18. Сегментация памяти к1810вм86, методы адресации

- •1) Основные понятия и определения мпс

- •6. Режимы обмена в мпс

- •19. Уго к1810вм86, назначение выводов

- •20. Режимы обмена к1810вм86мк

- •21.Структура микроконтроллера atmel avr

- •23.Система команд, режимы адресации аа

- •24. Схемы портов ввода-вывода мк(в общем)

- •1.2.3. Двунаправленный порт ввода-вывода

- •1.2.4. Квазидвунаправленный порт ввода-вывода

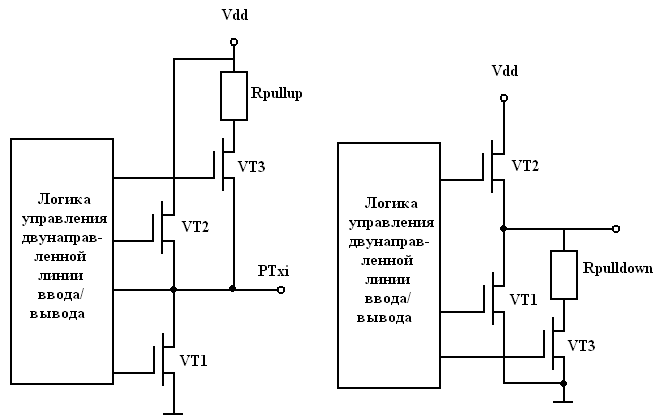

- •1.2.5. Двунаправленный порт ввода-вывода с программным подключением «подтягивающих» резисторов

- •25. Схема порта аа

- •26. Назначение, структура и работа таймеров-счетчиков (в общем виде)

- •27. Схема работы и управление таймеров-счетчиков т0 аа

- •28. Генераторы шим сигналов на таймерах аа

- •29. Классификация последовательных интерфейсов

- •30. Организация последовательного интерфейса rs-232, формат кадра и управление последовательным интерфейсом в Atmel avr

- •31. Средства программно-аппаратной поддержки для разработки программ для Atmel avr

- •32. Структура программы мк Atmel avr

24. Схемы портов ввода-вывода мк(в общем)

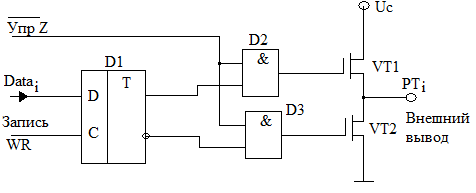

Однонаправленный порт вывода (двухтактный)

Основным элементом линии вывода будет D-триггер D1.

Если сигнал УпрZ = 1 и в триггер записан «0», открывается транзистор VT2, VT1 – закрыт. Запись в триггер происходит по синхросигналу «Запись» WR. На внешнем выводе PTi устанавливается низкий потенциал логического «0». Если в триггер записана «1», открывается транзистор VT1, VT2 – закрыт. На внешнем выводе PTi устанавливается высокий потенциал логической «1». Состояние триггера D1 и вывода сохраняется до следующей команды записи в триггер (при УпрZ = 1). Чтобы избежать встречного включения разных выводов, вывод можно перевести в Z-состояние, (УпрZ = 0).

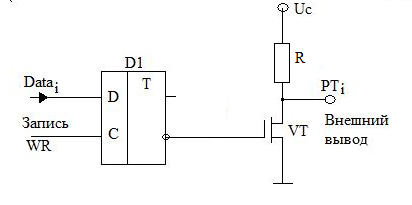

1.2.2. Однонаправленный порт вывода (однотактный)

На входе триг «1», на инверсном выходе логический «0», транзистор VT заперт, и внешний вывод питается от шины Uc через резистор. Имеем логическую «1» на выходе. На входе триг. «0», транзистор VT открывается и на выходе устанавливается также сигнал логического «0». Резистор выступает в качестве нагрузки для цепи питания. Высокое сопротивление резистора позволяет соединять несколько выходов (монтажное И), не опасаясь их встречного включения. Недостаток - низкая нагрузочная способность, или мощная нагрузка должна включаться нулем на выходе.

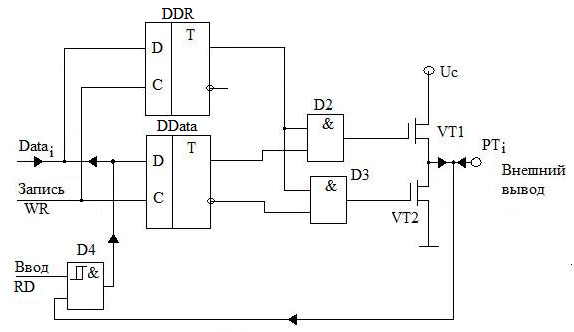

1.2.3. Двунаправленный порт ввода-вывода

Сигнал проходит через элемент D4, вход которого имеет гистерезисную характеристику (триггер Шмитта). Это способствует более четкому формированию логических уровней и подавлению дребезга и сигналов помех с амплитудой, меньшей ширины зоны гистерезиса.

Выведенная информация (открытый транзистор VT1 или VT2) будет препятствовать вводу сигнала противоположного значения. Поэтому для режима ввода надо перевести выход в Z-состояние, используется триггер DDR (Data DiRection). Записав в него логический «0», мы переводим выход в Z-состояние, то есть подготавливаем его для ввода. Записав логическую «1», мы открываем D2, D3 и переходим в режим вывода. Данная схема требует предварительной инициализации

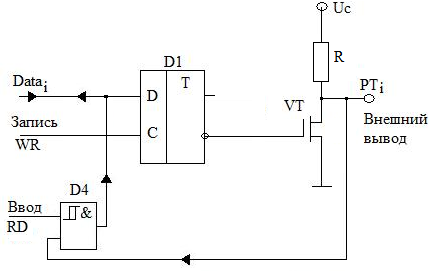

1.2.4. Квазидвунаправленный порт ввода-вывода

Не требуют предварительной инициализации. При вводе информации выполняется логическая операция И над вводимыми данными и последними выведенными. Если мы выведем (запишем в триггер D1) логическую «1», на инверсном выходе триггера будет «0», транзистор VT будет заперт, и на выходе PTi через резистор будет формироваться логическая «слабая 1», которая не помешает нам, подав извне сигнал логических «1» или «0», установить соответствующий сигнал на внешнем выводе и прочитать его по команде RD.

Если же мы выведем «0», то будет открыт транзистор VT, на выходе устанавливается так называемый «активный 0, который мы не можем, подав извне «1», перевести в состояние «1» Следовательно, мы не можем прочитать внешние сигналы. Вывод: для организации возможности ввода через соответствующий разряд порта через него следует предварительно вывести логическую «1».

1.2.5. Двунаправленный порт ввода-вывода с программным подключением «подтягивающих» резисторов

В режиме ввода выходные транзисторы закрыты, буфер находится в высокоомном состоянии (Z-состояние). Значение, которое будет возвращать операция чтения неподключенного входа, в общем случае не определено и под действием помех может изменяться, вызывая увеличение потребляемой энергии.

С тандартным

способом доопределения состояния входа

является подключение «подтягивающего

к 1» резистора (RPULLUP),

который обеспечивает уровень логической

«1» на входе или подключение «подтягивающего

к 0» резистора (RPULLDOWN),

который обеспечит уровень логического

«0» (рис. 6). Возможны схемы, где присутствуют

оба варианта подтяжки (и к «0», и к «1»),

с программным выбором одного.

тандартным

способом доопределения состояния входа

является подключение «подтягивающего

к 1» резистора (RPULLUP),

который обеспечивает уровень логической

«1» на входе или подключение «подтягивающего

к 0» резистора (RPULLDOWN),

который обеспечит уровень логического

«0» (рис. 6). Возможны схемы, где присутствуют

оба варианта подтяжки (и к «0», и к «1»),

с программным выбором одного.