- •1. Основные понятия и определения мпс

- •2. Понятие об архитектуре мп. Классификация мп.

- •3.Обобщенная структура мп. Назначение элементов структуры.

- •4.Рабочий цикл мп. (цикл фон-Неймана).

- •8. Структурная схема к580вм80, назначение элементов

- •7. Уго к580вм80, назначение выводов

- •33) Алгоритм функционирования к580вм80

- •12. Организация памяти мпс.

- •11. Организация обмена информацией в мпс на базе к580вм80

- •10. Структура мпс на базе к580вм80, организация шин

- •9 Программная модель мп кр580вм80а имеет вид:

- •14 Режимы адресации к580вм80

- •13. Система команд микропроцессора к580.

- •15. Методика записи программ на ассемблере.

- •16. Структурная схема к1810вм86

- •17. Программная модель к1810вм86.

- •18. Сегментация памяти к1810вм86, методы адресации

- •1) Основные понятия и определения мпс

- •6. Режимы обмена в мпс

- •19. Уго к1810вм86, назначение выводов

- •20. Режимы обмена к1810вм86мк

- •21.Структура микроконтроллера atmel avr

- •23.Система команд, режимы адресации аа

- •24. Схемы портов ввода-вывода мк(в общем)

- •1.2.3. Двунаправленный порт ввода-вывода

- •1.2.4. Квазидвунаправленный порт ввода-вывода

- •1.2.5. Двунаправленный порт ввода-вывода с программным подключением «подтягивающих» резисторов

- •25. Схема порта аа

- •26. Назначение, структура и работа таймеров-счетчиков (в общем виде)

- •27. Схема работы и управление таймеров-счетчиков т0 аа

- •28. Генераторы шим сигналов на таймерах аа

- •29. Классификация последовательных интерфейсов

- •30. Организация последовательного интерфейса rs-232, формат кадра и управление последовательным интерфейсом в Atmel avr

- •31. Средства программно-аппаратной поддержки для разработки программ для Atmel avr

- •32. Структура программы мк Atmel avr

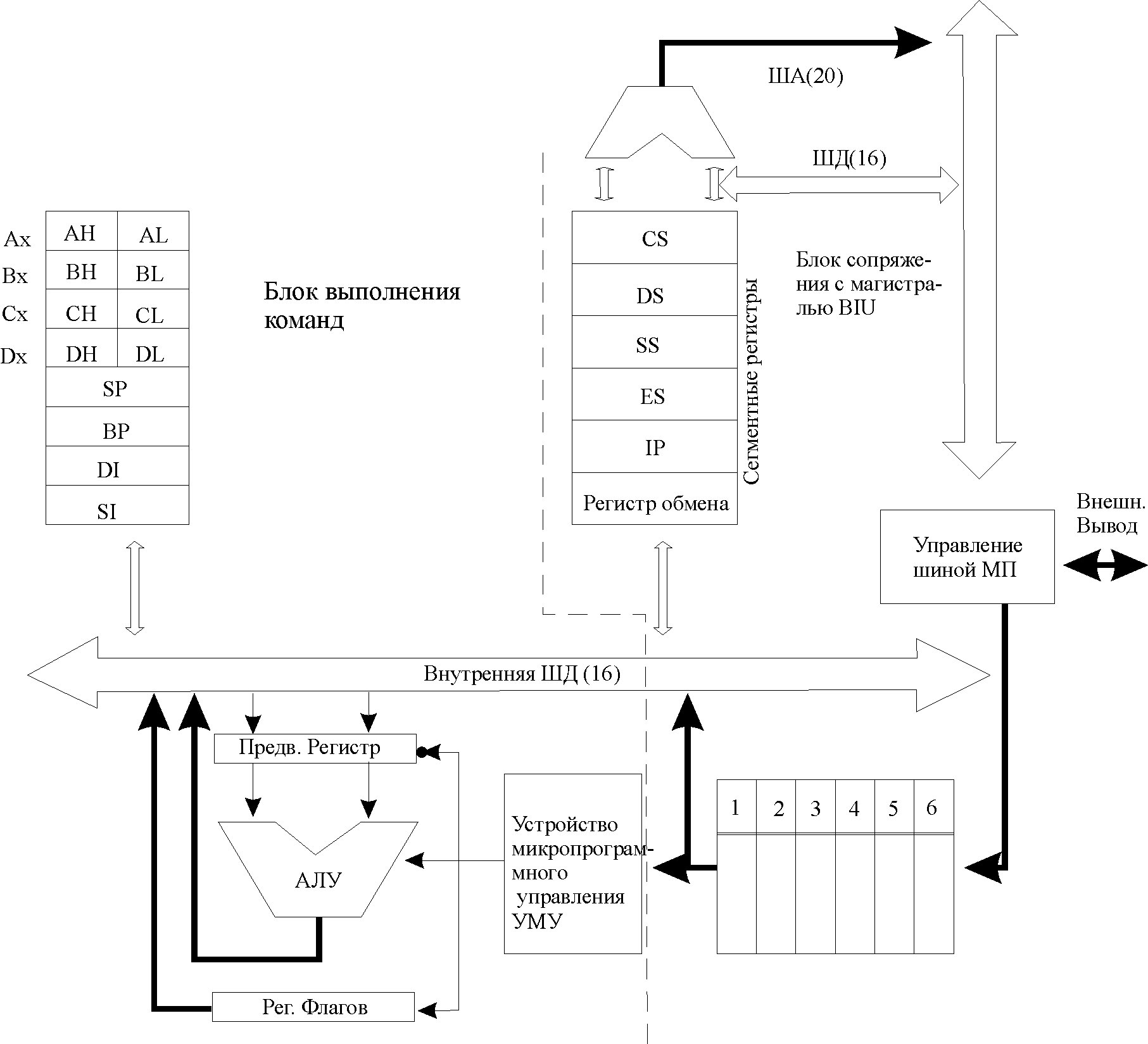

16. Структурная схема к1810вм86

Представляет собой однокристальный МП с 16 разрядной ШД, 20 разрядной шиной данных и позволяет работать с памятью до 1 Мб. Команды INT и OUT могут иметь адрес в 1 или 2 байта, что позволяет адресовать до 64 Кб регистров внешних устройств. Основные отличия:

для повышения быстродействия введен конвейер команд с предварительной выборкой.

Процессор разбит на 2 блока:

а) блок сопряжения с магистралью BIU (Bus Interface Unit); б) блок выполнения команд EU (Execution Unit), который работает независимо и параллельно.

Блок сопряжения с магистралью обеспечивает формирование 20 разрядного физического адреса, выборку команд и операндов из памяти и запись результатов в память составного блока:

- 6 8-разрядных регистров очереди команд;

- 4 16-разрядных сегментных регистра CS, DS, SS, ES;

- 16-разрядный регистр адреса команд IP;

- 16-разрядный регистр обмена;

- сумматор адреса;

- устройство управления шиной;

В каждом машинном цикле блок сопряжения готов выполнить цикл выборки слова (2б) из памяти, всякий раз, когда в очереди команд освоб-ся 2 ячейки памяти. Очередь организуется по принципу FIFO. С учетом формата команд МП (от 1 до 6 байт) конвейер всегда содержит от 1 до 6 команд следующих за выполняемой. Это сокращает затраты времени ожидание выборки команд из памяти. Если порядок следования команд нарушается, то регистр очереди очищается, считывается команда по новому адресу, передается на выполнение и начинает заполняться следующими командами. Сегментные регистры используются для формирования 20 разрядного физического адреса из логических 16 разрядных адресов.

Блок выполнения команд предназначен для выполнения операций по обработке данных и состоит из:

- УМУ - устройство микропрограммного управления

- 16 разрядного АЛУ;

- 8 16-и разрядных РОН

- регистр флагов

Коды операций из РОК (регистров очереди команд) поступают в УМУ, а операнды - в РОН, адреса - в сегментные регистры.

УМУ декодируют команды и формируют последовательность микрокоманд, управляющую процедурой. АЛУ выполняет логические и арифметические операции над 8 и 16 разрядными числами. Для ускорения внутренних обменов все регистры и магистрали имеют 16 разрядов.

Прямой связи с внешней шиной МП блок выполнения не имеет. Обмен данными происходит через регистр обмена.

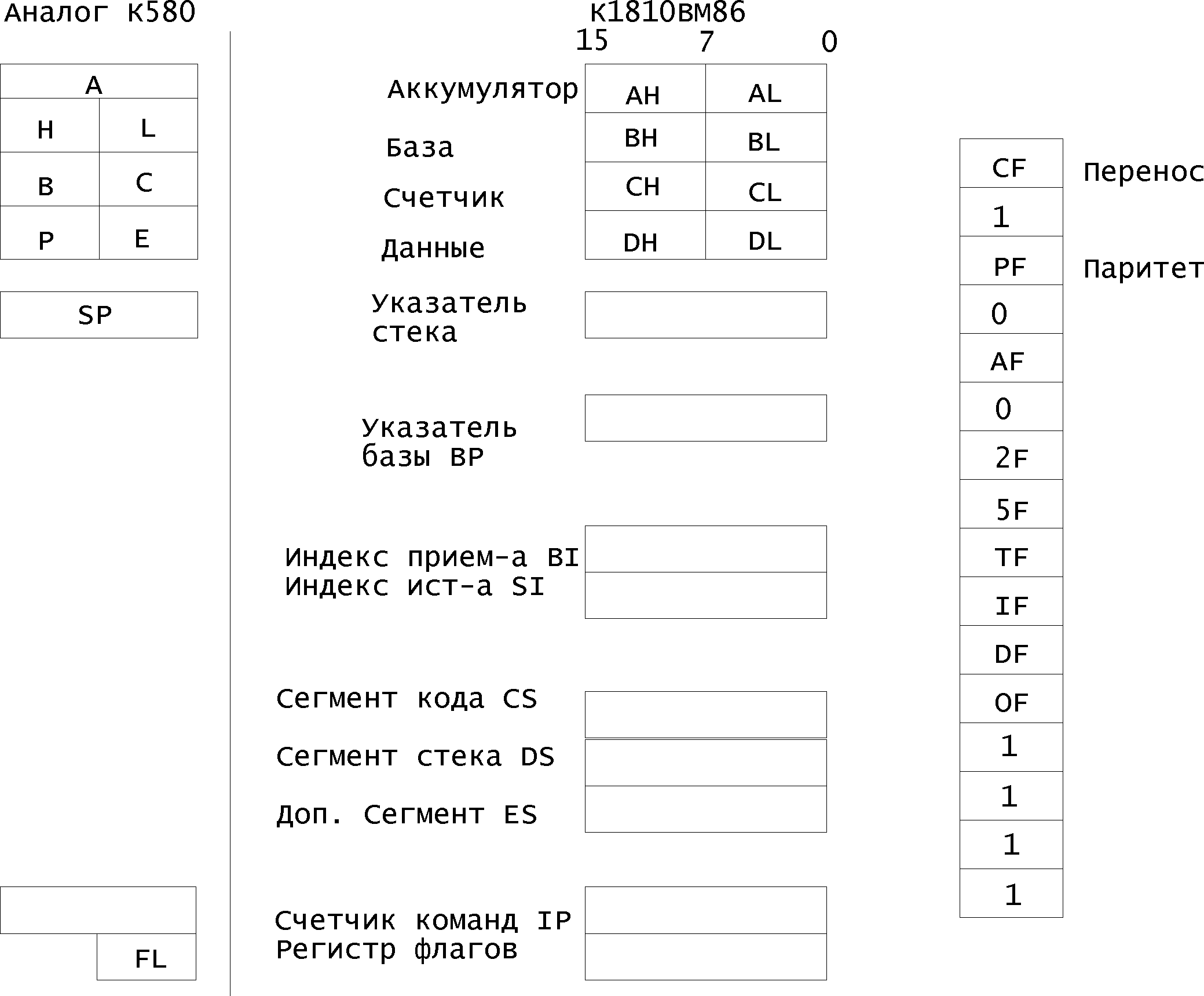

17. Программная модель к1810вм86.

ПМ содержит 3 группы регистров:

1гр. – РОН. Используются для хранения промежуточных результатов. Они 16 разрядные, но к ним можно обратиться как к 8 разрядным. Все регистры используются для выполнения логических и арифметических операций. В то же время некоторые команды предназначены для неявного использования опр. Регистра.

AX – умножение, деление, ввод-вывод слов в 16 разр.;

BX – умножение, деление, ввод-вывод байтов;

AH – умножение, деление байтов;

BX – операции перекодирования;

CX – операции со строками, циклы;

DX – умножение и деление слов, не явный ввод-вывод.

2гр. Указатели и индексные регистры. Предназначены для указания смещения в сегменте при задании логического адреса.

SS (SP&BP) содержат адресные смещения по отношению к стековому регистру.

DS (SI&DI) указывают сегмент и смещение по отношению к сегменту данных.

IP указывает сегмент и смещение относительно сегмента кода.

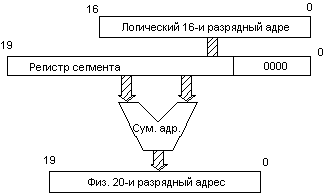

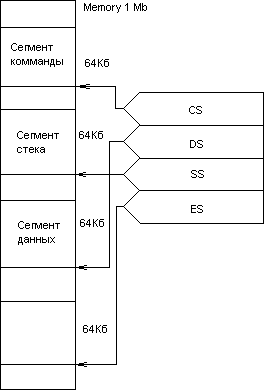

3гр. Регистры сегментов. Задают начальные адреса (базы) сегментов памяти. Любая ячейка памяти объемом в 1 Мб имеет однозначный 20-и разрядный физический адрес. В программах же действуют 16-и разрядные логические адреса, что позволяет адресовать один сегмент объемом 64 Кб. Программа рассматривет 1 Мб памяти как группу сегментов. Каждому сегменту соответствует непрерывно и отдельно адресуемая область памяти 64Кб физический адрес из логического формируется следующим образом: значение базы соответствующего регистра сегмента смещается влево на 4 разряда и получается 20 разрядное число с 0000 в младших разрядах. Затем складываем логическое число с логическим 16-и разрядным адресом. В результате мы получает 65536 сегментов, каждый емкостью 65536 байт. Сегменты перекрываются и расположены со сдвигом на 16 ячеек памяти.

В любой момент выполнения программы возможен доступ к 1 из 4 независимых сегментов:

а )

сегмент команд CS;

)

сегмент команд CS;

б) сегменту данных DS;

в) сегменту стека SS;

г) вспомогательному сегменту ES;

За исключением некоторых ограничений сегменты памяти могут быть заданы произвольно по умолчанию программиста и могут пересекаться в адресном пространстве.