- •Непозиционные сс. Смешанные сс

- •Позиционная сс

- •3. Перевод чисел из одной сс в другую.

- •5. Нульарные, унарные фал.Базис логических функций.

- •6. Бинарный фал. Синтез логических схем.

- •9. Правила эквивалентности булевой алгебры.

- •7.Представление фал. Таблица истинности. Сднф

- •8. Скнф. Получение сднф по скнф

- •11. Метод минимизаций Квайна. Метод Квайна-Мак-Класки.

- •10. Метод проб. Метод Блейка

- •12. Метод импликантных матриц.

- •13. Метод карт Карно. Минимизация не полностью определённых функций

- •6. Бинарный фал. Синтез логических схем.

- •14. Синтез фал в одноэлементном базисе. Работа с кнф

- •15. Логич. Элементы. Инверторы. Повторители, и их электр. Аналоги.

- •16. Элементы и, или и их электронные аналоги

- •17. Элемент xor и его электронный аналог. Триггер Шмитта

- •23. Триггеры.

- •30. Сумматоры. Принцип работы. Структура. Область применения. Примеры

- •18. Шифраторы. Принцип работы. Правила перевода из 10 сс в n сс.

- •19. Дешифраторы. Принцип работы. Правила перевода из n сс в 10 сс.

- •38. Процессор. Характеристики и архитектура процессора.

- •39.Процессор. Принципы работы, система команд. ПРерывание

- •43.Оперативная память. Виды и характеристики памяти.

- •47.Внешняя память. Виды и характеристики. Контроллеры

- •45.Защита памяти. Кэш-Память

- •44.Стековая и ассоциативная память. Виртуальная память

- •46.Адресация памяти.

- •51.Логический и физический доступ к секторам.

- •48.Файловая система. Расположение файлов на диске.

- •52.Назначение и типы устройств ввода вывода.

- •54.Организация устройств ввода/вывода: Порты, программный обмен, обмен по прерываниям.

- •37.Архитектура пк. Принцип Фон Неймана. Функциональная организация машины Фон Неймана.

- •53.Виды программного обеспечения. Слои по. Порядок загрузки по.

- •55.Представление чисел в эвм.

- •28. Взаимные преобразования триггеров

- •29. Компараторы. Принцип работы. Структура. Область работы. Применение. Пример

- •33.Арифметико-логическое устройство.

- •40. Процессор. Режимы работы. Конвейер. Кэширование

- •41.Процессор. Типы параллелизма. Сопроцессор.Виды процессоров

- •42.Запоминающие устройства. Классификация. Постоянная память

- •Постоянная память.

- •58. Влияния структуры программы на время ее выполнения

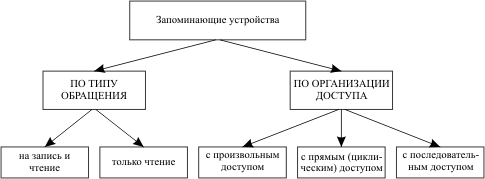

42.Запоминающие устройства. Классификация. Постоянная память

Запоминающие устройства можно классифицировать по целому ряду параметров и признаков. На рисунке ниже представлена классификация по типу обращения и организации доступа к ячейкам ЗУ.

По типу обращения ЗУ делятся на устройства, допускающие как чтение, так и запись информации, и постоянные запоминающие устройства (ПЗУ), предназначенные только для чтения записанных в них данных (ROM - read only memory). ЗУ первого типа используются в процессе работы процессора для хранения выполняемых программ, исходных данных, промежуточных и окончательных результатов. В ПЗУ, как правило, хранятся системные программы, необходимые для запуска компьютера. В некоторых ЭВМ, предназначенных для работы по одним и тем же неизменяемым алгоритмам, все программное обеспечение может храниться в ПЗУ.

В ЗУ с произвольным доступом (RAM - random access memory) время доступа не зависит от места расположения участка памяти (например, ОЗУ).

В ЗУ с прямым (циклическим) доступом благодаря непрерывному вращению носителя информации (например, магнитный диск) возможность обращения к некоторому участку носителя циклически повторяется. Время доступа здесь зависит от взаимного расположения этого участка и головок чтения/записи и во многом определяется скоростью вращения носителя.

В ЗУ с последовательным доступом производится последовательный просмотр участков носителя информации, пока нужный участок не займет некоторое нужное положение напротив головок чтения/записи (например, магнитные ленты).

Идеальное

запоминающее устройство должно обладать

бесконечно большой емкостью (![]() )

и иметь бесконечно малое время обращения

(

)

и иметь бесконечно малое время обращения

(![]() ).

На практике эти параметры находятся в

противоречии друг другу: в рамках одного

типа ЗУ улучшение одного из них ведет

к ухудшению значения другого. В настоящее

время запоминающие устройства компьютера

строятся по иерархическому принципу:

).

На практике эти параметры находятся в

противоречии друг другу: в рамках одного

типа ЗУ улучшение одного из них ведет

к ухудшению значения другого. В настоящее

время запоминающие устройства компьютера

строятся по иерархическому принципу:

Постоянная память.

Системная постоянная память (ПЗУ) занимает сравнительно небольшой объем (обычно 64 Кбайта). Однако ее значение для компьютера очень велико. Само ее название ROM BIOS (ROM Basic Input/Output System) — базовая система ввода/вывода — говорит о том, что в ней находится набор программ нижнего уровня для управления устройствами ввода/вывода. Поэтому даже до загрузки в оперативную память исполняемых программ с диска компьютер имеет возможность обслуживать клавиатуру, дисплей, подавать звуковые сигналы, общаться с дисками и т.д. Большинство современных видеоадаптеров, а также контроллеров накопителей имеют собственную систему BIOS, которая дополняет системную BIOS во время основной работы. Вызов программ BIOS осуществляется через программные или аппаратные прерывания, для чего BIOS формирует соответствующую таблицу векторов прерываний. Но этим функции постоянной памяти не ограничиваются.

56-57. Организация вычисления

Таблица сложения двоичных чисел:

0 + 0 = 0

0 + 1 = 1

1 + 0 = 1

1 + 1 = 10

Таблица разности двоичных чисел:

0 - 0 = 0

1 - 0 = 1

1 - 1 = 0

10 - 1 = 1

Таблица умножения двоичных чисел

0 * 0 = 0

0 * 1 = 0

1 * 0 = 0

1 * 1 = 1

Таблица деления двоичных чисел

0 / 0 = не определено

0 / 1 = 0

1 / 0 = не определено

1 / 1 = 1

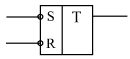

24. RS-триггеры. Классификация. Структура. Область приминения

RS-триггер — триггер, который сохраняет своё предыдущее состояние при одних комбинациях сигналов на входах и меняет своё выходное состояние при подаче на один из его входов единицы. RS-триггеры иногда называют RS-фиксаторами. RS-триггеры разделяются на асинхронные и синхронные.

Асинхронный триггер представляет собой запоминающую ячейку, представленную выше (т.е. в нем отсутствует комбинационная схема управления). Его УГО представлено ниже.

У синхронного триггера состояние его входов учитывается только в момент тактирования, например по переднему фронту импульса. Основу синхронного одноступенчатого триггера составляет рассмотренная выше запоминающая ячейка. Синхросигнал C разрешает передачу на входы элементов 1 и 2 таких значений сигналов S и R, которые устанавливают ЗЯ в то или иное состояние. Неактивное значение синхросигнала (сигнал 0) обеспечивает режим хранения.

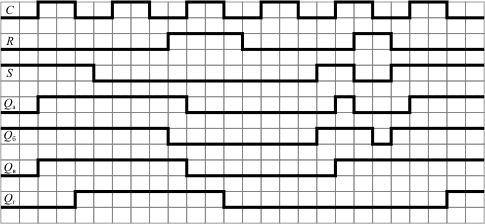

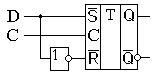

25. D-триггер.

В RS-триггерах для записи логического нуля и логической единицы требуются разные входы, что не всегда удобно. При записи и хранении данных один бит может принимать значение, как нуля, так и единицы. Для его передачи достаточно одного провода. Как мы уже видели ранее, сигналы установки и сброса триггера не могут появляться одновременно, поэтому можно объединить эти входы при помощи инвертора, как показано на рисунке.

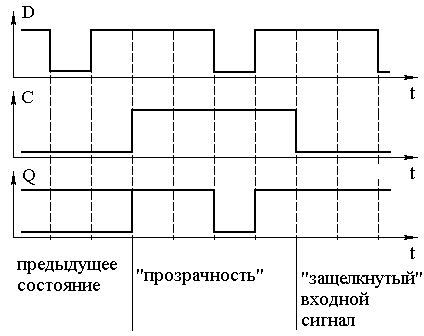

Такой триггер получил название D-триггер. D-триггер (delay — задержка) — запоминает состояние входа и выдаёт его на выход. D-триггеры имеют, как минимум, два входа: информационный D и синхронизации С. Сохранение информации в D-триггерах происходит в момент прихода активного фронта на вход С. Так как информация на выходе остаётся неизменной до прихода очередного импульса синхронизации, D-триггер называют также триггером с запоминанием информации или триггером-защёлкой.

По этой временной диаграмме видно, что триггер-защелка хранит данные на выходе только при нулевом уровне на входе синхронизации. Если же на вход синхронизации подать активный высокий уровень, то напряжение на выходе триггера будет повторять напряжение, подаваемое на вход этого триггера. Входное напряжение запоминается только в момент изменения уровня напряжения на входе синхронизации C с высокого уровня на низкий уровень. Входные данные как бы “защелкиваются” в этот момент, отсюда и название – триггер-защелка. Принципиально в этой схеме входной переходной процесс может беспрепятственно проходить на выход триггера. Поэтому там, где это важно, необходимо сокращать длительность импульса синхронизации до минимума. Чтобы преодолеть такое ограничение были разработаны триггеры, работающие по фронту.

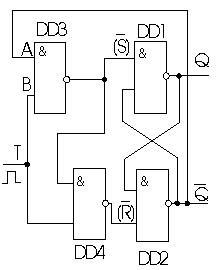

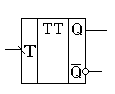

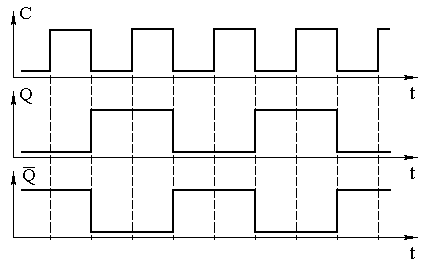

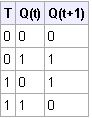

26. T-триггер

Т-триггер – это счетный триггер. У Т-триггера имеется только один вход. После поступления на этот вход импульса, состояние Т-триггера меняется на прямо противоположное. Счётным он называется потому, что он как бы подсчитывает количество импульсов, поступивших на его вход. Считать этот триггер умеет только до одного. При поступлении второго импульса T-триггер снова сбрасывается в исходное состояние. Т-триггер можно синтезировать из любого двухступенчатого триггера.

Реализация T-триггера, его УГО и временная диаграмма и таблица истинности приведены ниже.

Т-триггер по каждому такту изменяет своё логическое состояние на противоположное при единице на входе Т, и не изменяет выходное состояние при нуле на входе T. Т-триггер часто называют счётным триггером. Т-триггер часто применяют для понижения частоты в 2 раза, при этом на Т вход подают единицу, а на С — сигнал с частотой, которая будет поделена.

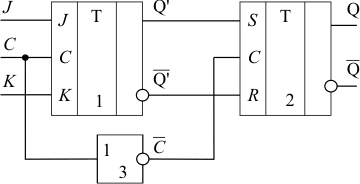

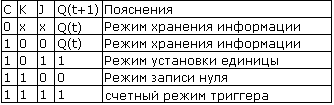

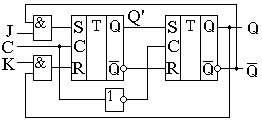

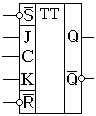

27.JK- триггер

JK-триггер является универсальным. JK-триггер имеет два информационных входа J и K, тактовый динамический вход, чаще инверсный, и два асинхронных входа установки и сброса. Он работает так же как RS-триггер, с одним лишь исключением: при подаче логической единицы на оба входа J и K состояние выхода триггера изменяется на противоположное. Вход J (Jump — прыжок) аналогичен входу S у RS-триггера. Вход K (Kill — убить) аналогичен входу R у RS-триггера. При подаче единицы на вход J и нуля на вход K выходное состояние триггера становится равным логической единице. А при подаче единицы на вход K и нуля на вход J выходное состояние триггера становится равным логическому нулю. JK-триггер в отличие от RS-триггера не имеет запрещённых состояний на основных входах. На практике применяются только синхронные JK-триггеры, то есть состояния основных входов J и K учитываются только в момент тактирования, например по положительному фронту импульса на входе синхронизации.

Таблица истинности JK-триггера, схемная реализация и УГО приведены ниже.

Временные диаграммы работы JK-триггера совпадают с приведёнными ранее диаграммами RS-триггера.

JK-триггер может быть двухступенчатым (см. рисунок ниже).