- •6.092200 – “Електричні машини і апарати”

- •Лабораторна робота №1 отримання навичок розробки програм мовою асемблера для мікропроцесора к1810вм86 у середовищі програмного пакету „turbo assembler” фірми borland

- •1.1 Теоретичні відомості

- •1.2 Порядок виконання роботи

- •1.4 Контрольні запитання

- •Лабораторна робота № 2 вивчення системи команд мп к1810вм86, команди передавання даних, математичних операцій

- •2.1 Теоретичні відомості

- •2.2 Порядок виконання роботи

- •2.4 Контрольні запитання

- •Лабораторна робота №3 вивчення системи команд мп к1810вм86, команди логічних операцій, команди організації переривань. Організація програмних циклів

- •3.1 Теоретичні відомості

- •3.2 Порядок виконання роботи

- •3.4 Контрольні запитання

- •Лабораторна робота № 4 розробка програми аналогово-цифрового перетворення і читання даних з ацп для мп к1810вм86

- •4.1 Теоретичні відомості

- •4.2 Порядок виконання роботи

- •4.4 Контрольні запитання

- •Лабораторна робота № 5 програмне опитування зовнішніх пристроїв. Програмування паралельного інтерфейсу

- •5.1 Теоретичні відомості

- •5.2 Порядок виконання роботи

- •5.4 Контрольні запитання

- •Лабораторна робота № 6 програмне опитування датчиків технологічної інформації. Програмне виведення інформації на зовнішній пристрій

- •6.1 Теоретичні відомості

- •6.2 Порядок виконання роботи

- •6.4 Контрольні запитання

- •Список літератури

- •3 9614, М. Кременчук, вул. Першотравнева, 20

3.2 Порядок виконання роботи

Ознайомитися з особливостями системи переривань мікропроцесора, вивчити їх атрибути.

Вивчити механізм виклику оброблювачів переривань системних пристроїв.

Відповідно до запропонованої граф-схеми роботи написати додатки, що забезпечують взаємодію задач через переривання.

Забезпечити затримку виведення рядка за перериваннями таймера значенням t_n порядку 1 с.

Написати додаток, який би здійснював запис під час виконання основної програми.

Перевірити правильність виконання програми.

Вийти коректно із програмного середовища.

Скласти звіт до лабораторної роботи.

3.3 Зміст звіту

Титульна сторінка.

Найменування та мета лабораторної роботи.

Короткі теоретичні відомості.

Отримане у викладача завдання (текст програми з докладними коментарями).

Опис виконання кожного пункту завдання.

Письмові відповіді на контрольні питання.

3.4 Контрольні запитання

Пояснити призначення кожного з внутрішніх реґістрів послідовного порта. Які основні компоненти входять до його складу?

Як відкрити вихідний файл з текстом програми мовою асемблера в середовищі відлагоджувача Turbo Debugger?

Які режими перегляду реґістрів процесора, для якого розробляється програма.

Лабораторна робота № 4 розробка програми аналогово-цифрового перетворення і читання даних з ацп для мп к1810вм86

Мета роботи. |

Навчитися створювати програми для керування процесом аналогово-цифрового перетворення і забезпечити читання перетворених даних з АЦП. |

4.1 Теоретичні відомості

Пристрої обчислювальної системи з’єднуються один з одним за допомогою уніфікованих систем зв’язку, що називаються інтерфейсом. Інтерфейс є системою шин, пристроїв, що погоджують, алгоритмів, які забезпечують зв’язок всіх частин мікропроцесорної системи між собою. Від характеристик інтерфейсу залежить швидкодія та надійність мікропроцесорної системи. Інтерфейс повинен бути стандартизований, щоб забезпечити зв’язок процесора і оперативної пам’яті з будь-яким периферійним пристроєм (ПП). Необхідне перетворення формату даних повинне проводитися в ПП. Алгоритми функціонування інтерфейсу і керуючого реґістра, також повинні бути стандартизовані. Схеми інтерфейсу зазвичай розташовуються в самих пристроях, що з’єднуються.

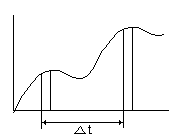

До спеціалізованих пристроїв інтерфейсу мікропроцесорних систем відносяться АЦП, ЦАП та перетворювачі кодів. Спеціалізовані пристрої перетворюють інформацію до вигляду, зручного для сприйняття даною системою (це виконують АЦП і перетворювачі кодів). ЦАП перетворюють інформацію до вигляду, зручного для сприйняття периферійними пристроями. Перетворення аналогової інформації в цифрову базується на теоремі Котельникова: будь-який аналоговий сиґнал може бути записаний в дискретній формі й інформація не буде втрачена, якщо крок квантування t буде вибраний за умови:

![]() , (4.1)

, (4.1)

де Fmax – максимальна частота спектру передаваного сиґналу.

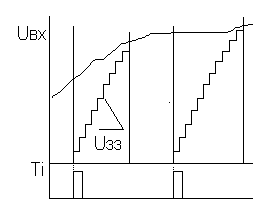

Рис. 4.1 – Вибір кроку квантування для перетворення аналогового сиґналу в цифровий

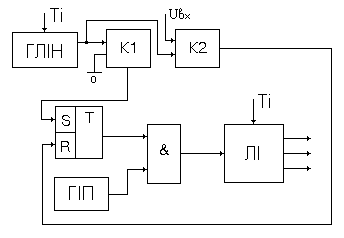

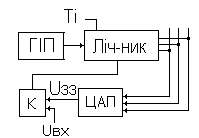

Рис. 4.2 – Структурна схема аналогово-цифрового перетворювача

У даній схемі відбувається проміжне перетворення напруги Uвх у тривалість імпульсу тригера, яка у свою чергу визначає кількість імпульсів генератора імпульсної послідовності (ГІП) підрахованих лічильником. Лічильник видає результат в двійковому коді, отже показання лічильника пропорційні Uвх. Тактовий імпульс запускає ґенератор напруги, яка лінійно змінюється (ГЛЗН), і обнуляє лічильник. У двох компараторах К1 і К2 відбувається порівняння напруги ГЛЗН з «0» і з Uвх.

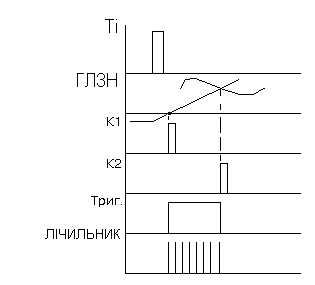

Рис. 4.3 – Часові діаграми роботи аналогово-цифрового перетворювача за схемою рис.4.2

Коли рівень напруги ГЛЗН дорівнює «0», на виході К1 виробляється сиґнал, який встановлює тригер в одиничний стан. На схему «І» подається одиничний сиґнал з виходу тригера і послідовність імпульсів з виходу ГІП. Імпульси ГІП подаються на лічильник, який їх рахує. Коли напруга пилкоподібних імпульсів стане рівною Uвх, сиґнал з виходу К2 «переключить» тригер в нульовий стан, імпульси через схему «І» не проходять, рахунок припиняється. Кількість минулих імпульсів пропорційна Uвх. Оскільки напруга «пилки» не є лінійною, особливо на початковій ділянці, то точність перетворення невелика. Більшу точність забезпечують АЦП із зворотним зв’язком (ЗЗ) і АЦП стежачого типу.

АЦП із зворотним зв’язком

ЦАП виробляє напругу ЗЗ. Ця напруга має ступінчасту форму. З приходом тактового імпульсу лічильник починає зчитувати від генератора імпульсної послідовності (ГІП). Рахунок припиняється в разі подачі нульового сиґналу з вихідного компаратора. Цей сиґнал виробляється в тому випадку, якщо напруга ЗЗ більша або дорівнює Uвх. Кількість зчитаних імпульсів пропорційна Uвх в двійковому коді.

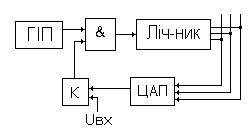

Рис. 4.4 – Структурна схема аналогово-цифрового перетворювача зі зворотним зв’язком

Рис. 4.5 – Часові діаграми аналогово-цифрового перетворювача зі зворотним зв’язком

АЦП стежачого типу

АЦП зі зворотним зв’язком перетворюють в двійковий код тільки зростаючу напругу Uвх. АЦП стежачого типу перетворюють в цифровий сиґнал як зростаючу, так і убуваючу напругу. У цій схемі застосовується реверсивний лічильник. Коли на виході компаратора (К) одиничний сиґнал (Uвх > Uзз) лічильник знаходиться в режимі прямого рахунку. Коли Uвх Uзз, на виході К – «0» і лічильник переходить в режим зворотного рахунку.

Рис. 4.6 – Структурна схема аналогово-цифрового перетворювача стежачого типу

Приклад. Процедура програмно-апаратного аналого-цифрового перетворювача працює за принципом послідовного наближення за двійковою системою. Процедура може запускатися за перериванням від зовнішнього пристрою або від таймера (періодично).

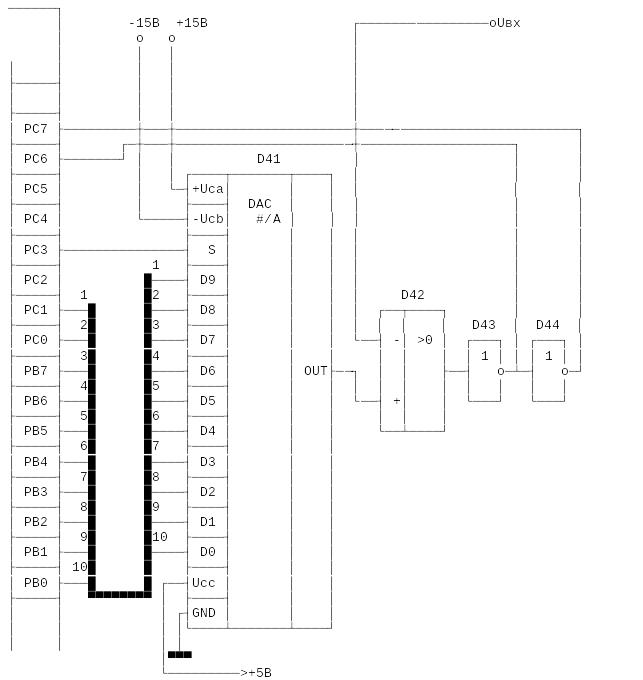

Схема АЦП на базі ЕОМ (мікроконтролера) показана на рис. 4.7.

Рис. 4.7 – Приклад (фрагмент) електричної схеми підключення АЦП до ЕОМ

Вона включає 10-розрядний реверсивний ЦАП, підключений до виходів порта РВ (молодші 8 розрядів) і порта РС.3-0 (старші розряди – РС.1-0 і знак – РС.3). Порт РС.7-4 настроюється на введення, два біти його: D7 і D6 використовуються для введення знака розузгодження компаратора в прямому та інверсного кодах. Аналоговий вихід ЦАП підключений до інверсного входу компаратора, на прямий (неінвертований) вхід якого подається вимірюваний реґістр. Вихід компаратора через реґістри інвертування DV3, DV4 підключений до входу ЕОМ для визначення знака розузгодження і програмного збереження або усунення бітів послідовного наближення.

Нижче наведений приклад фрагменту програмного коду для обміну даними між АЦП та МП системою:

stck segment para stack ‘stack’ ;налаштування сеґмента стека

dw 100 dup(?) ;встановлюється об’ємом у 100 слів

stck ends ;кінець сеґмента стека

data segment public para ;сеґмент даних

codin dw (?)

data ends ;кінець сеґмента даних

cod segment public para ‘code’ ;початок сеґмента кода

cap proc far ;оголошення процедури

assume cs:cod,ds:data,ss:stck,es:data

pb equ 21h ;адреса порта PB

pc equ 22h ;адреса порта PC

pu equ 23h ;адреса реґістра керування портами

push ax ;збереження в стек вмісту реґістра АХ

push

cx ;збереження в стек вмісту реґістра

push dx ;збереження в стек вмісту реґістра DХ

mov al,98h ;записуємо в акумулятор керуюче слово

;10011000B для настройки режиму 0 порта

;А – на введення

out pu,al ;C(7-4) – введення, В – виведення,

;С(3-0) – вивід

xor al,al ;очищення акумулятора

out pc,al ;пересилання до ЦAП нульового значення

out pb,al ;пересилання до ЦAП нульового значення

nop ;пауза на час роботи ЦАП

in al,pc ;введення знака біта С(7-4)

and al,0Ch ;операція маскування для виділення

;бітів D(7-6)

test al,08h ;перевірка знака вимірюваної напруги

jz mmin ;якщо знак «мінус» – перехід

;на встановлення знака (-)

mov dx,0000 ;інакше знак (+)

mov ch,40h ;контрольований біт розузгодження – D6

jmp short start ;команда безумовного переходу на початок

mmin: mov dx,0800h ;знак результату «мінус»

mov ch,80h ;контрольований біт – D7

mov ch,02h ;начало перевірки бітів PC.1,0

start: mov al,dh ;біти, що вже пеpевіpені

or al,cl ;вставлення біта, що перевіряється

out pc,al ;виведення старших бітів і знака на порт

;PC (3-0)

nop ;пауза ЦАП

in al,pc

and al,ch ;перевірка знака розузгодження

jz nnn ;якщо більше – біт не потрібен

or dh,cl ;інакше вводиться результат

nnn: rol cl,1 ;зсув біта, що перевіряється

jnc start ;якщо це не останній біт – повторити

mov cl,80h ;початок перевірки бітів PB 7-0

stta: mov al,dl

or al,cl ;вставлення біта, що перевіряється

out pb,al ;виведення молодших бітів та знака до ЦАП

nop ;пауза

in al,pc

and al,ch ;перевірка знака розузгодження

jz ttt ;якщо більше – біт не потрібен

or dl,cl ;інакше біт вставляється в результат

ttt: rol cl,1 ;зсув біта, що перевіряється вліво

jnc stta ;якщо біт не останній – повторити

test dx,0800h ;перевірка значення знака числа

jz rrr ;якщо «плюс» - вихід

and dx,03FFh ;встановлення прямого позитивного кода

neg dx ;отримання додаткового кода

rrr: mov codin,dx ;запам’ятовування результату

pop dx ;відновлення зі стека вмісту реґістра DX

pop cx ;відновлення зі стека вмісту реґістра CX

pop ax ;відновлення зі стека вмісту акумулятора

mov al,20h ;очищення біта переривання

out PU,al ;пересилання на контролер переривань

iret ;вихід з процедури обробки переривання

cap endp ;кінець процедури

cod ends ;завершення сеґмента коду

end cap ;кінець програми

Пpогpама АЦП працює таким чином:

Вхідна цифрова інформація на ЦАП подається в прямому коді як для позитивної, так і для негативної напруги. В разі негативної напруги виводиться одиниця в знаковий розряд порта РС3 при позитивному виході – цей розряд ну-льовий. В схемі ЦАП цей розряд, підключений до входу S, перемикає полярність опорної й вихідної напруги.

У процедурі наближення спочатку в ЦАП вводиться нульове значення реґістр і визначається знак напруги, що вимірюється. В залежності від цього знака контроль розузгодження здійснюється через наявність 1 в біті D7 РС при позитивній напрузі, що виміряється, або D6 – при негативній.

Розподіл реґістрів процесора:

DX – реґістр результату;

CL – маска біта, що додається;

CH – маска знака розузгодження ( CH = 10000000В при негативній напрузі входу, СН = 01000000В – при позитивному);

AL – оперативний реґістр уведення/виведення;

AH – запасний.

Після перевірки всіх бітів при негативній вхідній напрузі (якщо біт D.10 в реґістрі DX дорівнює 1) проводиться переведення негативного числа з прямого в нормальний додатковий код, а потім результат записується в пам’ять ЕОМ за міткою CODIN і всі реґістри відновлюються зі стека.