- •Введение

- •Преобразователи

- •1.1. Назначение и виды цифро- аналоговых преобразователей

- •1.2. Основные параметры цап

- •1.3. Принципы построения цап

- •Выходное напряжение для схемы, приведенной на рис.1.3, определяется формулой

- •Напряжение на выходе операционного усилителя определяется выражением

- •1.4. Серийные микросхемы цап

- •Характеристики интегральных микросхем цап

- •Контрольные вопросы:

- •Преобразование сигналов

- •2.1. Принципы аналого-цифрового преобразования сигналов

- •Для сигналов с ограниченным спектром теорема отсчетов имеет вид

- •2.2. Основные характеристики ацп

- •2.3. Принципы построения ацп

- •Контрольные вопросы:

- •3.4. Представление дробных чисел в двоичном коде с

- •3.5. Представление чисел в двоичном коде с плавающей

- •3.2. Знаковые обратные двоичные коды

- •3.3. Знаковые дополнительные двоичные коды

- •3.4. Представление дробных чисел в двоичном коде с фиксированной запятой

- •3.5. Представление чисел в двоичном коде с плавающей запятой

- •3.6. Запись десятичных чисел

- •3.7. Суммирование двоично- десятичных чисел

- •3.8. Арифметико-логические устройства

- •4.1. Функции микропроцессорных систем и микро-эвм

- •4.2. Принципы построения микропроцессорных систем и

- •4.2. Принципы построения микропроцессорных систем и микро-эвм

- •4.3. Структура и функционирование микропроцессорных систем

- •4.4. Микроконтроллеры

- •4.5. Микропроцессорные комплекты и микро-эвм

- •(Intel 8085a)

- •5.3. Синхронизация и последовательность действий мп

- •5.4. Система прерываний

- •5.2. Блок регистров

- •5.3. Синхронизация и последовательность действий мп

- •5.4. Система прерываний

- •6. Команды микропроцессора

- •7.1. Понятие системной шины микропроцессора

- •7.2. Адресное пространство микропроцессорного

- •7.3. Способы расширения адресного пространства

- •7.2. Адресное пространство микропроцессорного устройства

- •7.3. Способы расширения адресного пространства микропроцессора

- •8. Параллельный порт

- •9. Последовательный порт

- •9.1. Синхронный последовательный порт

- •9.2. Асинхронный последовательный порт

- •9.1. Синхронный последовательный порт

- •9.2. Асинхронный последовательный порт

- •10. Статические оперативные запоминающие устройства

- •11. Постоянные запоминающие устройства

- •11.1. Пзу на основе мультиплексора

- •11.2. Масочные пзу

- •11.3. Программируемые пзу

- •11.4. Пзу с ультрафиолетовым стиранием

- •11.5. Электрически стираемые ппзу

- •11.6. Flash - пзу

- •12. Подключение внешних устройств к микропроцессору

- •13. Шинные формирователи

- •14. Принципы построения таймеров

3.6. Запись десятичных чисел

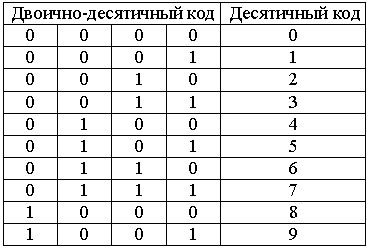

Иногда бывает удобно хранить числа в памяти процессора в десятичном виде (например, для вывода на экран дисплея). Для записи таких чисел используются двоично-десятичные коды. Для записи одного десятичного разряда используется четыре двоичных бита. Эти четыре бита называются тетрадой. При помощи четырех бит можно закодировать шестнадцать цифр. Лишние комбинации в двоично-десятичном коде являются запрещенными. Таблица соответствия двоично-десятичного кода и десятичных цифр приведена ниже (табл. 3.1):

Табл. 3.1.

Остальные комбинации двоичного кода в тетраде являются запрещенными. Запишем пример двоично-десятичного кода:

1258 = 0001 0010 0101 1000

589 = 0000 0101 1000 1001.

Достаточно часто в памяти процессора для хранения одной десятичной цифры выделяется одна ячейка памяти (восьми, шестнадцати или тридцатидвухразрядная). Это делается для повышения скорости работы программы. Для того, чтобы отличить такой способ записи двоично-десятичного числа от стандартного, способ записи десятичного числа, как это показано в примере, называется упакованной формой двоично-десятичного числа.

3.7. Суммирование двоично- десятичных чисел

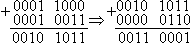

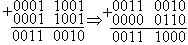

Суммирование двоично-десятичных чисел можно производить по правилам обычной двоичной арифметики, а затем производить двоично-десятичную коррекцию. Двоично-десятичная коррекция заключается в проверке каждой тетрады на допустимые коды. Если в какой либо тетраде обнаруживается запрещенная комбинация, то это говорит о переполнении. В этом случае необходимо произвести двоично-десятичную коррекцию. Двоично-десятичная коррекция заключается в дополнительном суммировании числа шесть (число запрещенных комбинаций) с тетрадой, в которой произошло переполнение или произошёл перенос в старшую тетраду.

Пример 3.8:

Пример 3.9:

3.8. Арифметико-логические устройства

Выше были рассмотрены схемы суммирования многоразрядных кодов. Однако кроме суммирования часто требуется осуществлять и вычитание двоичных кодов. Двоичные коды, при помощи которых можно записывать отрицательные числа уже рассматривались в предыдущих разделах. Там же было показано, что при использовании дополнительных кодов операцию вычитания двух положительных чисел можно заменить операцией суммирования положительного и отрицательного числа, при этом получение отрицательного числа из положительного числа является элементарной операцией. Для этого необходимо проинвертировать число и прибавить к нему 1.

Схема устройства вычитания числа A из числа B приведена на рис. 3.8, а схема вычитателя числа B из числа A приведена на рис. 3.9.

Рис. 3.8. Схема вычитателя числа A из числа B

Рис. 3.9. Схема вычитателя числа B из числа A

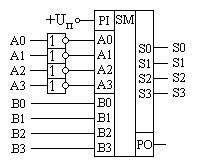

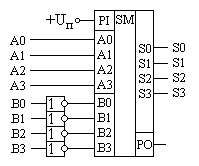

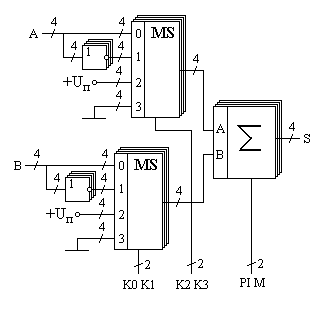

Если же потребуется в процессе вычислений изменять арифметическую операцию, то в схему можно ввести коммутатор. Такая схема приведена на рис. 3.10.

Рис. 3.10. Структурная схема арифметического устройства

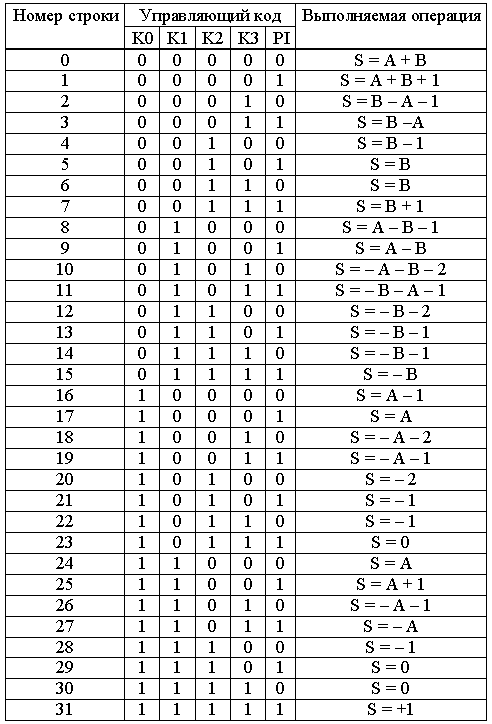

В приведённой на рис. 3.10 схеме используются четырёхвходовые коммутаторы, для управления каждым из которых достаточно двух бит. То есть для управления всей схемы в целом достаточно четырёх проводов управления. Попытаемся построить таблицу операций, которые будет выполнять эта схема. На результат операции будет влиять вход переноса сумматора PI, поэтому этот провод тоже включим в состав кода, управляющего схемой. Операции, которые выполняются арифметической схемой в зависимости от поданного на управляющие линии кода, приведены в табл. 3.2.

Табл. 3.2.

Проанализируем эту таблицу. Если на все управляющие входы подать низкий потенциал, то к входу сумматора будут подключены коды A и B без инверсии. В этом случае будет производиться операция суммирования. Эта ситуация отображена первыми двумя строками таблицы выполняемых операций. Операция вычитания осуществляется второй, третьей, восьмой и девятой строкой. В этом случае один из операндов поступает на вход сумматора через блок инверторов. Правда для получения дополнительного кода не хватает единицы, но её можно подать на вход переноса сумматора PI. Ещё одной часто используемой операцией является увеличение числа на единицу или уменьшение числа на единицу. Эти операции позволяют легко организовывать циклы в программе и переходить от предыдущего операнда к следующему. Такие операции могут быть выполнены при помощи кодов, записанных в строках четыре, семь, шестнадцать и двадцать пять. Кроме того, схема арифметического устройства может просто передавать на выход любой из входных кодов без изменения, что позволяет осуществлять копирование данных (суммирование с константой ноль) через это устройство без дополнительных схем коммутации.

При небольшом изменении схемы такое устройство может быть преобразовано в схему, которая позволяет осуществлять не только арифметические, но и логические операции. Для этого нужно вести дополнительный коммутатор, который будет разрывать цепи переноса между разрядами. Эта управляющая цепь обычно называется M.

Подчеркнём основную особенность полученного устройства. Арифметико-логические устройства позволяют выбирать вид выполняемой операции при помощи кода, подаваемого на специальные ножки микросхемы. Это позволяет программировать одно и то же устройство для выполнения различных функций. Разработка такого устройства позволило обменивать большую скорость выполнения отдельных операций на сложность реализуемого алгоритма, что, в конце концов, привело к разработке микропроцессорных систем.

КОНТРОЛЬНЫЕ ВОПРОСЫ:

1. Беззнаковые двоичные коды.

2. Знаковые обратные двоичные коды.

3. Знаковые дополнительные двоичные коды.

4. Представление дробных чисел в двоичном коде с фиксированной

запятой.

5. Представление чисел в двоичном коде с плавающей запятой.

6. Запись десятичных чисел.

7. Суммирование двоично-десятичных чисел.

8. Арифметико-логические устройства.

4. МИКРОПРОЦЕССОРНЫЕ

СИСТЕМЫ И МИКРО-ЭВМ