Master-uri.narod.ru |

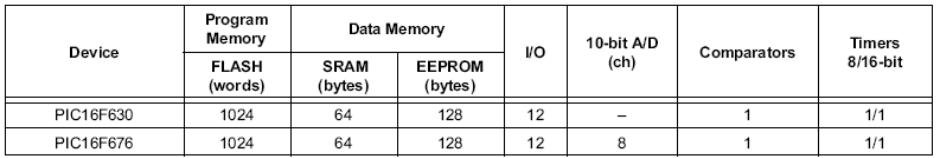

PIC16F630/676

|

Описание регистров и всякое другое. |

Master-uri 20.02.2010

|

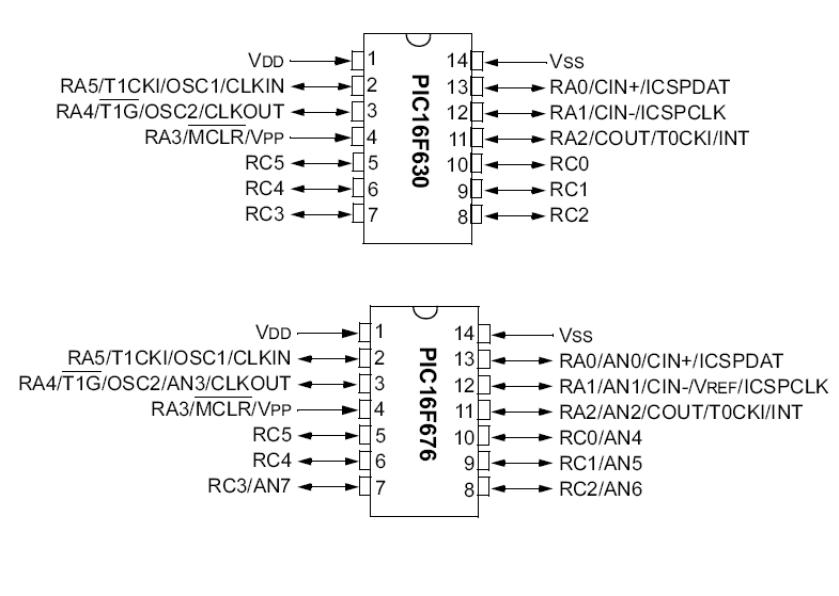

Расположение выводов

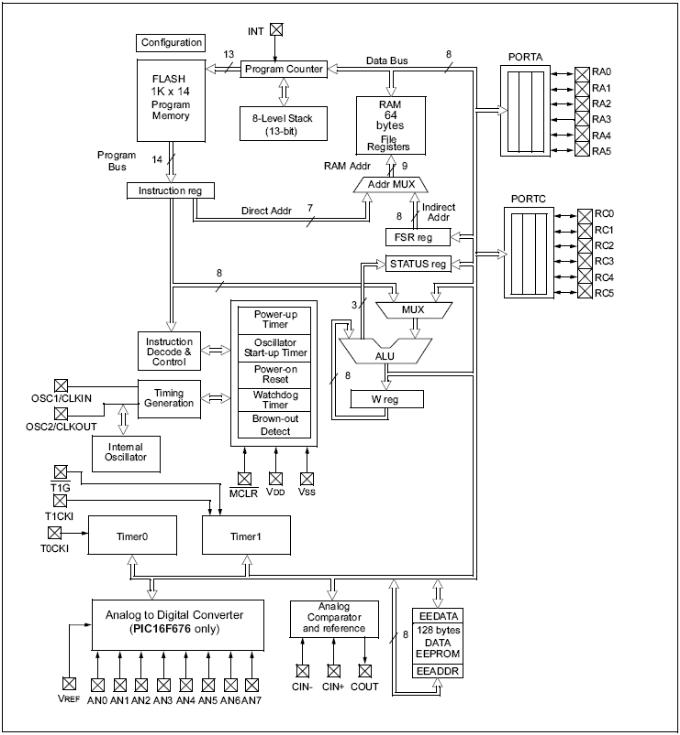

Блок схема

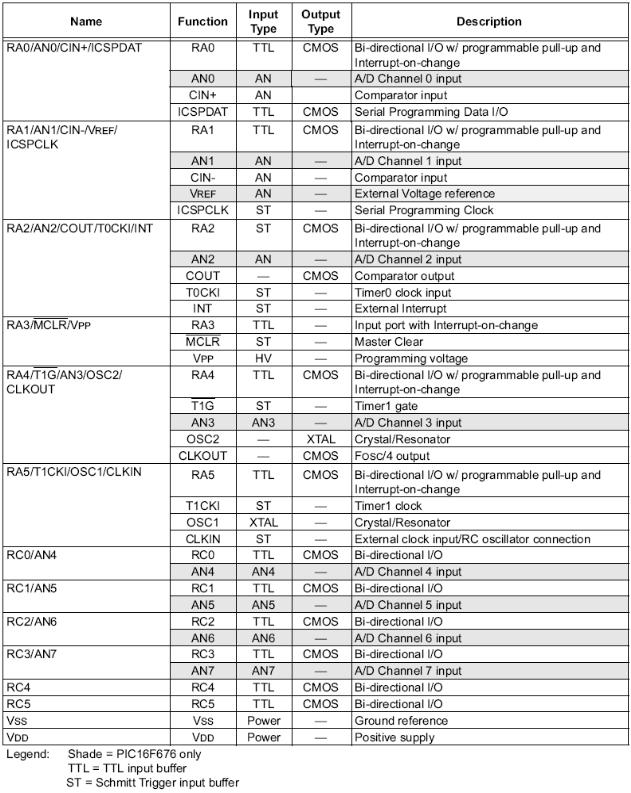

Описание выводов

Карта памяти

STATUS (03h или 83h)

№-бита |

Вес бита |

Название бита |

Описание бита |

|

7 |

128 |

IRP |

Зарезервирован,должен поддерживатся равным “0” |

- |

6 |

64 |

RP1 |

Зарезервирован,должен поддерживатся равным “0” |

- |

5 |

32 |

RP0 |

Выбор банка(используется при прямой адресации) 1=Банк 1 (80h-FFh) 0=Банк 0 (00h-7Fh) |

R/W-0 |

4 |

16 |

-TO |

Флаг переполнения сторожевого таймера WDT 1= после сброса POR,выполнения команды CLRWDT или SLEEP 0= произошло переполнение WDT |

R-1 |

3 |

8 |

-PD |

Флаг детектора выключения питания 1= после сброса POR,или выполнения команды CLRWDT 0= после выполнения команды SLEEP |

R-1 |

2 |

4 |

Z |

Флаг нулевого результата операции 1=нулевой результат 0=не нулевой результат |

R/W-x |

1 |

2 |

DC |

Флаг десятичного переноса/заёма (команды ADDWF, ADDLW,SUBLW,SUBWF) Флаг заёма имеет инверсное значение 1=был перенос из младшего полубайта 0=не было переноса из младшего полубайта |

R/W-x |

0 |

1 |

C |

Флаг переноса/заёма 1=был перенос из старшего бита 0=не было переноса из старшего бита |

R/W-x |

Примечание: 1.Флаги C и DC используются как биты заёма и десятичного заёма соответственно,например при выполнении команд вычетания SUBLW и SUBWF. Флаг заёма имеет инверсное значение.Вычетание выполняется путём прибавления дополнительного кода второго операнда.При выполнении команд сдвига (RRF,RLF) бит С загружается старшим или младшим битом сдвигаемого регистра. |

||||

OPTION_REG (81h)

№-бита |

Вес бита |

Название бита |

Описание бита |

|

7 |

128 |

-RAPU |

Включение подтягивающих резисторов PORTA 1=отключены 0=включены |

R/W-1 |

6 |

64 |

INTEDG |

Выбор активного фронта сигнала на входе внешнего прерывания INT 1=прерывания по переднему фронту сигнала RA2/INT 0=прерывания по заднему фронту сигнала RA2/INT |

R/W-1 |

5 |

32 |

T0CS |

Выбор тактового сигнала для TMR0 1=внешний тактовый сигнал с вывода RA2/TOCKI 0=внутренний тактовый сигнал (CLKOUT) |

R/W-1 |

4 |

16 |

T0SE |

Выбор фронта приращения TMR0 при внешнем тактовом сигнале 1=приращение при переходе сигнала с “1” к “0”,на выводе RA2/TOCKI 0=приращение при переходе сигнала с “0” к “1”,на выводе RA2/TOCKI |

R/W-1 |

3 |

8 |

PSA |

Выбор включения предделителя 1=предделитель включен перед WDT 0=предделитель включен перед TMR0 |

R/W-1 |

2 |

4 |

PS2-PS0 |

Установка коэфициента деления предделителя 000=1:2 для TMR0=1:1 для WDT 001=1:4 для TMR0=1:2 для WDT 010=1:8 для TMR0=1:4 для WDT 011=1:16 для TMR0=1:8 для WDT 100=1:32 для TMR0=1:16 для WDT 101=1:64 для TMR0=1:32 для WDT 110=1:128 для TMR0=1:64 для WDT 111=1:256 для TMR0=1:128 для WDT |

R/W-1 |

1 |

2 |

|||

0 |

1 |

|||

Примечание: Если предварительный делитель включен перед WDT (3-й бит=1),то коэффициент деления тактового сигнала для TMR0 равен 1:1 |

||||

INTCON (0Bh или 8Bh)

№-бита |

Вес бита |

Название бита |

Описание бита |

|

7 |

128 |

GIE |

Глобальное разрешение прерываний 1=разрешены все немаскированные прерывания 0=все прерывания запрещены |

R/W-0 |

6 |

64 |

PEIE |

Разрешение прерываний от периферийных модулей 1=разрешены все немаскированные прерывания периферийных модулей 0=прерывания от периферийных модулей запрещены |

R/W-0 |

5 |

32 |

T0IE |

Разрешение прерывания по переполнению TMR0 1=прерывание разрешено 0=прерывание запрещено |

R/W-0 |

4 |

16 |

INTE |

Разрешение внешнего прерывания RA2/INT 1=прерывание разрешено 0=прерывание запрещено |

R/W-0 |

3 |

8 |

RAIE |

Разрешение прерывания по изменению сигнала на входах PORTA (Регистр IOCA также должен быть соответственно настроен) 1=прерывание разрешено 0=прерывание запрещено |

R/W-0 |

2 |

4 |

T0IF |

Флаг прерывания по переполнению TMR0 1=произошло переполнение TMR0 (сбрасывается програмно) 0=преполнения не было |

R/W-0 |

1 |

2 |

INTF |

Флаг внешнего прерывания RA2/INT 1= произошло внешнее перерывание RA2/INT (сбрасывается програмно) 0=внешнего прерывания небыло |

R/W-0 |

0 |

1 |

RAIF |

Флаг прерывания по изменению сигнала на входах PORTA 1=произошло изменение уровня сигнала на одном из входов PORTA (сбрасывается програмно) 0=не было изменения уровня сигнала ни на одном из входов PORTA |

R/W-0 |

Примечание: T0IF устанавливается в “1”,когда происходит переполнение TMR0,который не очищается при последующих сбросах,поэтому он должен быть заново инициализирован перед проверкой флага T0IF. |

||||

PIE1 (8Ch)

№-бита |

Вес бита |

Название бита |

Описание бита |

|

7 |

128 |

EEIE |

Разрешение прерывания по завершению цикла записи в EEPROM память данных 1=прерывание разрешено 0=прерывание запрещено |

R/W-0 |

6 |

64 |

ADIE |

Разрешение прерывания по завершению преобразования АЦП (только в 16F676) 1=прерывание разрешено 0=прерывание запрещено |

R/W-0 |

5 |

32 |

- |

Не используется: читается как “0” |

- |

4 |

16 |

- |

Не используется: читается как “0” |

- |

3 |

8 |

CMIE |

Разрешение прерывания от модуля компаратора 1=прерывание разрешено 0=прерывание запрещено |

R/W-0 |

2 |

4 |

- |

Не используется: читается как “0” |

- |

1 |

2 |

- |

Не используется: читается как “0” |

- |

0 |

1 |

TMR1IE |

Разрешение прерывания по переполнению TMR1 1=прерывание разрешено 0=прерывание запрещено |

R/W-0 |

Примечание: Чтобы разрешить перефирийные прерывания,необходимо установить в “1” бит PEIE регистра INTCON. |

||||

PIR1 (0Ch)

№-бита |

Вес бита |

Название бита |

Описание бита |

|

7 |

128 |

EEIF |

Флаг прерывания по завершению цикла записи в EEPROM память данных 1= запись в EEPROM завершена (сбрасывается програмно) 0= запись в EEPROM не завершена или не была начата |

R/W-0 |

6 |

64 |

ADIF |

Флаг прерывания по завершению преобразования АЦП (только в 16F676) 1= преобразования АЦП завершено (сбрасывается програмно) 0= преобразования АЦП не завершено |

R/W-0 |

5 |

32 |

- |

Не используется: читается как “0” |

- |

4 |

16 |

- |

Не используется: читается как “0” |

- |

3 |

8 |

CMIF |

Флаг прерывания от модуля компаратора 1=изменился уровень сигнала на входе компаратора(сбрасывается програмно) 0= уровень сигнала на входе компаратора не менялся |

R/W-0 |

2 |

4 |

- |

Не используется: читается как “0” |

- |

1 |

2 |

- |

Не используется: читается как “0” |

- |

0 |

1 |

TMR1IF |

Флаг прерывания по переполнению TMR1 1=произошло переполнение (сбрасывается програмно) 0=преполнения не было |

R/W-0 |

Примечание: Флаги прерываний устанавливаются при возникновении условий прерываний вне зависимости от соответствующих битов разрешения и бита общего разрешения прерываний GIE регистра INTCON. Програмное обеспечение пользователя должно сбрасывать соответствующие флаги при обработке переферийных прерываний. |

||||

PCON (8Eh)

№-бита |

Вес бита |

Название бита |

Описание бита |

|

7 |

128 |

- |

Не используется: читается как “0” |

- |

6 |

64 |

- |

Не используется: читается как “0” |

- |

5 |

32 |

- |

Не используется: читается как “0” |

- |

4 |

16 |

- |

Не используется: читается как “0” |

- |

3 |

8 |

- |

Не используется: читается как “0” |

- |

2 |

4 |

- |

Не используется: читается как “0” |

- |

1 |

2 |

-POR |

Флаг сброса по включению питания,по сигналу на выводе MCLR или по переполнению сторожевого таймера WDT (программно должен быть установлен в “1”,для обнаружения сброса) 1=сброса не было 0= сброс был |

R/W-0 |

0 |

1 |

-BOD |

Флаг сброса по снижению напряжения питания (программно должен быть установлен в “1”,для обнаружения сброса) 1=сброса не было 0= сброс был |

R/W-x |

OSCCAL (90h)

№-бита |

Вес бита |

Название бита |

Описание бита |

|

7 |

128 |

CAL5 |

CAL5-CAL0 шести-разрядная константа коррекции частоты внутреннего генератора 4Мгц 111 111=максимальная частота 100 000=средняя частота 000 000=минимальная частота |

R/W-0 |

6 |

64 |

CAL4 |

||

5 |

32 |

CAL3 |

||

4 |

16 |

CAL2 |

||

3 |

8 |

CAL1 |

||

2 |

4 |

CAL0 |

||

1 |

2 |

- |

Не используется: читается как “0” |

- |

0 |

1 |

- |

Не используется: читается как “0” |

- |

PORTA (05h)

№-бита |

Вес бита |

Название бита |

Описание бита |

|

7 |

128 |

- |

Не используется: читается как “0” |

- |

6 |

64 |

- |

Не используется: читается как “0” |

- |

5 |

32 |

RA5 |

Входы или выходы (в зависимости от настройки регистра TRISA) Соответствуюющие названию бита выводы микроконтроллера |

R/W-x |

4 |

16 |

RA4 |

||

3 |

8 |

RA3 |

||

2 |

4 |

RA2 |

||

1 |

2 |

RA1 |

||

0 |

1 |

RA0 |

TRISA (85h)

№-бита |

Вес бита |

Название бита |

Описание бита |

|

7 |

128 |

- |

Не используется: читается как “0” |

- |

6 |

64 |

- |

Не используется: читается как “0” |

- |

5 |

32 |

TRISA5 |

Вывод RA5: 1=работает как вход, 0=работает как выход |

R/W-x |

4 |

16 |

TRISA4 |

Вывод RA4: 1=работает как вход, 0=работает как выход |

|

3 |

8 |

TRISA3 |

Вывод RA3: Работает только как вход и всегда читается как “1” |

R-1 |

2 |

4 |

TRISA2 |

Вывод RA2: 1=работает как вход, 0=работает как выход |

R/W-x |

1 |

2 |

TRISA1 |

Вывод RA1: 1=работает как вход, 0=работает как выход |

|

0 |

1 |

TRISA0 |

Вывод RA0: 1=работает как вход, 0=работает как выход |

WPUA (95h)

№-бита |

Вес бита |

Название бита |

Описание бита |

|

7 |

128 |

- |

Не используется: читается как “0” |

- |

6 |

64 |

- |

Не используется: читается как “0” |

- |

5 |

32 |

WPUA5 |

Подключение подтягивающего резистора,при работе на вход: 1-вкл.,0-выкл. |

R/W-1 |

4 |

16 |

WPUA4 |

Подключение подтягивающего резистора,при работе на вход: 1-вкл.,0-выкл. |

|

3 |

8 |

- |

Не используется: читается как “0” |

- |

2 |

4 |

WPUA2 |

Подключение подтягивающего резистора,при работе на вход: 1-вкл.,0-выкл. |

R/W-1 |

1 |

2 |

WPUA1 |

Подключение подтягивающего резистора,при работе на вход: 1-вкл.,0-выкл. |

|

0 |

1 |

WPUA0 |

Подключение подтягивающего резистора,при работе на вход: 1-вкл.,0-выкл. |

|

Примечание: Подтягигивающий резистор автоматически отключается при настройке вывода на выход. Подтягивающие резисторы на всех входах отключаются при сбросе по включению питания,а так же управляются битом –RAPU регистра OPTION_REG. |

||||

IOCA (96h)

№-бита |

Вес бита |

Название бита |

Описание бита |

|

7 |

128 |

- |

Не используется: читается как “0” |

- |

6 |

64 |

- |

Не используется: читается как “0” |

- |

5 |

32 |

IOCA5 |

Разрешение прерывания на входе RA5: 1=разрешено, 0=запрещено |

R/W-0 |

4 |

16 |

IOCA4 |

Разрешение прерывания на входе RA4: 1=разрешено, 0=запрещено |

|

3 |

8 |

IOCA3 |

Разрешение прерывания на входе RA3: 1=разрешено, 0=запрещено |

|

2 |

4 |

IOCA2 |

Разрешение прерывания на входе RA2: 1=разрешено, 0=запрещено |

|

1 |

2 |

IOCA1 |

Разрешение прерывания на входе RA1: 1=разрешено, 0=запрещено |

|

0 |

1 |

IOCA0 |

Разрешение прерывания на входе RA0: 1=разрешено, 0=запрещено |

|

Примечание: Для индивидуального разрешения прерываний по изменению уровня сигнала на входах RA5-RA0, должны быть глобально разрешены прерывания,битом GIE регистра INTCON и разрешены прерывания по изменению уровня сигнала на входах,битом RAIE регистра INTCON. |

||||

PORTC (07h)

№-бита |

Вес бита |

Название бита |

Описание бита |

|

7 |

128 |

- |

Не используется: читается как “0” |

- |

6 |

64 |

- |

Не используется: читается как “0” |

- |

5 |

32 |

RC5 |

Входы или выходы (в зависимости от настройки регистра TRISC) Соответствуюющие названию бита выводы микроконтроллера |

R/W-x |

4 |

16 |

RC4 |

||

3 |

8 |

RC3 |

||

2 |

4 |

RC2 |

||

1 |

2 |

RC1 |

||

0 |

1 |

RC0 |

TRISC (87h)

№-бита |

Вес бита |

Название бита |

Описание бита |

|

7 |

128 |

- |

Не используется: читается как “0” |

- |

6 |

64 |

- |

Не используется: читается как “0” |

- |

5 |

32 |

TRISC5 |

Вывод RC5: 1=работает как вход, 0=работает как выход |

R/W-1

|

4 |

16 |

TRISC4 |

Вывод RC4: 1=работает как вход, 0=работает как выход |

|

3 |

8 |

TRISC3 |

Вывод RC3: 1=работает как вход, 0=работает как выход |

|

2 |

4 |

TRISC2 |

Вывод RC2: 1=работает как вход, 0=работает как выход |

|

1 |

2 |

TRISC1 |

Вывод RC1: 1=работает как вход, 0=работает как выход |

|

0 |

1 |

TRISC0 |

Вывод RC0: 1=работает как вход, 0=работает как выход |

T1C0N (10h)

№-бита |

Вес бита |

Название бита |

Описание бита |

|

7 |

128 |

- |

Не используется: читается как “0” |

- |

6 |

64 |

TMR1GE |

Разрешение выключения TMR1 по сигналу с входа -T1G При бите TMR1ON=1: значение этого бита игнорируется. При бите TMR1ON=0: 1=таймер TMR1 включен,если на входе -T1G низкий логический уровень. 0=таймер TMR1 включен |

R/W-1 |

5 |

32 |

T1CKPS1

|

Выбор коэфициента деления предделителя TMR1 11=1:8 10=1:4 01=1:2 00=1:1 |

|

4 |

16 |

T1CKPS0 |

||

3 |

8 |

T1OSCEN |

Включение тактового генератора TMR1 Режим тактового генератора INTOSC без CLKOUT: 1=тактовый LP генератор TMR1 включен. 0= LP генератор выключен. Другие режимы тактового генератора микроконтроллера: значение этого бита игнорируется. |

|

2 |

4 |

-T1SYNC |

Синхонизация внешнего тактового сигнала. При бите TMR1CS=1: 1=не синхронизировать внешний тактовый сигнал. 0=не синхронизировать. При бите TMR1CS=0: значение этого бита игнорируется. TMR1 использует внутренний тактовый сигнал. |

|

1 |

2 |

TMR1CS |

Выбор источника тактового сигнала 1=внешний источник с вывода T1OSO/T1CKI (активным является передний фронт сигнала) 0=внутренний источник (Fosc/4) |

|

0 |

1 |

TMR1ON |

Включение модуля TMR1 1= TMR1 включен 0= TMR1 выключен |

CMCON (19h)

№-бита |

Вес бита |

Название бита |

Описание бита |

|

7 |

128 |

- |

Не используется: читается как “0” |

- |

6 |

64 |

COUT |

Выход компаратора Если CINV=0: 1=VIN+ > VIN- 0=VIN+ < VIN- Если CINV=1: 0=VIN+ > VIN- 1=VIN+ < VIN- |

R-0 |

5 |

32 |

- |

Не используется: читается как “0” |

- |

4 |

16 |

CINV |

Режим выхода компаратора 1=инверсный выход 0=не инверсный выход |

R/W-0 |

3 |

8 |

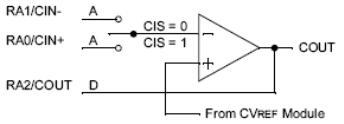

CIS |

Подключение входа компаратора Когда CM2:CM0=101 или CM2:CM0=110 1= VIN- подключен к CIN+ 0= VIN- подключен к CIN- |

|

2 |

4 |

CM2 |

Режим работы копаратора: Сброс компаратора (после сброса POR) CM2:CM0=000

Компаратор выключен CM2:CM0=111

Компаратор без внешнего выхода CM2:CM0=010

Компаратор с внутренним ИОН без внешнего выхода CM2:CM0=100

Компаратор с внутренним ИОН и внешним выходом CM2:CM0=011

Компаратор с внутренним ИОН ,внешним выходом и мултиплексируемым входом CM2:CM0=101

Компаратор с внешним выходом CM2:CM0=001

Компаратор с внутренним ИОН и мултиплексируемым входом CM2:CM0=110

|

|

1 |

2 |

CM1 |

||

0

|

1 |

CM0 |

||

Примечание: Для использования компаратора необходимо настроить соответствующие выводы как аналоговые |

||||

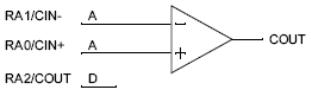

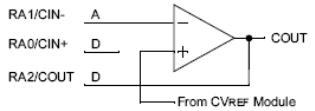

Блок-схема модуля компаратора

Примечание: При чтении регистра PORTA ,все выводы настроенные как аналоговые,будут читатся как “0”. Выводы,настроенные как цифровые входы,конвертируют аналоговый сигнал согласно характеристикам входного буфера. Аналоговые уровни сигналов,подаваемые на цифровые входы,могут быть причиной повышенного энергопотребления. |

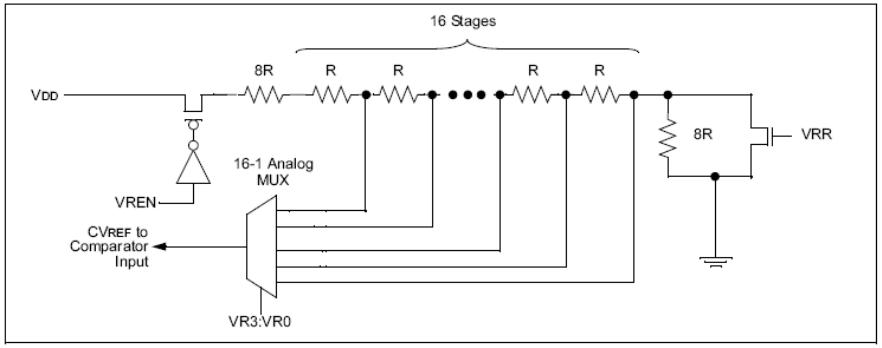

Источник опорного напряжения.

VRCON (99h)

№-бита |

Вес бита |

Название бита |

Описание бита |

|

7 |

128 |

VREN |

Включение источника опорного напряжения 1=включен 0=выключен и не потребляет тока |

R/W-0 |

6 |

64 |

- |

Не используется: читается как “0” |

- |

5 |

32 |

VRR |

Диапазон выходного напряжения ИОН (CVREF) 1=нижний диапазон 0=верхний диапазон |

R/W-0 |

4 |

16 |

- |

Не используется: читается как “0” |

- |

3 |

8 |

VR3 |

Вабор выходного напряжения ИОН (CVREF) Если бит VRR=1 то CVREF = (VR<3:0>/24)xVDD Если бит VRR=0 то CVREF = (VDD x 1/4)+(VR<3:0>/32)xVDD |

R/W-0 |

2 |

4 |

VR2 |

||

1 |

2 |

VR1 |

||

0 |

1 |

VR0 |

Модуль ацп (только в pic16f676)

ADCON0 (1Fh)

№-бита |

Вес бита |

Название бита |

Описание бита |

|

7 |

128 |

ADFM |

Формат сохранения 10-разрядного результата 1=правое выравнивание 0=левое выравнивание |

R/W-0 |

6 |

64 |

VCFG |

Выбор источника опорного напряжения 1=вывод VREF 0=напряжение питания VDD |

|

5 |

32 |

- |

Не используется: читается как “0” |

- |

4 |

16 |

CHS2 |

CHS2:CHS0 Выбор аналогово канала 000=канал 00 (AN0) 001=канал 01 (AN0) 010=канал 02 (AN0) 011=канал 03 (AN0) 100=канал 04 (AN0) 101=канал 05 (AN0) 110=канал 06 (AN0) 111=канал 07 (AN0) |

R/W-0 |

3 |

8 |

CHS1 |

||

2 |

4 |

CHS0 |

||

1 |

2 |

GO/-DONE |

Бит статуса модуля АЦП 1=модуль АЦП выполняет преобразование (установка бита вызывает начало преобразования) 0=состояние ожидания (аппаратно сбрасывается по завершению преобразования) |

|

0 |

1 |

ADON |

Бит включения модуля АЦП 1=включен 0=выключен и не потребляет тока |

ANSEL (9Fh)

№-бита |

Вес бита |

Название бита |

Описание бита |

|

7 |

128 |

- |

Не используется: читается как “0” |

- |

6 |

64 |

ADS2 |

Выбор источника тактового сигнала 000=FOSC/2 001=FOSC/8 010=FOSC/32 X11=FOSC/(отдельный внутренний RC генератор.Максимальная F=500кГц 100=FOSC/4 101=FOSC/16 110=FOSC/64 |

R/W-0 |

5 |

32 |

ADS1 |

||

4 |

16 |

ADS0 |

||

3 |

8 |

- |

Не используется: читается как “0” |

- |

2 |

4 |

- |

Не используется: читается как “0” |

- |

1 |

2 |

- |

Не используется: читается как “0” |

- |

0 |

1 |

- |

Не используется: читается как “0” |

- |