- •Вычислительные машины, системы и сети

- •Тема 1. Введение в предмет

- •Умножение чисел в дополнительных кодах

- •Операция умножения над обратными кодами сомножителей

- •Выполнение операции сложения над числами с плавающей запятой

- •6. Стадии выполнения команды и способы адресации

- •Тема 2. Оcновные архитектурные понятия Лекция 4. Определение понятия "архитектура"

- •Архитектура системы команд. Классификация процессоров (cisc и risc)

- •Лекция 5. Методы адресации и типы данных Методы адресации

- •Типы команд

- •Команды управления потоком команд

- •Типы и размеры операндов

- •Тема 3. Функциональная структура и организация процессора

- •Структура конвейера процессора р6

- •Процессор Pentium Pro

- •Характеристики процессоров р6

- •Характеристики процессоров amd

- •Форматы чисел блоков sse

- •Лекция 12: Сравнительный анализ процессоров с различной архитектурой Особенности процессоров с архитектурой sparc компании Sun Microsystems

- •Процессоры pa-risc компании Hewlett-Packard

- •Процессор mc88110 компании Motorola

- •Особенности архитектуры Alpha компании dec

- •Особенности архитектуры power компании ibm и PowerPc компаний Motorola, Apple и ibm

- •Архитектура power

- •Эволюция архитектуры power в направлении архитектуры PowerPc

- •Тема 4. Структурные модели современных системных плат

- •Тема 5. Организация памяти в эвм

- •2. Постоянные и полупостоянные запоминающие устройства

- •3. Оперативные запоминающие устройства

- •4. Характеристики обмена и типы оперативной памяти

- •7. Сегментация памяти

- •8. Страничная организация памяти

- •Тема 6. Организация ввода-вывода

- •Системные и локальные шины

- •Устройства ввода/вывода Основные типы устройств ввода/вывода

- •2.1. Шины микропроцессорной системы

- •2.2. Циклы обмена информацией

- •2.3. Прохождение сигналов по магистрали

- •Тема 2. Оценка производительности вычислительных систем

- •Тема 5. Многопроцессорные системы Лекция 18: Классификация систем параллельной обработки данных

- •Многопроцессорные системы с общей памятью

- •Многопроцессорные системы с локальной памятью и многомашинные системы

- •Тема 9. Организация микроконтроллеров

- •4.1. Классификация и структура микроконтроллеров

- •4.2. Процессорное ядро микроконтроллера

- •Тема 10. Однокристальные микроконтроллеры серии pic

- •5.1. Основные особенности микроконтроллеров серии pic

- •5.2. Микроконтроллеры подгруппы pic16f8x

- •Тема 11. Проектирование устройств на микроконтроллерах

- •6.1. Разработка микропроцессорной системы на основе микроконтроллера

- •Тема 12. Системы высокой готовности и отказоустойчивые системы

- •Подсистемы внешней памяти высокой готовности

- •Требования, предъявляемые к системам высокой готовности

- •Конфигурации систем высокой готовности

- •Требования к системному программному обеспечению

- •Требования высокой готовности к прикладному программному обеспечению

- •Требования к сетевой организации и к коммуникациям

- •Базовая модель vax/vms кластеров

- •Критерии оценки кластеров Gartner Group

- •Кластеры Alpha/osf компании dec

- •Unix-кластеры компании ibm

- •Кластеры at&t gis

- •Кластеры Sequent Computer Systems

- •Системы высокой готовности Hewlett-Packard

- •Кластерные решения Sun Microsystems

- •Отказоустойчивые решения Data General

- •Список сокращений

3. Оперативные запоминающие устройства

Для построения ОЗУ большой емкости используются элементы статической или динамической памяти, которые строятся на простейших элементах транзисторно-транзисторной логики (ТТЛ), инжекционной логики (И2Л), эмиттерносвязной логики (ЭСЛ) и других технологий [5].

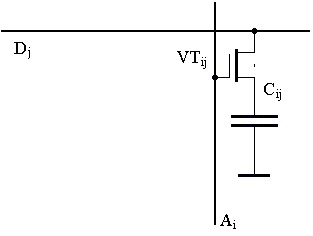

В основе динамических ОЗУ (DRAM) используется заряд межэлектродных конденсаторов Cij емкостью менее 0.1 пФ и током заряда менее 10-10 А. Схема i-го разряда ячейки памяти динамического ОЗУ (DRAM) представлена на рис. 3.3. Для записи логической “1” в элемент памяти активизируются информационная шина Dj и адресная шина Аi. При этом униполярный (полевой) транзистор открывается и через него конденсатор Cij заряжается. При отсутствии открывающего напряжения на шине Аi транзистор закрыт, конденсатор Cij заряжен и хранит информацию. При подаче напряжения чтения на шину Аi транзистор VTij открывается и напряжение конденсатора Cij подается на шину Dj, и он разряжается. Ток разряда Cij усиливается и фиксируется в информационном регистре ОЗУ.

Dj

VTij

Cij

Ai

Рис. 3.3. Элемент динамического ОЗУ

Для устранения искажений информации в результате утечки заряда с конденсатора элементы памяти периодически, через 2 мс или более, в зависимости от типа ИС, необходимо перезаряжать в цикле регенерации. Преимуществом динамических ОЗУ является высокая степень интеграции элементов памяти и малая потребляемая мощность. Недостатком их является большое время доступа 50-70 нс по сравнению со статической памятью, где оно равно менее 15 нс.

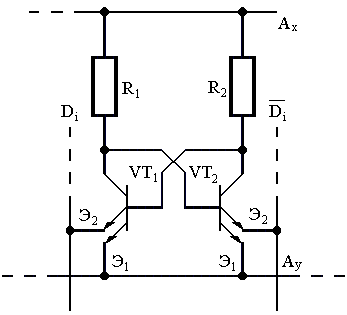

Статическая

оперативная память (SRAM) строится на

быстродействующих биполярных транзисторах,

например, двухэмиттерных транзисторах

TTL (рис. 3.4). В режиме хранения информации

между шинами Аx

и Аy

поддерживается минимальное напряжение

(около 0.2 В), сохраняя один из транзисторов

открытым (логический “0”), другой

закрытым (логическая “1”). На обоих

проводах информационной парафазной

шины (![]() )

устанавливается положительное напряжение,

которое обеспечивает нулевой ток через

эмиттеры Э2.

Элемент памяти (ЭП) находится в пассивном

режиме хранения информации с наименьшим

уровнем потребления энергии.

)

устанавливается положительное напряжение,

которое обеспечивает нулевой ток через

эмиттеры Э2.

Элемент памяти (ЭП) находится в пассивном

режиме хранения информации с наименьшим

уровнем потребления энергии.

Рис. 3.4. Элемент статического ОЗУ

В режиме чтения информации шины Аx и Аy возбуждаются и на них подаются потенциалы, обеспечивающие быстрое чтение разных токов, поступающих с эмиттеров Э2 на провода в усилитель чтения. В зависимости от величины токов в проводах, после их усиления триггер Т2 (см. рис. 3.5, а) информационного регистра ОЗУ устанавливается в “1” или “0”. При этом состояние ЭП не изменяется и он может быть переведен в режим хранения предыдущего состояния.

Для

записи информации в бистабильный ЭП

возбуждаются адресные шины Аx

и Аy

и соответствующий

один провод

![]() или

или

![]() под действием управления с усилителя

записи. Противоположный возбужденному

проводу

(

)

транзистор VT1

(VT2)

открывается, т.к. через его эмиттер Э2

протекает больший ток под действием

большей разности потенциалов

под действием управления с усилителя

записи. Противоположный возбужденному

проводу

(

)

транзистор VT1

(VT2)

открывается, т.к. через его эмиттер Э2

протекает больший ток под действием

большей разности потенциалов

![]() .

ЭП переходит в устойчивое состояние:

VT1

открыт, а VT2

закрыт.

.

ЭП переходит в устойчивое состояние:

VT1

открыт, а VT2

закрыт.

На статических и динамических ЭП изготавливают ИС различной емкости и разрядности. На рис. 3.5, б приведена типичная ИС емкостью

N = 2L = m n (бит).

Массив ЭП состоит из n строк и m столбцов. Каждый ЭП хранит один бит информации.

а б

Рис. 3.5. Структура ИС ОЗУ: а – 1- битная схема ОЗУ, б – обобщенная схема ОЗУ

Адрес ЭП, участвующего в операции чтения /записи, определяется L-разрядным двоичным кодом, поступающим с шины адреса ША в регистр адреса RGA. Младшие l1 разряда адреса в режиме чтения или записи информации в ОЗУ с появлением сигнала выборки строки RAS поступают на дешифратор строк DCx. Старшие l2 разряда адреса с появлением сигнала выборки столбца CAS поступают на дешифратор столбцов DCy.

В

соответствии с двоичным кодом адреса

каждый из дешифраторов возбуждает

только одну выходную шину. На пересечении

возбужденных шин Аx

и Аy

соответствующий ЭП подключается к

внутренней информационной парафазной

шине

![]() .

.

В режиме записи (W=0, CAS=0, RAS=0) УУ включает усилитель записи (УЗ) и подсоединяет его к шине . Одновременно к шине дешифраторами DCx и DCy подключается один ЭП, который УЗ устанавливается в устойчивое состояние, задаваемое триггером Т1. Триггер Т1 перед началом записи воспринимает один бит информации через коммутатор К с внешней шины данных ШД.

В режиме чтения (W=1, RAS=0, CAS=0) УУ отключает УЗ от шины и подключает к ней усилитель чтения (УЧ). Одновременно выход триггера Т2 через К подсоединяется к ШД. В соответствии с кодом адреса усилителем чтения (УЧ) устанавливается состояние триггера Т2, соответствующее состоянию возбужденному ЭП дешифраторами DCx и DCy. В следующий момент времени информация с триггера Т2 передается на ШД.

При

хранении информации (CAS=RAS=1) коммутатор

К отключает от ШД ОЗУ. На всех шинах Аx,

Аy,

![]() устанавливаются потенциалы, обеспечивающие

пассивный режим сохранения состояний

ЭП.

устанавливаются потенциалы, обеспечивающие

пассивный режим сохранения состояний

ЭП.