- •27. Операционные усилители

- •28. Инвертирующий усилитель

- •29. Неинвертирующий усилитель

- •32.Электронные ключи. Параметры и характеристики

- •34. Улучшенные схемы ключей на бт

- •35 Ключ на переключателе тока

- •37. Комплементарный ключ

- •38 Семейства логических элементов

- •Преимущества и недостатки

- •42. Кмоп-логика

- •43 Триггерная ячейка

- •44.Триггер с разделённым входом

- •50 Мультиплексоры

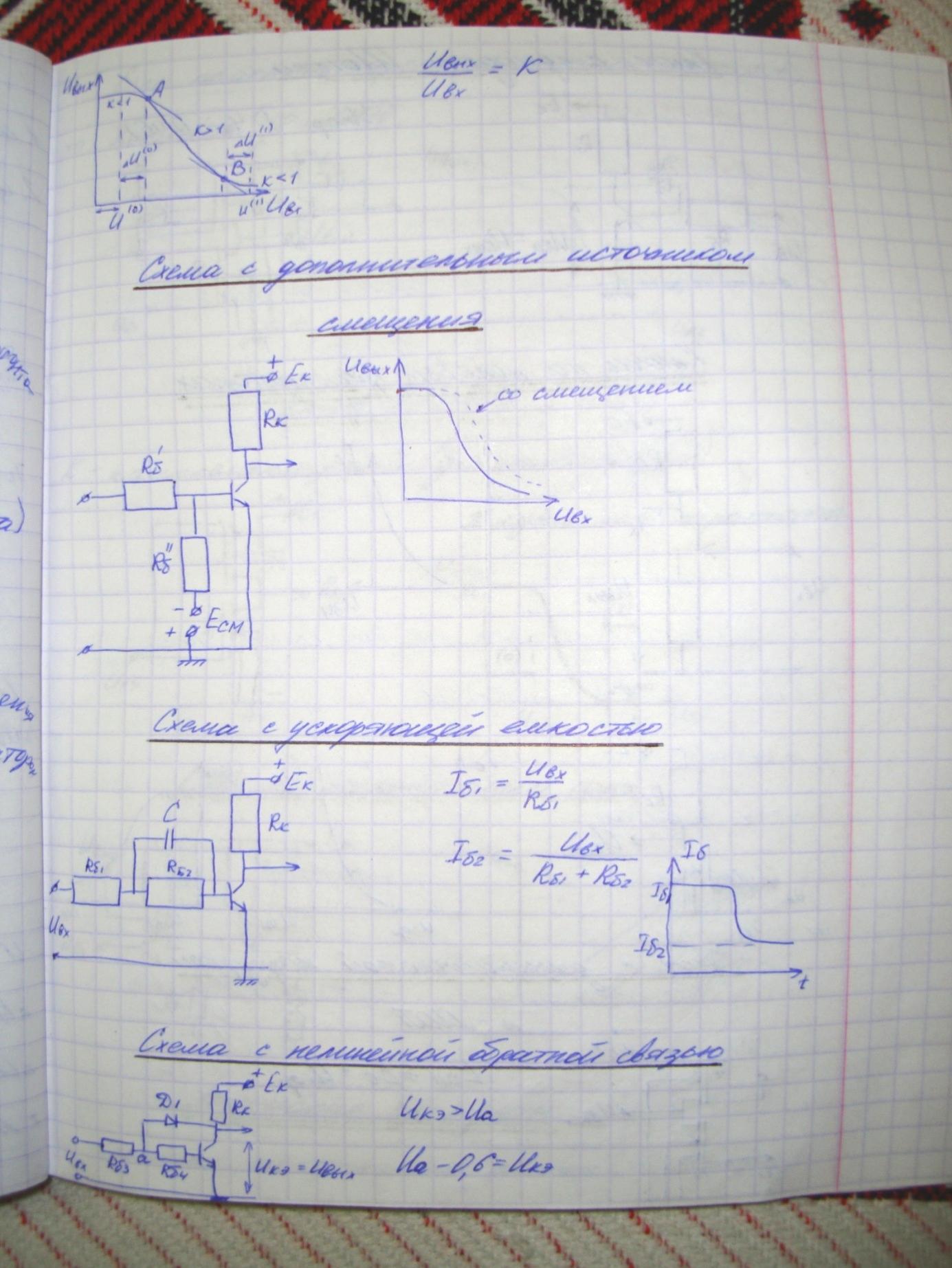

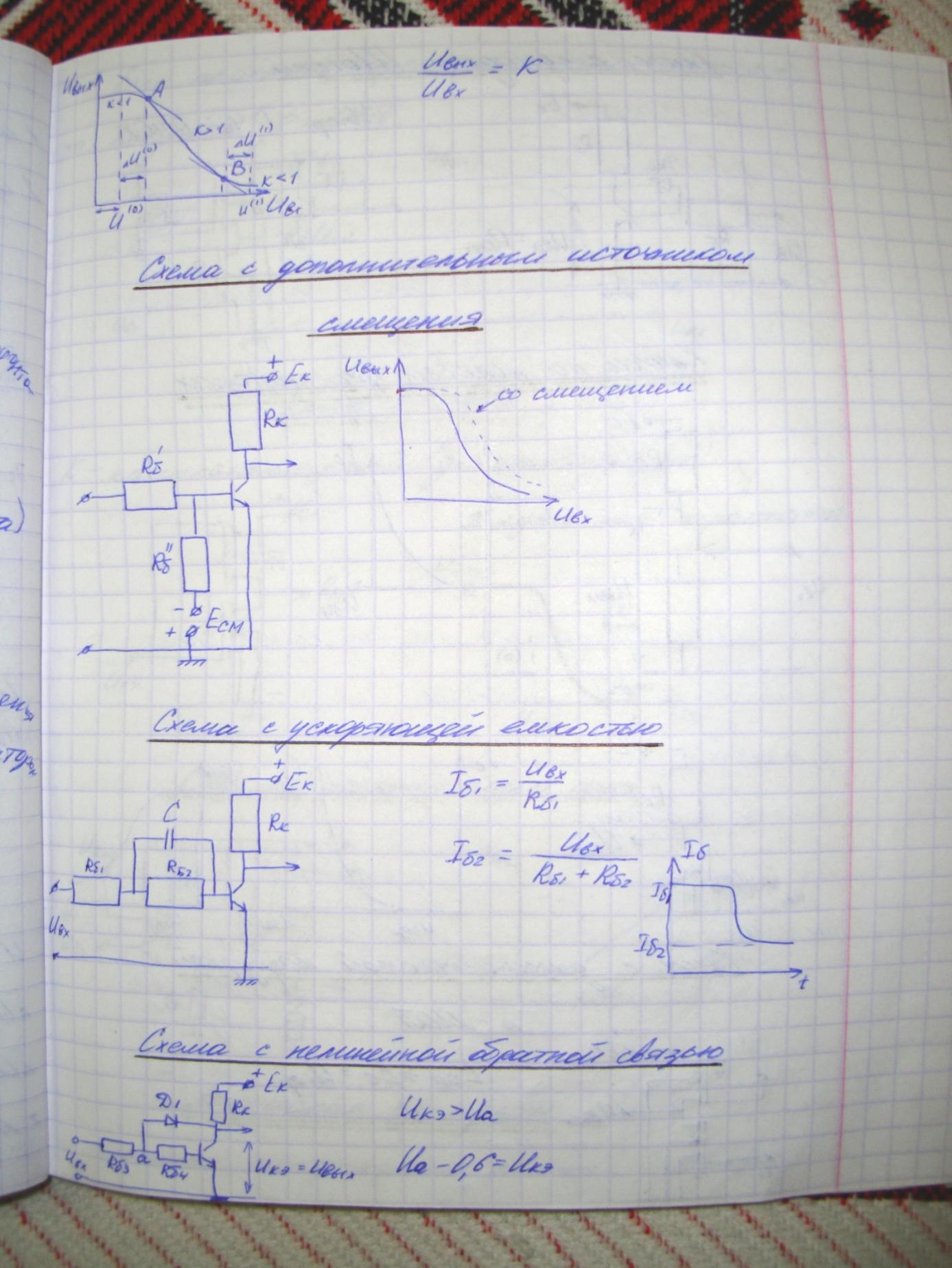

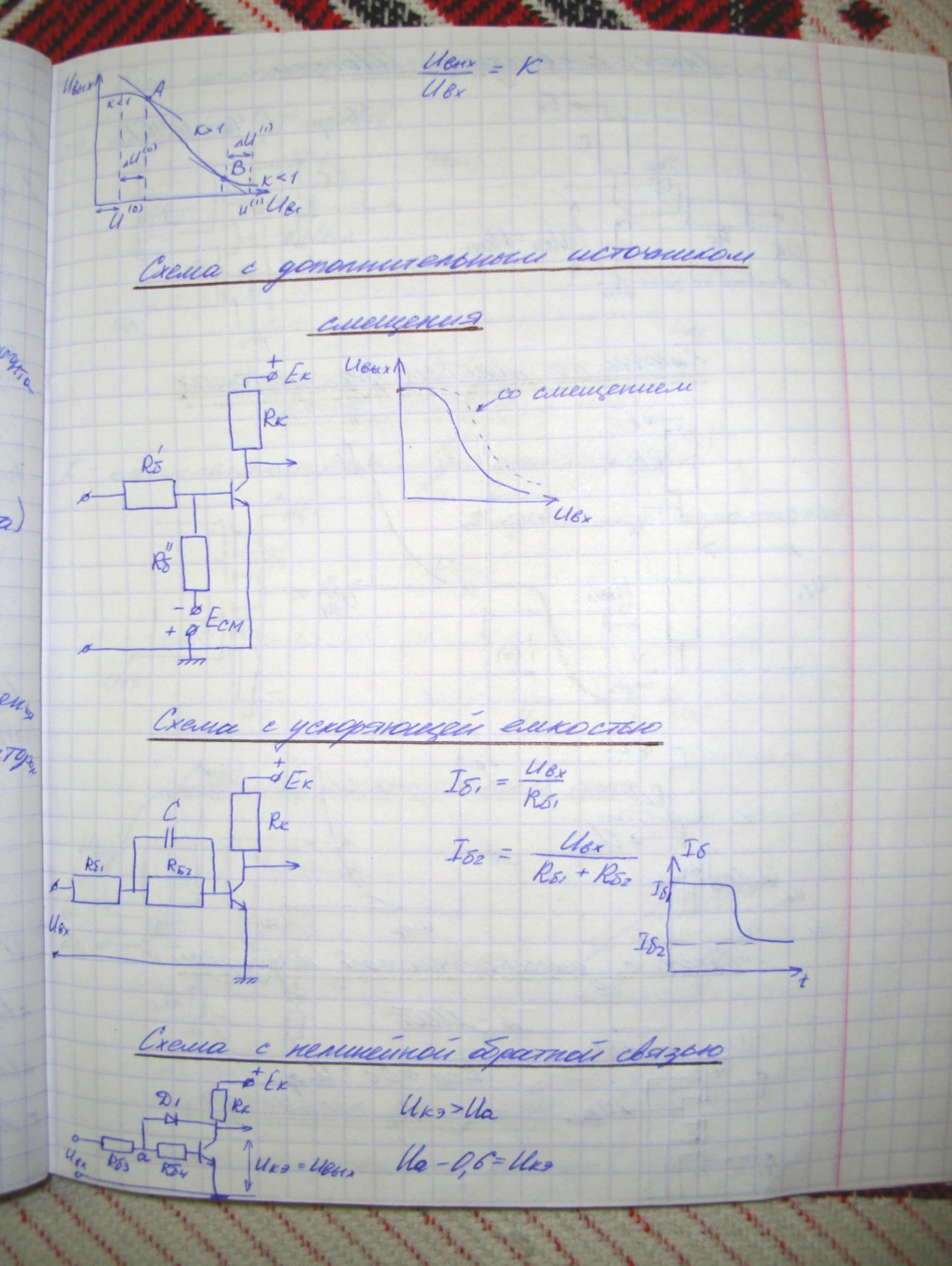

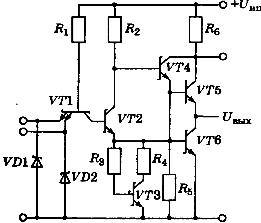

34. Улучшенные схемы ключей на бт

Схема с дополнительным источником смещения.

Схема с ускоряющей емкостью

Схема с нелинейной обратной связью

35 Ключ на переключателе тока

36. Ключи на полевых транзисторах (ПТ)

Для построения эл. ключей на ПТ исп. тр-ры обогащенного и обедненного типов. При этом часто вместо резистора в цепи стока исп. такой же ПТ, и ключ с тр-ром С-цепи наз. тр-ром с динамичн нагрузкой.

В данном ключе тр-тор VT1 наз. ключевым тр-ром, а тр-тор VT2 наз. нагрузочным тр-ром. При аналитич анализе такой схемы ключа на стат. хар-ках строят нагрузочную прямую, т.к. нагрузочный тр-тор представляет собой нелин эл-т, т.к. тр-тор VT2 работает на пологом участке. При этом на затвор VT2 подается дополнит смещение.

Недостатки: -ключевой и нагрузочный тр-ры практически всегда открыты, и через них протекает ток. Схема в стат. режиме потребляет относит большую P, чем ИП. Для исключения Uсм часто затвор VT2 соед с ИП. (схема пунктиром) такие Эл ключи им сущ. недостатки: 1) потребление Р в стат. режиме

2) относит большее Uостаточное, т.е. большее значение логич «0» (0,5-1В)

37. Комплементарный ключ

Для увелич быстродействия и уменьшения потребл Р в стат. режиме эл ключи строятся на комплементарных парах (-пара ПТ, различ типом проводимостей канала)

В данной схеме ключевой тр-тор – это тр-р с каналом n-типа, а нагрузочный с каналом р-типа.

При послед вкл-ии тр-ров сток ключевого тр-ра соед со стоком нагрузочного тр-ра, а управление тр-рами вх сигналом явл противоположным. При подаче небольшого Uвх ключевой тр-р открывается, а нагрузочный закрыт, т.к. на затвор действует большой положит потенциал.

Ток, протекаемый в послед цепи тр-ра, определяется током закрытого тр-ра. При подаче на вход большого положит сигнала происходит открывание нагрузочного тр-ра, а ключевой тр-р закрывается, через послед цепь тр-ра протекает небольшой ток.

Сам ключ потребляет Р только в режиме переключения, а передат хар-ка такого ключа близка к прямоуг форме. Малое потребление Р относит высокое быстродействие позволяет исп-ть ключи на комплементарных тр-рах для создания КМОП-логики.

38 Семейства логических элементов

Логическими элементами(ЛЭ) наз. функциональные устройства, предназначенные для выполнения элементарных логических функций.С их помощью выполняется построение преобразователей цифровых сигналов комбинационного типа, которые реализуют сложные логические функции. Основными параметрами ЛЭ , которые являются общими для всех существующих и возможных логических интегральных микросхем явл. :

- реализуемая логическая функция

- быстродействие

-коэффициент объединения по входу

- коэффициент разветвления по выходу(нагрузочная способность)

- коэффициент объединения по выходу

-помехоустойчивость

-потребляемая мощность

-устойчивость против внешних воздействий

-степень интеграции, надежность.

Быстродейсдвие ИМС определяется след. параметрами: время переходя из состояния «1» в «0» t 1,0 ; время перехода из состояния «0» в состояние «1» t 0,1 ; время задержки включения tзд1,0 ; время задержки выключения tзд0,1 время задержки распространения сигнала при включении (при выключении); среднее время задержки распространения сигнала t зд р ср = 0,5 (tзд р0,1 + tзд р1,0 ).

По среднему времени задержки ИС делятся на:

сверхбысдродействующие

быстродействующие

среднего быстродействия

низкого быстродействия .

Коэффициент объединения по входу — это максимальное число входов, которое может иметь логический элемент. С увеличением коэффициента объединения но входу расширяются логические возможности микросхемы за счет выполнения функции с большим числом элементов на одном типовом элементе. Увеличение коэффициенда объединения но входу ухудшает другие параметры микросхемы: быстродейсдвие, помехоустойчивость, нагрузочную способность. Чаще всего коэффициент объединения не превышает 8.

Коэффициент разветвления по выходу К раз определяется числом схем этой же серии, входы которых могут быть подключены к выходу данной схемы без нарушения ее работоспособности. Чем выше К, тем шире возможности микросхемы и тем меньше число микросхем необходимо для построения сложного комбинац-ого устройства.

Помехоустойчивость U пом - максимально допустимое напряжение статической помехи на входе микросхемы, при котором еще не происходит изменения уровней ее выходного напряжения. Помехоустойчивость характеризует работоспособность логического элемента при наличии помех, действующих на входе ИМС наряду с полезными сигналом.

ПО уровню потребляемой мощности ИМС делятся на

- мощные 25<= P <= 250 мВт, средней мощности, маломощные, микромощные, нановаттные.

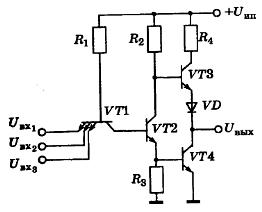

39. ТТЛ-, ТТЛШ-логика

Транзисторно-транзисторная логика (ТТЛ)

Она вып-ет лог. операцию И-НЕ и явл-ся усоверш-ем ДТЛ. Вместо лог. диодов у ТТЛ исп-ся многоэмит-е тр-ры, кот. объеденены ОБ и ОК. При этом эмит-е переходы многоэм. тр-ра вып-ют роль лог-х диодов, а диоды смещ-я вып-ют роль К-го пер-да.

Э л.

схема ТТЛ имеет вид:

л.

схема ТТЛ имеет вид:

Хар-ой особ-тью эл-овТТЛ явл-ся высокая по-

мехоуст-ть, большоебыстрод-е, малая потр.

мощность, высокая надёжность, малая стои-

мость.

Лог операцию И вып-ет VT1 и R1. Вых-я цепь

реализ-ет ф-ю НЕ и сод-ит сложный инвертор на тр-рах VT2...VT4. Он включ-ет в свой состав простой инвертор (VT2, R2) и эмит-й повтор-ль (VT3) с динамич. нагр-й (VT4), кот. упр-ся эмит-м током тр-ра VT2.

Принцип работы схемы: если хотя бы на один из входов под-ся напр. лог 0, то эмит-й пер. тр-ра VT1 откр-ся.Ток базы пмротек. во вх. цепь, при этом ток К VT1 ум-ся, К-й пер. откр-ся и тр-р VT1 нас-ся по К-й цепи. Напряж-е на вых. имеет выс-й уровень – лог 1.

Если на всех лог входах дейст-ют выс. уровни напр-я, то эмит-е пер. тр-ра VT1 закр-ся, он раб-ет в инверсном акт-ом режиме. Ток от ИП поступает в базу тр-ра VT2. VT2 и VT4 откр-ся и на вых. схемы им-ся уровень напряж-я, соотв-щий лог нулю. Тр-р VT3 и диод VD закрыты.

Транзисторно-транзисторная логика с барьером Шотки (ТТЛШ)

Для повыш-я быстрод-я исп-ют ТТЛШ.

В данной схеме диоды предназнач. для защиты от помех хода лог. эл-та,при этом диоды включ.в обратном напр-ии как для лог 0, так и для лог1.

На VT3 собран генератор тока для того, чтобы пол-ть передат.

хар-ку блише к прямоуг форме.

На базе VT4, VT5 собран составной тр-р для повышения тока вых. цепи инвертора. При этом VT5 обычный, а не с барьером Ш, ибо в сост. тр-ре быстрод-е опр-ся VT4, а ост. эл-ты инвертора вып-ют ту же ф-ю, что и обычный тр-р ТТЛ.

З а

счёт того, что тр-ры раб-ют на гране акт.

режима и режима насыщ-я, быстрод-е схемы

сост-ет 5-10 нанасек

а

счёт того, что тр-ры раб-ют на гране акт.

режима и режима насыщ-я, быстрод-е схемы

сост-ет 5-10 нанасек

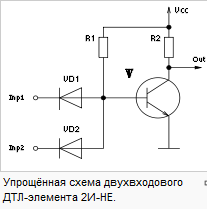

40.ДТЛ-логика

Диодно-транзисторная логика (ДТЛ) — технология построения цифровых схем на основе биполярных транзисторов, диодов и резисторов. Своё название технология получила благодаря реализации логических функций (например, 2И) с помощью диодных цепей, а усиления и инверсии сигнала — с помощью транзистора (для сравнения см. резисторно-транзисторная логика и транзисторно-транзисторная логика).

П ринцип

работы

ринцип

работы

Показанная на рисунке схема представляет собой типичный элемент 2И-НЕ: Если хотя бы на одном из входов уровень логического нуля, то ток течет через R1 и диод во входную цепь. На анодах диодов напряжение 0,7В, которого недостаточно для открывания транзистора. Транзистор закрыт. На выходе формируется уровень логической единицы. Если на все входы поступает уровень логической единицы, ток течет через R1 в базу транзистора, образуя на анодах диодов напряжение 1,4В. Поскольку напряжение уровня логической единицы больше этой величины входы диодов обратносмещены и не участвуют в работе схемы. Транзистор открыт в режиме насыщения. В транзистор втекает ток нагрузки по величине значительно больший тока нагрузки при уровне логической единицы.