- •27. Операционные усилители

- •28. Инвертирующий усилитель

- •29. Неинвертирующий усилитель

- •32.Электронные ключи. Параметры и характеристики

- •34. Улучшенные схемы ключей на бт

- •35 Ключ на переключателе тока

- •37. Комплементарный ключ

- •38 Семейства логических элементов

- •Преимущества и недостатки

- •42. Кмоп-логика

- •43 Триггерная ячейка

- •44.Триггер с разделённым входом

- •50 Мультиплексоры

Преимущества и недостатки

Основное преимущество ДТЛ над более ранней технологией РТЛ — возможность создания большого числа входов. Задержка прохождения сигнала по-прежнему достаточно высока, из-за медленного процесса утечки заряда с базы в режиме насыщения (когда все входы имеют высокий уровень) при подаче на один из входов низкого уровня. Эту задержку можно уменьшить подключением базы транзистора через резистор к общему проводу или к источнику отрицательного напряжения.

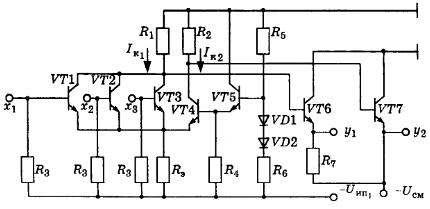

41. ЭСЛ-логика

Особ-ю ЭСЛ явл-ся то, что в них исп-ся не электрон. ключи, а переключат. тока. Переключ. тока имеют такую же принцип. схему, как и диф. каскады, только на один из входов под-ся опорное напряж-е и связь переключ. тока одного плеча и второго осущ-ся за счёт эмит-й связи, т.е. рез-ра, включ. в эмит-ю цепь переключателя. Схема имеет след. вид:

Перекл. тока собр. на VT3, VT4. Вх. с-лы под-ся в цепь Б тр-ра VT1, VT3. Для созд-я пути протекания обр. тока в цепи Б включ. р-ры Rб (50-240Ом). Опорн-е напряж-е на перекл. тока (VT4) созд-ся с пом. термостаб. цепочки VT5,R5, VD1,VD2,R6. Для повыш-я быстрод. в окон. каск-х исп. эмит. повтор-ли, собр. на VT6, VT7. Также для повыш. помехоуст-ти + ИП Э повт-й заземл-ся, а в цепь Э под-ся напр-е от доп-го напр-я смещ-я.

Предп, что на 1 или все 3 вх. подан неб вх. с-л –лог 0. Это приводит к тому, что 1 или все тр-ры под действ. вх. с-ла откр-ся. За счёт пад-я напр-я на р-ре Rэ VT4 закр-ся.

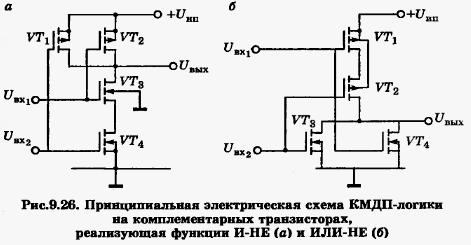

42. Кмоп-логика

Особ-ю КМОП-логики явл-ся: для выч-я логич. опер. ИЛИ-НЕ ключ. тр-ры VT3,VT4 включ. ||, а нагр. тр-ры VT1, VT2 послед. При этом упр-е вх. логич. с-ми нагр. и ключ. тр-ров противоположны.

Для вып-я лог. операции И-НЕ ключ. тр-ры включ. послед., а нагр. тр-ры ||. При этом упр-е ключ. и нагр. тр-ров противофазно и упр-е происх-т логич. с-ми, подав. на входы. При этом с-л на вых. будет только тогда, когда на всех лог входах одновр. действует одинак. по уровню с-л

Особ-ю КМОП логики явл-ся то, что она практ. не потр-ет мощность от ИП, а только потребляет её в режиме переключения.

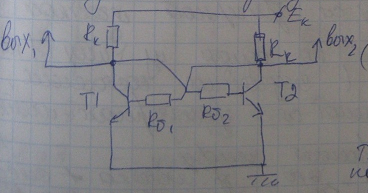

43 Триггерная ячейка

Пусть Т1 в режиме насыщения (R=0, Uкэ=0,1..0,2В, Iкб2=0) = > T2 – отсечка, т.е. два транзистора поддерживают друг друга, т.е. состояние устойчивое (также будет если Т1 – отсечка, Т2 – насыщение)

Пусть у Т1 и Т2

Пусть

в Т1 получили приращение ∆Iб1,

∆Iк1= ∆

Iб

∆

Iб

=-∆

=-∆ Rк=-∆

Iб*

*

Rк

Rк=-∆

Iб*

*

Rк

=(-∆Iб1*β*

Rк)/Rб

=(-∆Iб1*β*

Rк)/Rб

(-∆Iб1*β^2*

Rк)/Rб

(-∆Iб1*β^2*

Rк)/Rб

>>1

>>1

Ситуация самоподдерживаемости, если Т1 и Т2 в активном режиме, всё равно перейдём к устойчивому состоянию, где 1 – нас., 2 – отс., или наоборот.

Это называется триггерной ячейкой вых1 и вых2 на одном из них 1, на другом 0 (случайное состояние, когда включается триггерная ячейка. Ячейка хранит информацию. А триггерная ячейка+система управления = триггер.

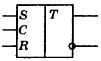

44.Триггер с разделённым входом

45 Интегральные триггеры

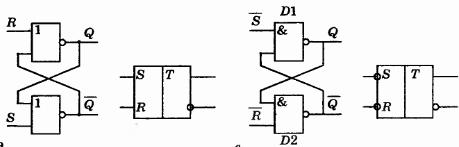

46. RS-триггер

RS-триггер[9][10], или SR-триггер — триггер, который сохраняет своё предыдущее состояние при нулевых входах и меняет своё выходное состояние при подаче на один из его входов единицы. Триггером называется устройство, имеющее два устойчивых состояния и способное под действием управляющих сигналов скачкообразно переходить из одного состояния в другое. Триггер имеет два устойчивых состояния 0 и 1 и два выхода: прямой Q и

Инверсный Q Информационный вход, входной сигнал которого устанавливает триггер

в единичное состояние, называют S–входом. Перевод триггера в нулевое состояние называют сбросом или гашением (reset), а соответствующий сигнал и вход обозначают R.

Схема простейшего триггера получается на основе двух двухвходовых логических элементов ИЛИ–НЕ или И–НЕ. Устойчивое состоя-ние обеспечивается за счет связи выхода каждого элемента с одним из входов другого. Свободные входы логических элементов служат для управления и называются информационными или логическими (R – сброс, S – установка).

Асинхронные RS-триггеры

Строится на эл-ах ИЛИ-НЕ и И-НЕ

Для созд-я RS тр. исп-ся лог. эл-т с двумя вх-ми. За счёт ПОС с вых. одного лог эл-та на вх. др. происходит быстрое переключ. схемы при смене инф. входов.

Отличие ИЛИ-НЕ и И-НЕ состоит в том, что управл. тр. на эл-ах И-НЕ осущ-ся инверсн., т.е. низкими пот-ми.

Асинхр. тр. не нашли шир. примен., а явл-ся сост. частью для созд-я др. тр.

Синхронизируемые RS-триггеры

Строятся как на эл-ах И-НЕ, так и на эл-ах ИЛИ-НЕ. Однако исп-е эл-ов И-НЕ наиб. распростр. в инж. практике.

Кроме инф. входов S и R ещё им-ся синхрос-л. При этом тр-р перех. в др. сост-е только при налич. с-ла на С-входе.

Особ-ю постр-я синхр.RS-тр. явл-ся схема управления, собр-я на эл-ах D1,D2 и упр.

происх. прямыми инф. с-ми.На эл-ах D3,D4 собран обычный асинхр. тр-р.

Состояние тр-ра будет изм-ся только при наличии с-ла на синхровходе и на одном из инф. входах.

47. MS-триггер

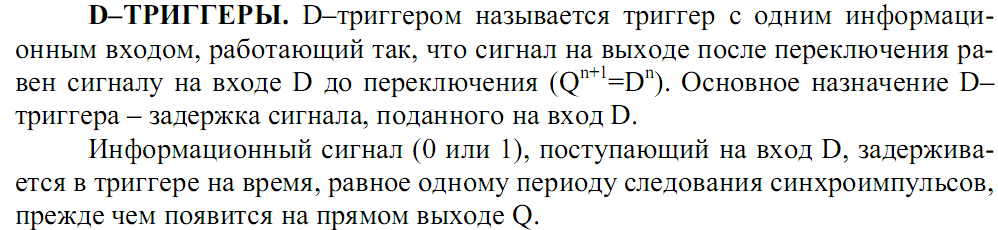

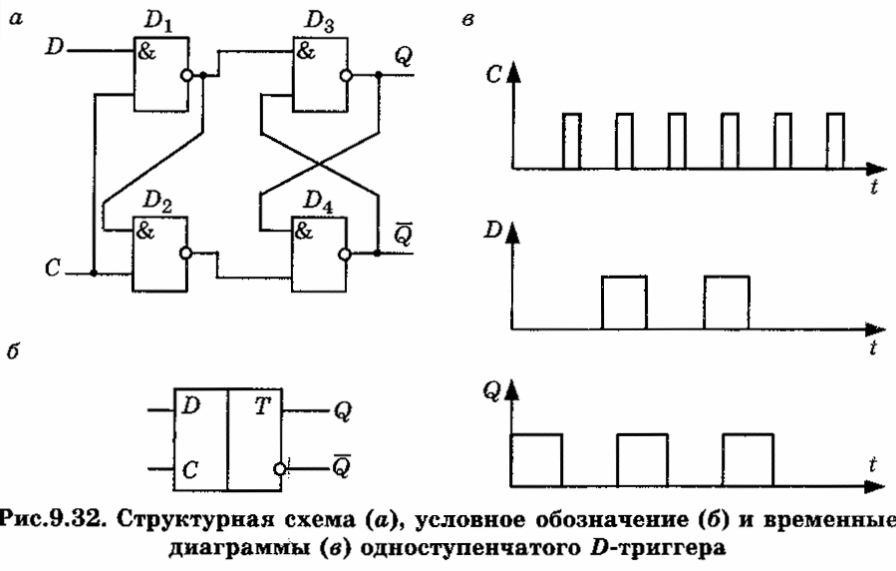

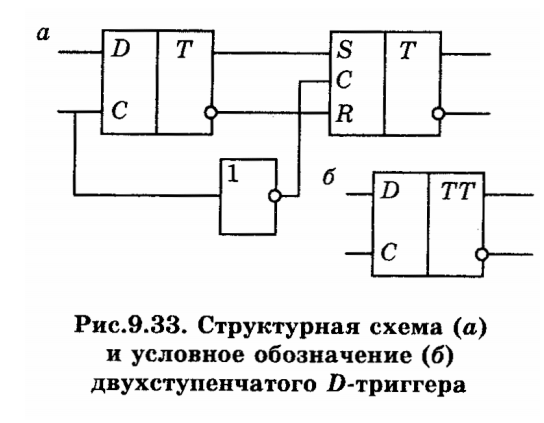

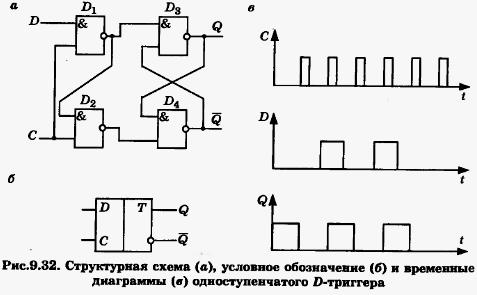

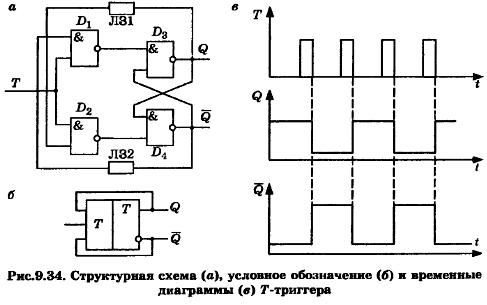

48 D-, T-триггеры

D-тр наз-ют тригером задержки и с-л на его вых. при перекл. получ. то знач, кот. было на Dвходе. Этот тр. предн. для зад-ки с-ла.

На эл-ах D1 и D2 постр. схема управления, а на D3, D4 – асинхр. RS-триг.

Триггером Т-типа наз-ют лог. устр-во с двумя уст-ми сост-ми и одним входом Т, кот. ост-ся в исх. сост-ии при Т=0 и инвертирует своё исходное сост-е при Т=1

Линии задержки предназнач. для чёткой раб .тр, потому что любые лог. эл-ты обл-ют быстр-ем и ЛЗ зад-ет с-л практич. на время сраб-я микросхемы так, что обеспеч-ся беспер-я раб Т-триг.

49 JK-триггер