- •Лабораторна робота 1 Знайомство з аналоговою комп’ютерною лабораторією схемотехніки

- •2. Порядок роботи:

- •2.1. Робота з мультиметром

- •2.2. Робота з генератором та осцилографом

- •Лабораторна робота 2 Методи та обладнання для дослідження частотних характеристик електричних кіл

- •2. Порядок роботи:

- •Лабораторна робота 3 Дослідження перехідних процесів у електричних колах постійного струму

- •2. Порядок роботи:

- •Лабораторна робота 4 Дослідження діодних випрямлячів змінного струму

- •2. Порядок роботи

- •Т аблиця 4.1

- •2. Порядок роботи

- •Т аблиця 5.1

- •Т аблиця 5.2.

- •Дослідження польового транзистора

- •Т аблиця 5.3

- •Т аблиця 5.4

- •Дослідження однокаскадних підсилювачів

- •Р ис. 5.6. Схема дослідження однокаскадного підсилювача на біполярному транзисторі т аблиця 5.5

- •Дослідження двокаскадного підсилювача

- •Лабораторна робота 6 Дослідження операційних підсилювачів і генераторів на їх основі

- •2. Порядок роботи

- •Т аблиця 6.1

- •Лабораторна робота 7 Ключовий режим роботи транзисторів. Логічні інвертори

- •Р ис. 7.1. Схема дослідження ключового режиму бінарного транзистора

- •Т аблиця 7.1 т аблиця 7.2

- •Т аблиця 7.4

- •Т аблиця 7.5

- •Т аблиця 7.6

- •Т аблиця 7.7

- •Лабораторна робота 8 Схемотехніка базових логічних елементів

- •2. Порядок роботи

- •Р ис. 8.4. Логічна схема “nand” у логіці кмоп

- •Лабораторна робота 9 Алгебра логіки та еквівалентні перетворювання логічних схем

- •2. Порядок роботи Дослідження базових логічних функцій і елементів

- •Дослідження похідних логічних функцій

- •Дослідження логічних схем

- •Лабораторна робота 10 Тригери та їх застосування у схемах бінарних лічильників

- •2. Порядок роботи: Дослідження схем тригерів

- •Дослідження бінарних лічильних схем

- •2. Порядок роботи

- •Дослідження елементів запам’ятовуючих пристроїв

- •Т аблиця 12.1

- •Дослідження дешифраторів

- •Дослідження транскодера

- •Т аблиця 12.2. Дослідження демультиплексора

- •Дослідження мультиплексора

Дослідження дешифраторів

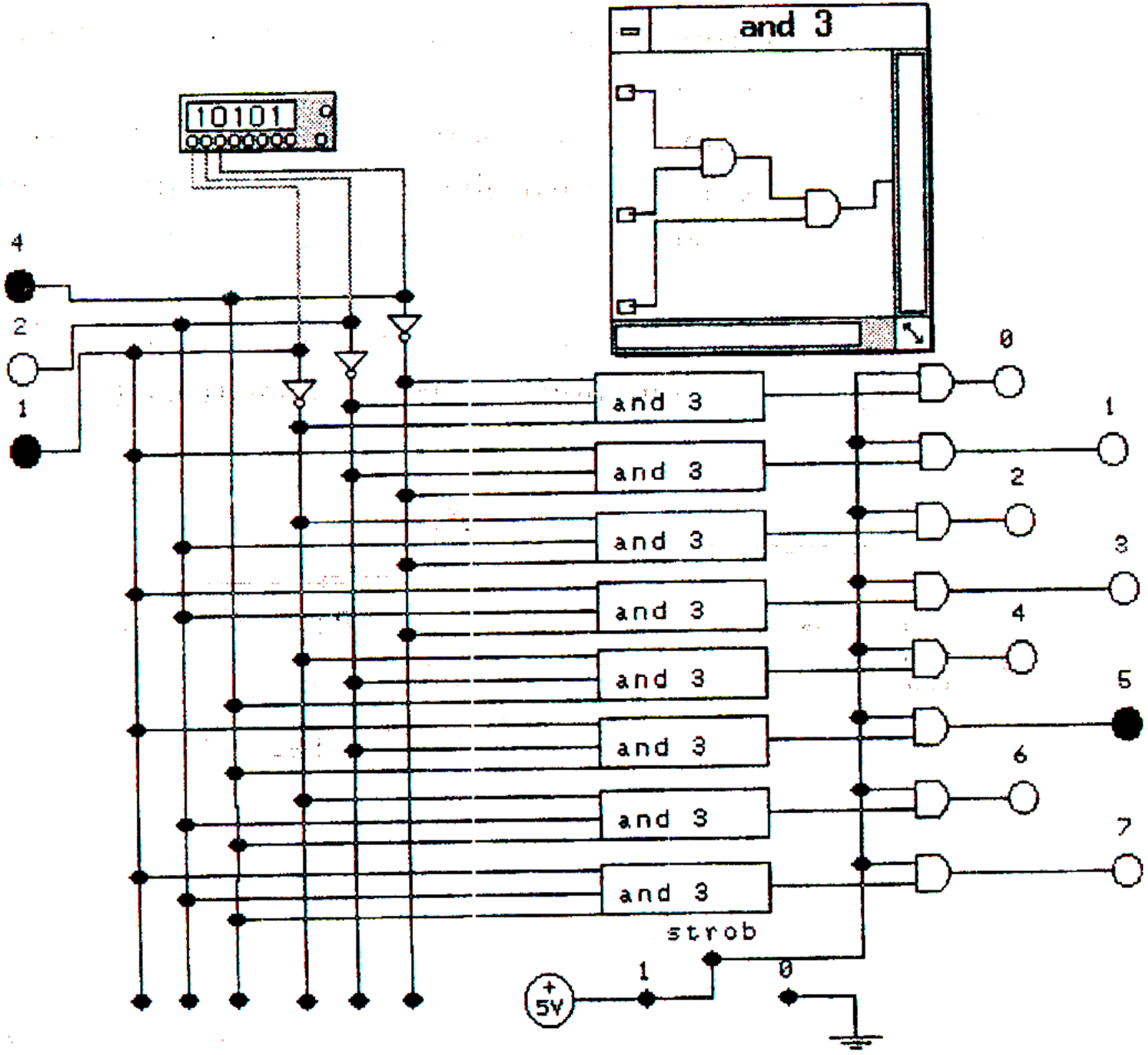

2.5. Зібрати схему повного дешифратора 3-розрядного двійкового коду з поступово зростаючим номером виходу, що має логічну “1”, в якому при збільшенні на одиницю двійкового вхідного коду поступово збільшується номер виходу (Рис. 12.3.).

Рис. 12.3. Схема повного дешифратора на 8 виходів

2.6. Скласти логічне рівняння та таблиці істинності для кожного виходу. Перевірити алгоритм роботи дешифратора. Застосовуючи перемикач “Strob”, з’ясувати роботу стробувального входу дешифратора.

2.7. Скласти схему дешифратора дворозрядного коду зі стробуванням. На його основі зробити схему повного дешифратора на 16 виходів. Застосовуючи генератор слів, перевірити режим його функціонування.

2.8.

Активізувати файл “Dech_16.cd3”,

що моделює пірамідальний дешифратор

на 16 виходів (Рис.

12.4.).

Змінюючи за допомогою генератора слів

поступово двійковий вхідний код,

простежити роботу цього дешифратора.

Пояснити роботу кожного із застосованих

стробів.

2.8.

Активізувати файл “Dech_16.cd3”,

що моделює пірамідальний дешифратор

на 16 виходів (Рис.

12.4.).

Змінюючи за допомогою генератора слів

поступово двійковий вхідний код,

простежити роботу цього дешифратора.

Пояснити роботу кожного із застосованих

стробів.

Рис. 12.4. Схема пірамідального дешифратора на 16 виходів

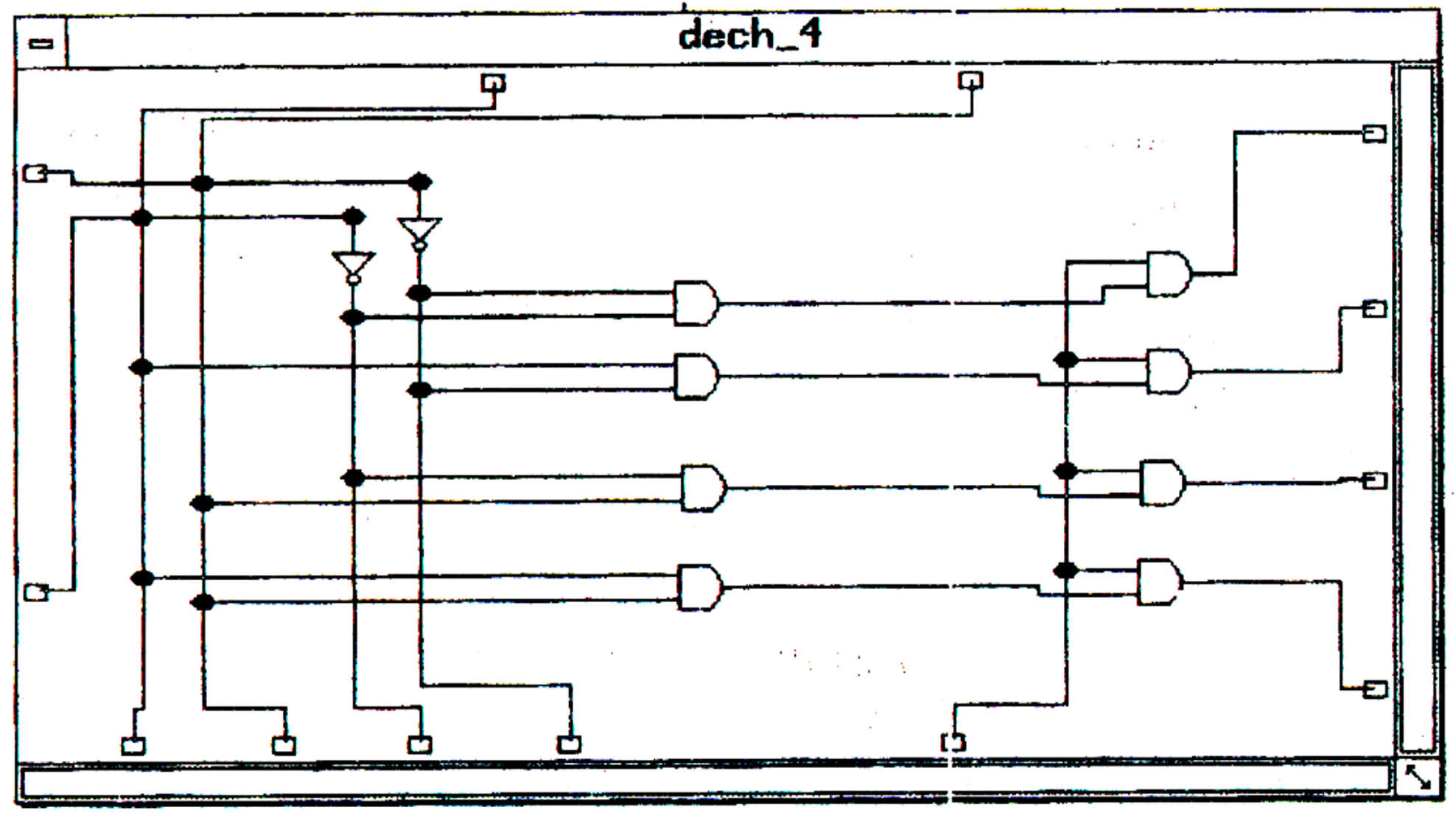

Зазначимо, що на (Рис. 12.4.) всі схеми дешифраторів на чотири виходи (Dech_4) ідентичні (Рис. 12.5.).

Рис. 12.5. Дешифратор на чотири виходи зі стробуванням

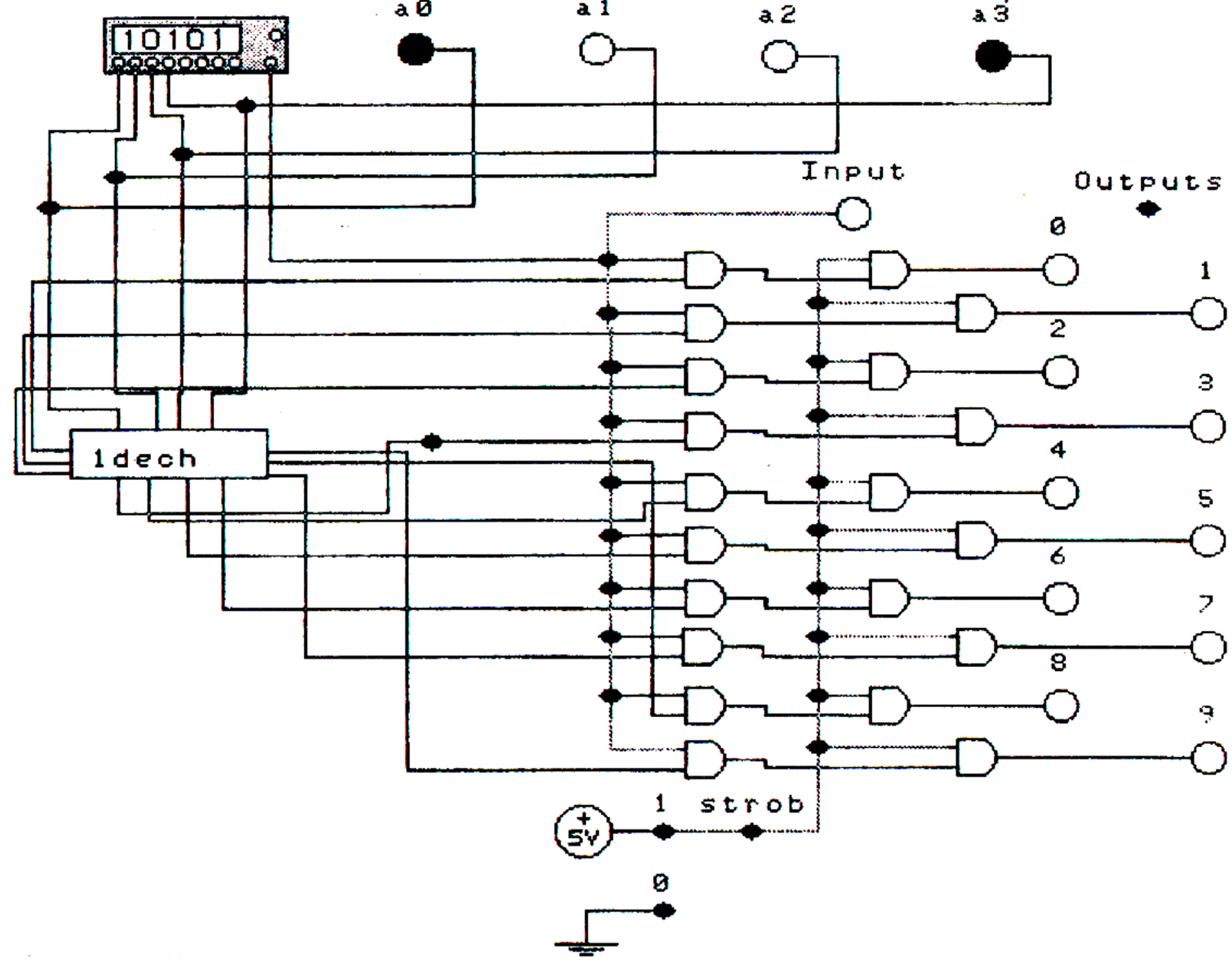

2.9. Активізувати файл “Dech_10.cd3”, що моделює дешифратор однієї декади двійково-десяткового коду в унітарний код (Рис. 12.6.). Змінюючи двійкові комбінації вхідного коду, простежити процес його перетворення в унітарний 10-розрядний код. Відкрити і накреслити схеми кожної зі ступенів дешифратора: “Dech_5” і “Dech_10”. Пояснити принцип функціонування двійково-десяткового дешифратора.

Рис. 12.6. Схема однієї декади двійково-десяткового дешифратора

Дослідження транскодера

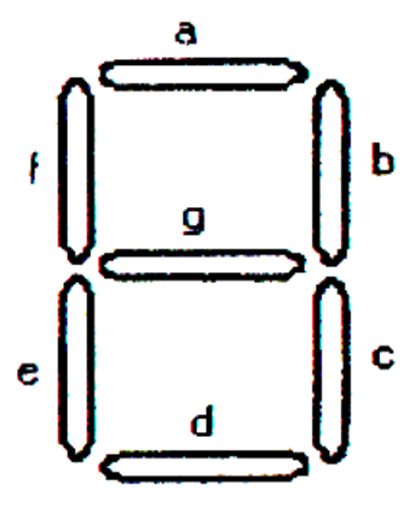

2.10. Як

приклад транскодера розглянемо схему

управління 7-сегментним десятковим

індикатором стану однієї декади

двійково-десяткового коду. Умовне

позначення цього індикатора показано

на (Рис.

12.7.). Вхідним

кодом такого індикатора є двійковий

4-розрядний код 1.2.4.8, вихідний забезпечує

десяткову індикацію числового еквівалента

вхідного коду від 0 до 9. Відповідність

кодів подано в Табл.

12.2.

2.10. Як

приклад транскодера розглянемо схему

управління 7-сегментним десятковим

індикатором стану однієї декади

двійково-десяткового коду. Умовне

позначення цього індикатора показано

на (Рис.

12.7.). Вхідним

кодом такого індикатора є двійковий

4-розрядний код 1.2.4.8, вихідний забезпечує

десяткову індикацію числового еквівалента

вхідного коду від 0 до 9. Відповідність

кодів подано в Табл.

12.2.

Рис. 12.7. Вид 7-сегмент-

ного індикатора

У цій таблиці показано необхідний стан елементів 7-сегментного індикатора (a,b,c,d,e,f,g) при кожній комбінації вхідного двійкового коду. Наприклад, якщо вхідним кодом є “0,0,0,0”, то мають засвітитися сегменти a,b,c,d,e,f, якщо “0,0,1,1”, то сегменти a,b,g,c,d і т.д.

2.11. Скласти логічне рівняння для станів кожного сегмента, за допомогою логічного синтезатора синтезувати схеми управління кожним сегментом і перевірити її функціонування (кожну синтезовану схему в мікросхему).

Т аблиця 12.2. Дослідження демультиплексора

2.12.

Активізувати файл “Dempx.cd3”,

що моделює демультиплексор на 10 виходів

(Рис. 12.8.).

Ретельно дослідити запропоновану схему

і визначити призначення демультиплексора

і кожної його логічної схеми. Відкрити

панель

2.12.

Активізувати файл “Dempx.cd3”,

що моделює демультиплексор на 10 виходів

(Рис. 12.8.).

Ретельно дослідити запропоновану схему

і визначити призначення демультиплексора

і кожної його логічної схеми. Відкрити

панель

Рис. 12.8. Схема демультиплексора на 10 виходів

генератора слів і визначити комбінації адресів, що мають вибрати той або інший канал для його підключення до виходу.

2.13. Перевірити функціонування демультиплексора шляхом послідовного режиму моделювання, визначаючи на кожному кроці відповідність адреси каналу та фактичному з’єднанні вхідного і вихідного каналів. Пояснити призначення команди “Strob” шляхом подачі на відповідний вхід “1” або “0”.

2.14. Запрограмувати будь-який інший порядок підключення каналів і перевірити послідовність їх підключення.