- •Содержание.

- •Перечень элементов………………………………………………………13 Приложение а ……………………………………………………………….14 Введение.

- •Структурная схема блока озу.

- •Описание работы схемы.

- •Проектирование модуля озу.

- •Микросхема к537ру14

- •Страничная организация Модуля озу.

- •Описание интерфейса

- •Устройства сопряжения с шинами.

- •Выбор буферных регистров.

- •Выбор шинного формирователя.

- •Выбор дешифратора.

Страничная организация Модуля озу.

Способ проектирования ОЗУ иллюстрируется на принципиальной схеме проекта, на котором приведён блок ОЗУ, ёмкостью в 32К байт. Каждая микросхема К537РУ14 имеет одноразрядную организацию 4К бит на 1 (4К*1). Для наращивания разрядности слов до 16К байт объединяют по шестнадцать микросхем в субмодуль (или страницу) путём соединения всех одноимённых выводов, кроме информационных. Для получения информационной ёмкости модуля ОЗУ в 32К байта нужно ещё 4 субмодуля..

Для наращивания информационной ёмкости до 32К байт соединяют все одноимённые выводы субмодулей , кроме выводов для сигналов выбора микросхем CS1,CS2,…,CS4. Эти выводы подключают к выходам дешифратора DD3.

Описание интерфейса

Интерфейс МПИ (QBUS) предназначен для организации систем управления промышленным оборудованием на основе микроЭВМ типа Элекгроника-60" и совместимых с ней, т.е выполненных на микропроцессорах К1801ВМ1. К1801ВМ2 Перечень сигналов интерфейса МПИ. имеющих отношения к операциям с памятью, приведен в таблице.2

Таблица2

|

Обозначение сигнала

|

Назначение сигнала

|

Уровень активности

|

|

AD(0-15) |

Параллельная 1 6-разрядная шина адреса данных |

низкий низкий

|

|

WTBT |

Признак записи/вывода байта |

низкий |

|

SYNC

|

Сигнал синхронизации активного устройства

|

низкий

|

|

RPLY

|

Сигнал синхронизации пассивного устройства

|

низкий

|

|

DIN

|

Ввод данных

|

низкий

|

|

DOUT

|

Вывод данных

|

низкий {

|

|

BS | Выбор внешнего устройства

|

Выбор внешнего устройства |

низкий

|

Логической единице соответствует низкий уровень сигнала, логическому нулю - высокий уровень

Особенностью интерфейса

является мультиплексирование

информационной

шины, по которой в различные моменты

времени

пересылаются

адреса и данные. При использовании

16-разрядной шины

возможна адресация

64 Кбайт, минимальной адресуемой единицей

является

байт

Совокупность двух байтов, начинающаяся

с четного адреса, представляет

слово. При выполнении

операций ввода информации а  активный

модуль

(процессор) всегда

адресуются слова, а при выводе - как

слова, так и байты.

активный

модуль

(процессор) всегда

адресуются слова, а при выводе - как

слова, так и байты.

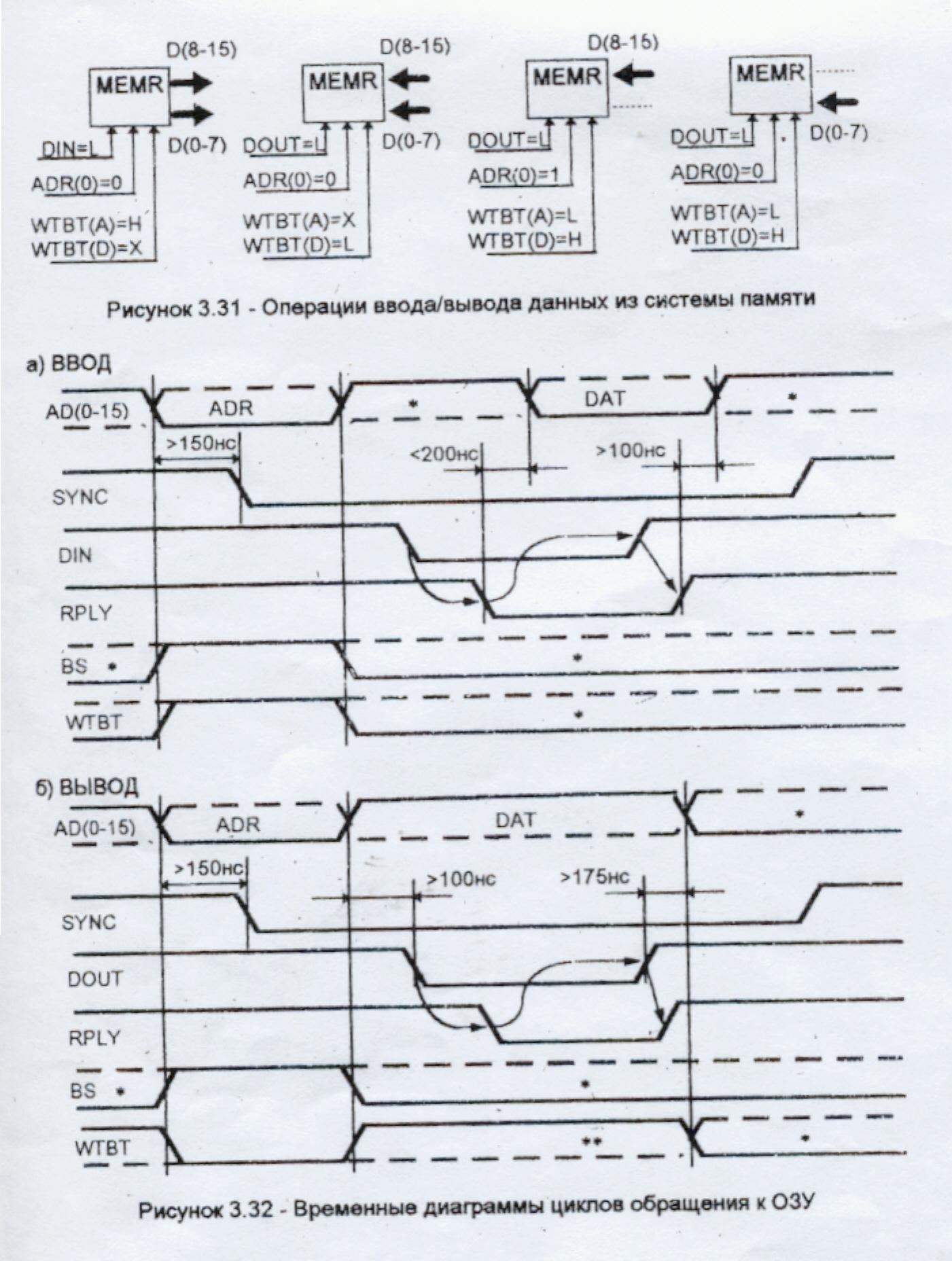

Все возможные олерации ввода/вывода информации из системы памяти MEMR иллюстрируются рисунком Предстоящую операцию определяют сигналы: DIN, DOUT, ADR(O), WTBT. Значение младшего разряда адреса ADR(0)= AD(0) во время адресной посылки определяет выбор старшего (1) или младшего (0) байта. При выполнении операции ввода/вывода слов ADR(0)=0 Значение сигнала WTBT во время адресной посылки WTBT(A)=H извещает систему о предстоящей операции ввода, a WTBT(A)=L - вывода информации Значение сигнала WTBT во время информационной посылки при выводе WTBT(D) определяет выбор слоd (Н) или байта (L).

Связь между активным устройством (процессором) и пассивным (выполняющим операцию) асинхронная, те. на управляющий сигнал должен поступить ответный сигнал, извещающий о выполнении операции

Временные диаграммы циклов ВВОД (чтение ОЗУ) и ВЫВОД (запись в ОЗУ) приведены на рисунке а,б При обращении к ОЗУ сигнал BS имеет высокий уровень При выводе данных из активного устройства (процессора) сигнал WTBT выдается низким потенциалом, если происходит запись байта. Адрес байта в пределах слова задается сигналом AD(0) во время адресного цикла посылки.

Рис 4 Временные диаграммы циклов

обращения к ОЗУ

Микросхема KP1801BM1 предстлвляет собой однокристальный микропроцессор для обработки 16-разрядных данных. Система команд соответствует системе команд микроЭВМ «Электроника-60». Структурная схема микропроцессора представлена на рис. Рассмотрим состав и назначение основных блоков. Операционный блок (ОБ) содержит АЛУ, блок РОН, регистр состояния процессора, регистры адреса и данных. Операционный блок осуществляет: вычисление адреса и его временное храпение; прием данных, их хранение в регистрах и выдачу в канал; выполнение арнфнетическо-логнческнх операций; формирование состоянии процессора и адресов векторов прерывания.

Арифметичсско-логнческое устройство выполняет все арифметические и логические операции и операции сдвиги над 16-разрядпыми операндами. Кроме того, оно офрмирует ряд признаков, необходимых для формирования состояний процессора.

Блок РОН состоит из восьми 16-разрядных регистров, которые могут использоваться в качестве: накопителей, когда обрабатываемые данные хранятся в регистрах; указателен адреса, когда регистр содержит адрес операнда; указателей индекса, когда содержимое регистра прибавляется к индексному слову для вычисления адреса операнда; указателей адреса при автоинкрементной и автодекрементной адресации, когда адрес автоматически изменяется с заданным шагом, что позволяет обращаться к последовательно расположенным ячейкам памяти. При автоинкрементной адресации происходит автоматическое увеличение, а при автодекрементной — автоматическое уменьшение содержимого указателя адреса.