- •Схемотехника эвм

- •Содержание

- •Предисловие

- •Введение

- •1. Основные определения и характеристики схем цифровых устройств

- •1.1. Основные определения в области микросхемотехники

- •1.2. Основные обозначения на схемах

- •1.3. Основные положения модели поведения полупроводниковых приборов

- •1.3.1. Полупроводниковый p-n-переход.

- •1.3.2. Полупроводниковый диод

- •1.3.3. Биполярный транзистор

- •1.3.4. Полевой транзистор

- •2. Основные понятия алгебры логики

- •Введение в алгебру логики

- •Булевый базис

- •2.3. Произвольные функции и логические схемы

- •Законы булевой алгебры

- •2.5. Положительная и отрицательная логика

- •3. Цифровые интегральные микросхемы

- •3.1. Параметры микросхем

- •3.2. Особенности логических элементов различных логик

- •3.2.1. Диодно-транзисторная логика

- •3.2.2. Высокопороговая логика

- •3.2.3. Транзисторно-транзисторная логика

- •Универсальные (стандартные) серии ттл

- •Микромощные микросхемы ттл

- •Микросхемы ттл повышенного быстродействия

- •Микросхемы ттл с транзисторами Шотки

- •Способ увеличения числа входов и, или

- •Исключающее или

- •Соединение входов и выходов микросхем ттл

- •Неиспользуемые логические элементы ттл

- •Неиспользуемые входы ттл

- •Совместное применение разных серий ттл

- •3.2.4. Типы выходных каскадов Микросхемы с открытым коллектором

- •3.2.5. Микросхемы с тремя логическими состояниями

- •4. Логические элементы на кмоп-транзисторах

- •4.1. Логические элементы на моп-транзисторах

- •4.2. Цифровые микросхемы кмоп

- •4.3. Микросхемы с буферными выходами

- •Основные логические элементы кмоп

- •5. Схемотехника интегральных схем инжекционной логики и эсл

- •5.1. Схемы с непосредственными связями

- •5.2. Схемотехника ис инжекционной логики и2л

- •5.3. Эмиттерно-связанная логика

- •6. Триггеры

- •6.1. Общие сведения о триггерных устройствах

- •6.2. Асинхронный rs-триггер

- •6.3. Триггерные системы

- •6.3.1. Синхронный rs-триггер

- •6.4. Тактируемый d-триггер

- •6.5. Счетный т-триггер

- •6.6. Двухступенчатые триггеры

- •7. Счетчики

- •7.1. Общие положения

- •7.2. Классификация счетчиков

- •7.2.1. Асинхронные суммирующие счетчики с последовательным переносом

- •7.2.2. Асинхронные вычитающие счетчики с последовательным переносом

- •7.2.3. Асинхронные реверсивные счетчики с последовательным переносом

- •7.3. Параллельное соединение счетчиков

- •7.4. Последовательное соединение счетчиков

- •7.5.Синхронные двоичные счетчики со сквозным переносом.

- •7.6.Синхронные двоичные счетчики с параллельным переносом.

- •8. Регистры

- •8.1. Назначение и классификация регистров

- •8.2. Регистры памяти

- •8.3. Буферы данных

- •8.4. Регистры сдвига

- •Кольцевые счетчики

- •9. Мультиплексоры и демультиплексоры

- •9.1. Общие сведения

- •9.2. Мультиплексоры

- •9.3. Демультиплексоры

- •10. Шифраторы и дешифраторы

- •10.1. Шифраторы

- •10.2. Дешифраторы

- •11. Арифметические устройства

- •11.1. Сумматоры

- •Четвертьсумматор

- •Полусумматор

- •Полный одноразрядный двоичный сумматор

- •Сумматоры с последовательным переносом

- •11.2. Инкрементор

- •11.3. Вычитатели (субтракторы)

- •11.4. Компараторы

- •Основные характеристики компараторов

- •Компараторы аналоговых сигналов

- •Компараторы цифровых сигналов

- •Компаратор на базе сумматора

- •11.5. Арифметико-логические устройства

- •12. Импульсные устройства на имс

- •12.1. Формирователи импульсов

- •12.2. Схемы нормализации импульсов

- •12.3. Схемы укорачивания импульсов

- •12.4. Схемы задержки импульса

- •12.5. Одновибраторы

- •12.6. Генераторы тактовой частоты

- •13. Запоминающие устройства

- •13.1. Общие характеристики устройств

- •13.2. Запоминающие элементы постоянных зу

- •13.3. Оперативные запоминающие устройства

- •13.3.1. Динамические зу

- •13.3.2. Статические зу

- •14. Аналого-цифровые и цифро-аналоговые преобразователи

- •14.1. Общие сведения

- •14.2. Цифро-аналоговые преобразователи

- •14.3. Аналого-цифровые преобразователи

- •14.3.1. Характеристики и параметры ацп

- •14.3.2. Ацп последовательного счета

- •14.3.3. Параллельный ацп

- •14.3.4. Сигма-дельта ацп

- •Заключение

- •Библиографический список

- •Приложение 1 Перечень стандартов

- •Основные стандарты ескд

- •Система технологической документации

- •Стандарты системы информационно-библиографической документации

- •Система стандартов по безопасности труда

- •Разработка и постановка продукции на производство

- •Система стандартов программной документации

- •Основополагающие стандарты гсп

- •Приложение 2

- •Цифровых устройств

Способ увеличения числа входов и, или

В процессе разработки цифровых схем может оказаться недостаточным число входов элемента И. Увеличить число входов микросхемы (выполнить расширение по И) можно применением нескольких схем И. Например, на двухвходовую схему И можно подать выходы с двух 4- или 8-входовых схем И (рис. 3.20, а). Получится 8- или 16-входовая схема И.

И![]() спользуя

разбиение исходной функции на группы

с помощью формулы де Моргана, можно

получить различные варианты реализации

требуемой функции из имеющихся элементов.

Например, шестнадцативходовый элемент

И можно реализовать с помощью двух

восьмивходовых элементов И–НЕ

и одного двухвходового элемента ИЛИ–НЕ

(рис. 3.20, б):

спользуя

разбиение исходной функции на группы

с помощью формулы де Моргана, можно

получить различные варианты реализации

требуемой функции из имеющихся элементов.

Например, шестнадцативходовый элемент

И можно реализовать с помощью двух

восьмивходовых элементов И–НЕ

и одного двухвходового элемента ИЛИ–НЕ

(рис. 3.20, б):

Тот же результат может быть получен подключением дополнительных внешних диодов и резистора к любому из входов микросхемы И–НЕ (рис. 3.20, в). Сопротивление резистора определяется в соответствии с требуемым быстродействием. С увеличением Rд задержка будет возрастать. Обычно принимают Rд = 1–2 кОм.

Рис. 3.20. Увеличение числа входов: а – с помощью нескольких микросхем И;

б – микросхем И–НЕ и ИЛИ–НЕ; в– подключением внешнего диода и резистора

Логические элементы И–НЕ наиболее характерны для семейства ТТЛ и ТТЛШ. Они производятся в виде самостоятельных микросхем, а также служат для построения других устройств. Промышленностью выпускаются микросхемы с различным числом входов, различной нагрузочной способностью и различным числом выполняемых функций. Кроме базового элемента (155ЛА1 – 2х4И–НЕ) выпускаются также 4x2И–НЕ (ЛА3), 3x3И–НЕ (ЛА4), 8И–НЕ (ЛА2), 2x4И–НЕ (ЛА6), 4x2И–НЕ (ЛА12) и др.

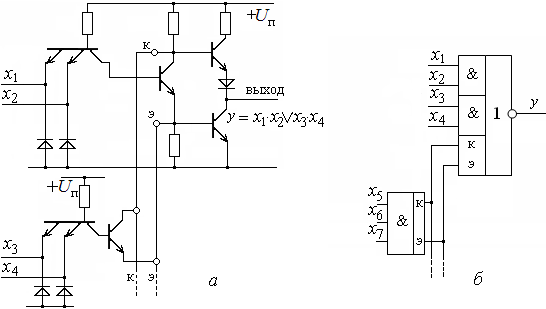

Схема логического элемента И–ИЛИ–НЕ (а также ИЛИ–НЕ) получается

путем подключения параллельно транзистору-расщепителю фазы дополнительных транзисторов со своими входными каскадами. На рис. 3.21, а показана принципиальная схема логического элемента 2x2И–2ИЛИ–НЕ (половина микросхемы 155ЛР1). Если входы x1 и x2, а также x3 и x4 перемкнуть, элемент будет выполнять функцию ИЛИ–НЕ.

В составе серий 155 ТТЛ и 555 ТТЛШ есть и другие, более сложные микросхемы. Они обладают большой функциональной гибкостью.

На рис. 3.22 представлена микросхема 155ЛР3. Здесь выходной сигнал:

В зависимости от сигнала на входе V схема работает как элемент 3И–НЕ либо 3ИЛИ–НЕ.

![]()

При

V =

0,

![]() ,

,

При

V =

1

![]()

Рис. 3.21. Элемент И–ИЛИ–НЕ с возможностью расширения по ИЛИ:

а – принципиальная схема;

б – условное графическое обозначение схемы с расширением по ИЛИ

Рис. 3.22. Микросхема 155ЛР3

Увеличение числа секций И–ИЛИ может осуществляться путем применения специальных микросхем – расширителей по ИЛИ (экспандеров).

Схема расширителя (155ЛД1) представлена на рис. 3.23.

Рис. 3.23. Схема расширителя 155ЛД1

Выводы к и э транзистора VT2 расширителя подключают к точкам к и э логического элемента ИЛИ (к расщепителю фазы) (см. рис. 3.21).

Микросхема 155ЛД1 содержит два четырехвходовых расширителя. Каждый такой расширитель увеличивает задержку распространения сигнала на 3–5 нс, что следует учитывать при разработке цифровых схем. Микросхема расширителя 155ЛД3 имеет восемь входов по И.