- •Схемотехника эвм

- •Содержание

- •Предисловие

- •Введение

- •1. Основные определения и характеристики схем цифровых устройств

- •1.1. Основные определения в области микросхемотехники

- •1.2. Основные обозначения на схемах

- •1.3. Основные положения модели поведения полупроводниковых приборов

- •1.3.1. Полупроводниковый p-n-переход.

- •1.3.2. Полупроводниковый диод

- •1.3.3. Биполярный транзистор

- •1.3.4. Полевой транзистор

- •2. Основные понятия алгебры логики

- •Введение в алгебру логики

- •Булевый базис

- •2.3. Произвольные функции и логические схемы

- •Законы булевой алгебры

- •2.5. Положительная и отрицательная логика

- •3. Цифровые интегральные микросхемы

- •3.1. Параметры микросхем

- •3.2. Особенности логических элементов различных логик

- •3.2.1. Диодно-транзисторная логика

- •3.2.2. Высокопороговая логика

- •3.2.3. Транзисторно-транзисторная логика

- •Универсальные (стандартные) серии ттл

- •Микромощные микросхемы ттл

- •Микросхемы ттл повышенного быстродействия

- •Микросхемы ттл с транзисторами Шотки

- •Способ увеличения числа входов и, или

- •Исключающее или

- •Соединение входов и выходов микросхем ттл

- •Неиспользуемые логические элементы ттл

- •Неиспользуемые входы ттл

- •Совместное применение разных серий ттл

- •3.2.4. Типы выходных каскадов Микросхемы с открытым коллектором

- •3.2.5. Микросхемы с тремя логическими состояниями

- •4. Логические элементы на кмоп-транзисторах

- •4.1. Логические элементы на моп-транзисторах

- •4.2. Цифровые микросхемы кмоп

- •4.3. Микросхемы с буферными выходами

- •Основные логические элементы кмоп

- •5. Схемотехника интегральных схем инжекционной логики и эсл

- •5.1. Схемы с непосредственными связями

- •5.2. Схемотехника ис инжекционной логики и2л

- •5.3. Эмиттерно-связанная логика

- •6. Триггеры

- •6.1. Общие сведения о триггерных устройствах

- •6.2. Асинхронный rs-триггер

- •6.3. Триггерные системы

- •6.3.1. Синхронный rs-триггер

- •6.4. Тактируемый d-триггер

- •6.5. Счетный т-триггер

- •6.6. Двухступенчатые триггеры

- •7. Счетчики

- •7.1. Общие положения

- •7.2. Классификация счетчиков

- •7.2.1. Асинхронные суммирующие счетчики с последовательным переносом

- •7.2.2. Асинхронные вычитающие счетчики с последовательным переносом

- •7.2.3. Асинхронные реверсивные счетчики с последовательным переносом

- •7.3. Параллельное соединение счетчиков

- •7.4. Последовательное соединение счетчиков

- •7.5.Синхронные двоичные счетчики со сквозным переносом.

- •7.6.Синхронные двоичные счетчики с параллельным переносом.

- •8. Регистры

- •8.1. Назначение и классификация регистров

- •8.2. Регистры памяти

- •8.3. Буферы данных

- •8.4. Регистры сдвига

- •Кольцевые счетчики

- •9. Мультиплексоры и демультиплексоры

- •9.1. Общие сведения

- •9.2. Мультиплексоры

- •9.3. Демультиплексоры

- •10. Шифраторы и дешифраторы

- •10.1. Шифраторы

- •10.2. Дешифраторы

- •11. Арифметические устройства

- •11.1. Сумматоры

- •Четвертьсумматор

- •Полусумматор

- •Полный одноразрядный двоичный сумматор

- •Сумматоры с последовательным переносом

- •11.2. Инкрементор

- •11.3. Вычитатели (субтракторы)

- •11.4. Компараторы

- •Основные характеристики компараторов

- •Компараторы аналоговых сигналов

- •Компараторы цифровых сигналов

- •Компаратор на базе сумматора

- •11.5. Арифметико-логические устройства

- •12. Импульсные устройства на имс

- •12.1. Формирователи импульсов

- •12.2. Схемы нормализации импульсов

- •12.3. Схемы укорачивания импульсов

- •12.4. Схемы задержки импульса

- •12.5. Одновибраторы

- •12.6. Генераторы тактовой частоты

- •13. Запоминающие устройства

- •13.1. Общие характеристики устройств

- •13.2. Запоминающие элементы постоянных зу

- •13.3. Оперативные запоминающие устройства

- •13.3.1. Динамические зу

- •13.3.2. Статические зу

- •14. Аналого-цифровые и цифро-аналоговые преобразователи

- •14.1. Общие сведения

- •14.2. Цифро-аналоговые преобразователи

- •14.3. Аналого-цифровые преобразователи

- •14.3.1. Характеристики и параметры ацп

- •14.3.2. Ацп последовательного счета

- •14.3.3. Параллельный ацп

- •14.3.4. Сигма-дельта ацп

- •Заключение

- •Библиографический список

- •Приложение 1 Перечень стандартов

- •Основные стандарты ескд

- •Система технологической документации

- •Стандарты системы информационно-библиографической документации

- •Система стандартов по безопасности труда

- •Разработка и постановка продукции на производство

- •Система стандартов программной документации

- •Основополагающие стандарты гсп

- •Приложение 2

- •Цифровых устройств

14.3.2. Ацп последовательного счета

Самый простой АЦП – это компаратор, работа которого рассмотрена в главе 11 (рис. 11.10). Это одноразрядный АЦП, который имеет только одну ступень квантования. Подобные АЦП находили применение в гибридных ЭВМ.

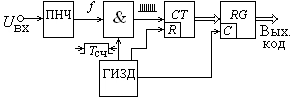

Более сложный АЦП имеет несколько ступеней квантования. Далее будут рассмотрены несколько вариантов построения АЦП. Структурная схема АЦП последовательного счета с предварительным преобразованием напряжения в частоту представлена на рис. 14.6.

Рис. 14.6. Структурная схема интегрирующего АЦП последовательного счета

Двоичный счетчик подсчитывает число импульсов, поступивших от преобразователя напряжения в частоту (ПНЧ) за период Тсч, фиксируемый генератором импульсов заданной длительности (ГИЗД). По окончании счета код счетчика заносится в регистр, а перед началом нового счета счетчик сбрасывается в нулевое состояние по входу R.

Преобразователи напряжения в частоту могут быть выполнены с применением различных элементов и схем. Одна из схем приведена на рис. 14.7.

Входной сигнал Uвх интегрируется и подается на устройство сравнения, на другой вход которого поступает напряжение U0 от источника опорного напряжения ИОН. В момент равенства выходного напряжения интегратора Uи и напряжения U0 устройство сравнения включает формирователь импульсов обратной связи СФ (например, одновибратор), формирующий в течение интервала времени tос импульс амплитудой Uос, постоянной вольт-секундной площади Uос tос (рис. 14.7, б). Цикл работы формирователя определяется интервалом времени Тх = tинт + tос, зависящим от значения напряжения Uвх.

а б

Рис. 14.7. Структурная схема (а) и временная диаграмма (б) преобразователя

напряжения в частоту

При прямоугольной форме импульсов амплитудой Uос:

Uвх tинт / 1 = U0 = Uос tос/ 2 – Uвх tос / 1;

Uвх (tинт+ tос) / 1 = Uвх Тх /1 = Uос tос/ 2,

где R1C = 1; R2C = 2; Тх = tинт + tос = 1 / fвых.

Следовательно, уравнение преобразования можно записать в виде

fвых = 1 / Тх = Uвх 2/1 Uос tос = Uвх R2 / R1 Uос tос = k Uвх ,

т. е. параметры преобразователя не зависят от значений емкости С и образцового напряжения U0 и определяются только отношением сопротивлений интегратора и стабильностью площади импульса обратной связи.

На значение общей погрешности преобразователя существенное значение может оказать дрейф нуля интегратора, поэтому в схемах преобразователей малых напряжений в частоту используют различные способы компенсации дрейфа нуля интегратора.

Рассмотренный способ преобразования аналогового сигнала в код используется в микросхеме типа КР1108ПП1, которая преобразует положительные и отрицательные уровни входного напряжения ±10 В в импульсы прямоугольной формы с калиброванной длительностью, а также служит для преобразования частоты в напряжение (ПНЧ – ПЧН). В [3] приведена схема включения микросхемы в режиме ПНЧ для преобразования положительного напряжения 0…10 В в частоту от 0 Гц до 10 кГц. При этом крутизна преобразования равна 1 кГц/В (т. е. каждый выходной импульс соответствует приращению входного напряжения на 1 мВ).

Более высокую точность имеет АЦП двойного интегрирования, схема которого приведена на рис. 14.8.

а б

Рис. 14.8. АЦП с двойным интегрированием: а – структура;

б – временная диаграмма

В двухтактном АЦП преобразование аналогового сигнала в код проходит две стадии: стадию интегрирования и стадию счета. В начале первой стадии ключ Кн1 замкнут, а ключ Кн2 разомкнут. В момент начала преобразования установленный управляющим устройством УУ на нуль по входу R счетчик запускается. С этого момента до момента tо формируется временной интервал – время первичного интегрирования. В течение интервала ключ Кн1 замкнут, а входное напряжение предполагается постоянным. Интегратор интегрирует входное напряжение. На выходе интегратора напряжение к моменту окончания интегрирования составляет

И![]() з

этого выражения видно, что величина

выходного напряжения интегратораUи

прямо зависит от постоянного уровня

входного сигнала (на рис. 14.8 показаны

уровни Uвх1

и Uвх2).

з

этого выражения видно, что величина

выходного напряжения интегратораUи

прямо зависит от постоянного уровня

входного сигнала (на рис. 14.8 показаны

уровни Uвх1

и Uвх2).

После окончания первой стадии интегрирования счетчик формирует сигнал окончания первого интервала Uк, ключ Кн1 размыкается, а ключ Кн2 замыкается и на вход интегратора поступает опорное напряжение от источника опорного напряжения ИОН. При этом опорное напряжение выбирается противоположным по знаку входному напряжению. На второй стадии, стадии счета, выходное напряжение интегратора линейно уменьшается по абсолютной величине, как показано на рис. 14.8. Счетчик подсчитывает число импульсов, пропорциональное длительности второго интервала интегрирования.

Стадия счета заканчивается, когда выходное напряжение интегратора переходит через нуль. В момент такого пересечения срабатывает компаратор К, напряжение на выходе компаратора Uк становится равным нулю и по входу V счетчика прекращает подсчет импульсов.

Отличительной особенностью метода двухтактного интегрирования является снижение влияния помех на результат преобразования вследствие того, что содержимое счетчика после окончания счета определяется усредненным значением входного напряжения за время . Поэтому переменные составляющие входного напряжения в значительной степени ослабляются. Благодаря высокой точности преобразования двухтактные АЦП находят преимущественное применение в измерительной технике. В качестве примера преобразователей рассмотренного типа можно указать ИМС 11-разрядного АЦП К572ПВ2.

К преобразователям последовательного счета относятся АЦП с единичным приближением (со ступенчатым пилообразным напряжением), основанные на уравновешивании входного аналогового сигнала суммой минимальных (для данного преобразователя) по весу квантов. Другое название такого преобразователя – АЦП с постоянными ступеньками. Схема такого преобразователя и временная диаграмма процесса преобразования приведены на рис. 14.9. Схема состоит из компаратора, счетчика и цифроаналогового преобразователя (ЦАП).

а б

Рис. 14.9. АЦП последовательного счета с единичным приближением:

а – структурная схема; б – временная диаграмма процесса преобразования

На один вход компаратора поступает преобразуемый сигнал Uвх, а на другой – сигнал обратной связи Uос с ЦАП. В исходном состоянии выход компаратора равен логической единице. С приходом импульса «Пуск» управляющее устройство УУ устанавливает счетчик в нулевое состояние и разрешает работу счетчика, который суммирует импульсы, поступающие с генератора тактовых импульсов ГТИ. Выходной код счетчика подается на ЦАП, осуществляющий преобразование этого кода в напряжение обратной связи Uос. Подсчет импульсов и линейно-ступенчатое возрастание напряжения обратной связи продолжается до тех пор, пока в некоторый момент времени tок напряжение обратной связи не сравняется с входным напряжением. В этот момент компаратор переключится в состояние логического нуля и запретит поступление тактовых импульсов на счетчик. Интервал от момента запуска АЦП до момента прекращения счета называется временем преобразования.

Время преобразования последовательного АЦП является переменным и зависит от входного напряжения. Его максимальное значение соответствует максимальному входному напряжению. Быстродействие АЦП определяется числом разрядов п и частотой счетных импульсов fсч. При заданной разрядности АЦП время преобразования определяется частотой следования счетных импульсов. Максимальное время преобразования, соответствующее максимальному входному напряжению,

tок = (2n – 1) tсч,

где tсч = 1 / fсч – период следования счетных импульсов.

Быстродействие АЦП существенно возрастает при организации следящего режима. Этот режим характерен тем, что компенсация входного сигнала в каждом последующем цикле преобразования начинается не с конечного (нулевого или максимального) значения, а со значения, установленного в предыдущем цикле, т. е. без переключения счетчика в исходное (нулевое) состояние. Подход к состоянию равновесия при следящем уравновешивании может осуществляться с двух сторон: как снизу, так и сверху. Непосредственно после включения, до достижения первого состояния равновесия, прибор следящего уравновешивания работает аналогично прибору последовательного счета с единичным приближением. Схема АЦП, работающего в следящем режиме, представлена на рис. 14.10.

На сравнивающее устройство, как и в предыдущей схеме, подаются преобразуемое напряжение Uвх и компенсирующее Uос, полученное обратным преобразованием кода в напряжение с помощью ЦАП. Схема сравнения управляет двумя схемами совпадения И, на входы которых подаются импульсы от генератора тактовых импульсов ГТИ. Если Uвх > Uос, открывается схема совпадения, соединяющая генератор с суммирующим входом счетчика СТ. При Uвх < Uос открывается вычитающий вход счетчика и выходной код уменьшается. Как только компенсирующее напряжение Uос достигает преобразуемого, обе схемы совпадения закрываются. Код преобразуемого напряжения определяется состоянием счетчика.

а

б

а

б

Рис. 14.10. Блок-схема АЦП (а) и график следящего уравновешивания (б)