- •М.А. Амелина

- •Список сокращений

- •Логические основы цифровых устройств

- •Общие сведения о цифровых устройствах

- •Алгебра логики

- •Коды и системы счисления

- •Компьютерные форматы данных

- •Элементы цифровых устройств

- •Комбинационные и последовательностные устройства

- •Шифраторы, дешифраторы, преобразователи кодов

- •Мультиплексоры и демультиплексоры

- •Компараторы кодов

- •Двоичные полусумматор и сумматор

- •Арифметико-логические устройства

- •Триггеры

- •Взаимные преобразования триггеров

- •Счетчики

- •Основные параметры и классификация счетчиков

- •Двоичные счетчики

- •Двоично-кодированные счетчики

- •Счетчики с недвоичным кодированием состояний

- •Регистры и регистровые файлы

- •Параллельные регистры

- •Регистровые файлы

- •Сдвигающие регистры

- •Универсальные регистры

- •Аббревиатуры цифровых сигналов, используемые в моделях последовательностных цифровых устройств программы Micro-cap

- •Запоминающие устройства

- •Синтез цифровых автоматов

- •Синтез асинхронных автоматов на rs-триггерах

- •Пример 1

- •Пример 2

- •Пример 3 — Автомат Мили

- •Пример 4 — автомат Мура

- •Синтез асинхронных автоматов на мультиплексорах

- •Пример 1. Асинхронный автомат Мили

- •Пример 2. Асинхронный автомат Мура

- •Синтез синхронных автоматов

- •Пример 3. Синтез счетчика с изменяемым коэффициентом пересчёта

- •Литература

Аббревиатуры цифровых сигналов, используемые в моделях последовательностных цифровых устройств программы Micro-cap

|

…bar |

активный низкий уровень входа или выхода(o) |

|

Borrow |

выход заема для счетчиков |

|

Carry |

выход переноса для счетчиков |

|

Clk |

вход тактовых импульсов |

|

CS |

вход выборки кристалла (корпуса микросхемы) |

|

DOWN |

вход счета на уменьшение |

|

DS (DR, DL) |

последовательные данные для сдвиговых регистров |

|

Load |

параллельная загрузка |

|

Mode |

режим работы |

|

OE, outen |

outputenable, разрешение работы выходов ИМС для трехстабильных схем |

|

R, Reset, Clear |

вход сброса |

|

R/W |

выбор режима чтение/запись |

|

Ser |

последовательный вход |

|

Shift |

Сдвиг |

|

Sh/Ld |

сдвиг/параллельная загрузка |

|

Strobe |

строб, разрешение |

|

UP |

вход счета на приращение |

Запоминающие устройства

Синтез цифровых автоматов

Синтез асинхронных автоматов на rs-триггерах

Пример 1

На основе асинхронных RS-триггеров синтезировать JK-триггер (Master-slave), запоминающий состояние J и K входов при низком уровне синхроимпульса и меняющий состояние на выходе по положительному перепаду синхроимпульса (переход из низкого в высокое состояние).

Синтезируем

устройство как асинхронный автомат,

управляющими сигналами для которого

являются уровень синхроимпульса (0 —

![]() ,

1 —С) и значение информационных

сигналов наJи К входах

(дляJ-входа 0 —

,

1 —С) и значение информационных

сигналов наJи К входах

(дляJ-входа 0 —

![]() ,

1 —J; дляK-входа

0 —

,

1 —J; дляK-входа

0 —

![]() ,

1 —K).

,

1 —K).

Составим граф

переходов разрабатываемого автомата

(рис. 3.1), используя словесный алгоритм

описания его работы, данный в техническом

задании. Вершины графа (устойчивые

состояния автомата) будем кодировать

противогоночно (с использованием кода

Грея). Т.к. для формирования сигнала на

выходе устройства необходим единичный

уровень сигнала на синхровходе, а

информация записывается при нулевом

уровне сигнала C,

вводятся промежуточные состояния на

графе, переход в которые осуществляется

отрицательным уровнем синхроимпульса

Рисунок 3.1 — Граф переходов асинхронного

автомата (JK-триггераMaster-Slave)![]() .

Таким образом, всего получается 4

устойчивых состояния, для кодирования

которых необходимо 2 з

.

Таким образом, всего получается 4

устойчивых состояния, для кодирования

которых необходимо 2 з

Охватим замкнутой линией все состояния на графе переходов, в которых значения одной и той же переменной (состояние одного элемента памяти) равны 1. Эти замкнутые кривые показаны штрих-пунктирной и пунктирной линиями соответственно.

Поскольку вход в подобную замкнутую область и выход из нее требуют линий сигналов возбуждения, обозначаются соответствующие сигналы возбуждения. Стрелками, входящими в область, указывают возбуждение установки (присваивающее переменной единичное значение), а стрелками, выходящими из области, — возбуждение сброса (присваивающее ей нулевое значение).

Составляются два выражения в форме ДНФ (суммы произведений): одно для функции возбуждения установки, а другое для функции возбуждения сброса. Каждое произведение должно содержать входные переменные (сигналы по которым совершается переход) и вторичные переменные, связанные с данным переходом, но не меняющие свои значения. В качестве вторичных переменных выступают двоичные разряды кода состояния в коде Грея. Включение вторичных переменных гарантирует выполнение переходов в правильной последовательности.

![]()

![]() ;

;

![]()

![]() .

.

Строится схема на основе асинхронных RS-триггеров, реализующая полученные логические выражения. Для последующего моделирования с помощью программы Micro-CAP в качестве асинхронных RS-триггеров используются JK или D-триггера с асинхронными входами установки (PREBAR) и сброса (CLRBAR). При этом входы синхронизации и информационные входы не задействуются.

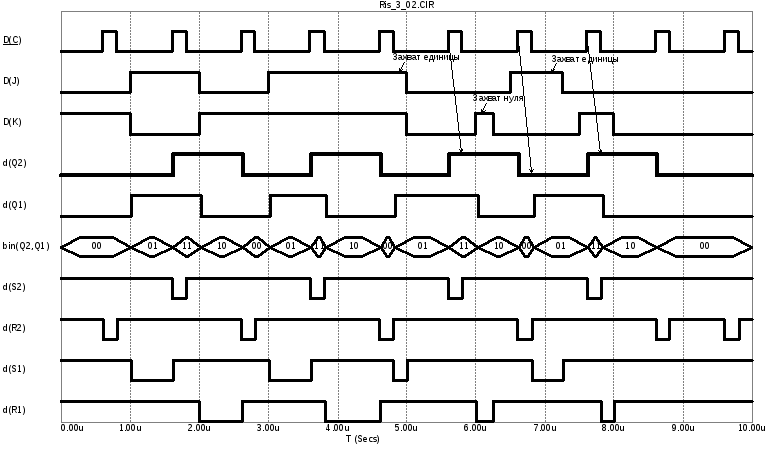

Схема для моделирования с обозначениями необходимых сигналов приведена на рис. 3.2, а, а на рис. 3.2, б приведены временные диаграммы работы автомата, доказывающие его работоспособность.

а

б

Рисунок 3.2 — Двухтактный JK-триггер, меняющий состояние по положительному фронту: а — схема; б — временные диаграммы