- •Министерство образования и науки Российской федерации

- •1. Последовательностные устройства

- •1.1 Триггера.

- •1.2 Регистры.

- •1.3 Счетчики.

- •2. Делители и синтезаторы частоты

- •2.1 Делители частоты с постоянным коэффициентом деления.

- •2.2 Делители частоты с управляемым коэффициентом деления.

- •2.3 Синтезаторы частоты прямого синтеза.

- •2.4 Синтезаторы с фазовой автоподстройкой частоты.

- •3. Полупроводниковые запоминающие

- •3.1 Классификация и структурная организация запоминающих устройств.

- •3.2 Схемотехника запоминающих ячеек накопителей статических запоминающих устройств.

- •3.3 Принципы работы и методы повышения быстродействия динамической памяти.

- •3.4 Постоянные и перепрограммируемые запоминающие устройства.

- •Лехин Сергей Никифорович

- •Часть 3.

3.4 Постоянные и перепрограммируемые запоминающие устройства.

Как отмечалось ранее, записанная в ПЗУ информация фиксирована и может только считываться. Для реализации ПЗУ могут использоваться полупроводниковые диоды, биполярные и полевые транзисторы, а также КМОП структуры. Информация в ПЗУ заносится на этапе изготовления путем фиксации определенных состояний соответствующих ячеек накопителя.

У прощенная

структура одного из вариантов ПЗУ имеет

вид. Матрица накопителя представляет

собой набор биполярных транзисторов,

эмиттера которых до этапа программирования

ни с чем не связаны. Базы этих транзисторов

подключены к адресным шинам выборки

строк. Для адресации столбцов используется

группа вспомогательных транзисторовVT1÷VTK,

коллекторные цепи которых соединены с

соответствующими эмиттерами

многоэмиттерного (VT).

Адресный сигнал для выбора ячейки в

виде напряжения высокого уровня, подается

на соответствующую строку и столбец.

прощенная

структура одного из вариантов ПЗУ имеет

вид. Матрица накопителя представляет

собой набор биполярных транзисторов,

эмиттера которых до этапа программирования

ни с чем не связаны. Базы этих транзисторов

подключены к адресным шинам выборки

строк. Для адресации столбцов используется

группа вспомогательных транзисторовVT1÷VTK,

коллекторные цепи которых соединены с

соответствующими эмиттерами

многоэмиттерного (VT).

Адресный сигнал для выбора ячейки в

виде напряжения высокого уровня, подается

на соответствующую строку и столбец.

Если память не запрограммирована, то сигнал выбора столбца в виде напряжения высокого уровня откроет один из транзисторов нижнего ряда и все транзисторы выбранной строки накопителя. При этом соответствующий эмиттер многоэмиттерного транзистора через резистор окажется подключенным к корпусу, а его связь с источником питания ввиду отсутствия перемычки у транзисторов накопителя будет отсутствовать Так как на базу этого транзистора постоянно подано некоторое опорное напряжение, то многоэмиттерный транзистор откроется и на его коллекторе, а также на выходе запоминающего устройства сформируется сигнал логического нуля. Ситуация будет аналогичной при переборе всех ячеек накопителя, что позволяет считать, что в исходном состоянии в них записаны нули.

Н а

этапе программирования с помощью

специальной маски в эмиттерных цепях

требуемых ячеек формируются токопроводящие

перемычки. При выборе такой ячейки

откроются как транзистор, входящий в

ее состав, так и транзистор, подключенный

к соответствующему столбцу матрицы.

Так как сопротивление перемычки мало,

то на связанный с ней эмиттер

многоэмиттерного транзистора будет

подано напряжение источника питания.

При адресации активизируется лишь один

столбец, а эмиттера многоэмиттерного

транзистора отключены от потенциальных

шин и не повлияют на его работу. В данной

ситуации транзисторVTокажется закрытым и на его коллекторе,

связанном с усилителем считывания

появится высокий потенциал, соответствующий

выходному сигналу логической единицы.

а

этапе программирования с помощью

специальной маски в эмиттерных цепях

требуемых ячеек формируются токопроводящие

перемычки. При выборе такой ячейки

откроются как транзистор, входящий в

ее состав, так и транзистор, подключенный

к соответствующему столбцу матрицы.

Так как сопротивление перемычки мало,

то на связанный с ней эмиттер

многоэмиттерного транзистора будет

подано напряжение источника питания.

При адресации активизируется лишь один

столбец, а эмиттера многоэмиттерного

транзистора отключены от потенциальных

шин и не повлияют на его работу. В данной

ситуации транзисторVTокажется закрытым и на его коллекторе,

связанном с усилителем считывания

появится высокий потенциал, соответствующий

выходному сигналу логической единицы.

Устанавливая перемычку, в ячейку накопителя можно занести единичное значение информационного бита, но изменить ситуацию нельзя, так как перемычки не могут быть уничтожены. Вследствие этого при отключении питания записанная в постоянное запоминающее устройство информация сохраняется. Микросхемы ПЗУ маркируются буквами РЕ, например К155РЕ21, и такие устройства широко используются в качестве управляющей памяти и преобразователей кодов.

Одноразрядные однократно программируемые ПЗУ имеют аналогичную структуру, но на этапе изготовления перемычки встраиваются в эмиттерные цепи всех транзисторов накопителя, то есть во все ячейки памяти записываются логические единицы. Такие перемычки изготавливаются на основе нихрома, либо состоят из слоев поликристаллического кремния и могут быть разрушены путём пропускания через них импульса тока достаточно большой величины, что изменяет состояние ячейки на противоположное.

В ариант

структуры многоразрядного запоминающего

устройства с плавкими перемычками

выглядит следующим образом. От адресного

дешифратора на базу одного из транзисторов

поступает сигнал выборки в виде напряжения

высокого уровня. При этом через эмиттера,

в которых имеются перемычки и внешние

резисторы будут протекать токи, формируя

на них сигналы высокого уровня (логической

единицы). Если перемычка отсутствует,

то ток и напряжение в цепи окажутся

нулевыми. Здесь один многоэмиттерный

транзистор хранит все разряды слова.

Память такого типа обычно имеет структуру

2Dи невелика по объему.

ариант

структуры многоразрядного запоминающего

устройства с плавкими перемычками

выглядит следующим образом. От адресного

дешифратора на базу одного из транзисторов

поступает сигнал выборки в виде напряжения

высокого уровня. При этом через эмиттера,

в которых имеются перемычки и внешние

резисторы будут протекать токи, формируя

на них сигналы высокого уровня (логической

единицы). Если перемычка отсутствует,

то ток и напряжение в цепи окажутся

нулевыми. Здесь один многоэмиттерный

транзистор хранит все разряды слова.

Память такого типа обычно имеет структуру

2Dи невелика по объему.

Для удаления перемычек, то есть записи в выбранные ячейки накопителя логических нулей используются специальные устройства – программаторы. Так как разрушенные перемычки не восстанавливаются, то программирование, то есть запись произвольного массива данных, можно осуществить лишь один раз. Для маркировки микросхем однократно программируемых ПЗУ используют буквы РТ (К556РТ5, К556РТ11).

Такие устройства широко используются при изготовлении мелкосерийной аппаратуры, так как разработка шаблонов для программирования ПЗУ требует больших затрат и использование однократно программируемой памяти становится экономически целесообразным при партиях микросхем в десятки и более тысяч штук. Как и ОЗУ, ПЗУ обладают достаточно высоким быстродействием, их емкость достигает сотен килобит.

Оперативные и постоянные запоминающие устройства, обладают каждое своими особенностями, ОЗУ не хранят данные после выключения питания, а ПЗУ не позволяют изменять их произвольным образом. Однако часто встречаются ситуации, когда информацию требуется записывать, считывать, а кроме того она должна оставаться неизменной (сохраняться) и при отключении источников питания.

Примером таких устройств является память на магнитных носителях (дискеты, винчестеры) и перезаписываемых компакт-дисках. Их существенным недостатком является очень малая по сравнению с оперативными запоминающими устройствами скорость обмена данными и наличие механических узлов.

Однако, используя специальные виды полевых транзисторов, можно реализовать полупроводниковую память с требуемыми свойствами (энергонезависимую), которая относится к классу перепрограммируемой - ППЗУ или PROM.

Вариант полевого транзистора, используемого в запоминающих устройствах типаEPROM, представляет собой МОП транзистор с плавающим затвором. Он относится к классу транзисторов с лавинной инжекцией зарядов (ЛИЗМОП). Его упрощенная структура выглядит следующим образом.

З десь,

как и в обычном МОП транзисторе с

индуцированным каналом имеются области

стока, истока и подложки, однако электрода

затвора нет. Внутрь диэлектрика внедряется

токопроводящий слой, состоящий из

металла, либо поликристаллического

кремния. В исходном состоянии такой

транзистор ток не проводит, так как обаpn-перехода закрыты.

десь,

как и в обычном МОП транзисторе с

индуцированным каналом имеются области

стока, истока и подложки, однако электрода

затвора нет. Внутрь диэлектрика внедряется

токопроводящий слой, состоящий из

металла, либо поликристаллического

кремния. В исходном состоянии такой

транзистор ток не проводит, так как обаpn-перехода закрыты.

Однако, если на переход сток-подложка подать импульс обратного напряжения достаточно большой амплитуды, то произойдет лавинный пробой p-nструктуры. Прилегающая к переходу подзатворная область обогатится электронами, при этом часть из них, получившая достаточную энергию сможет преодолеть потенциальный барьер диэлектрика и проникнуть в плавающий затвор. Вследствие большой напряженности электрического поля при пробое, вступают в силу квантовомеханический эффект туннелирования. Если длительность программирующего импульса установить небольшой, то электрический пробой после снятия обратного напряжения не перейдет в тепловой и переход восстановит свои свойства.

П од

воздействием отрицательного потенциала

поля, создаваемого накопленными

электронами, из подложки в подзатворную

область подтянутся дырки, образуя

токопроводящий канал. При наличии

внешнего напряжения между истоком и

стоком транзистор станет проводить

ток.

од

воздействием отрицательного потенциала

поля, создаваемого накопленными

электронами, из подложки в подзатворную

область подтянутся дырки, образуя

токопроводящий канал. При наличии

внешнего напряжения между истоком и

стоком транзистор станет проводить

ток.

У электронов находящихся в слое затвора недостаточно энергии для преодоления запрещенной зоны диэлектрика, поэтому они будут сохранятся там теоретически бесконечное время, а реально в течение десятков и более тысяч часов.

В накопителе, ячейки которого реализованы на ЛИЗМОП транзисторах, часть из них можно перевести в проводящее состояние, поставив этому в соответствие хранение логической единицы, а оставшиеся не программировать (там будут записаны нули). Такие состояния транзисторов сохранятся в течение достаточно длительного времени, независимо от того, включено питание или нет. При считывании информации определяется проводит или нет выбранная ячейка ток и формируется соответствующий выходной сигнал.

Чтобы занести новый массив данных часть ячеек потребуется перевести в исходное, непроводящее состояние. Однако реализовать это подачей электрического сигнала противоположной полярности на p-nпереход сток-подложка не удастся, так как он при этом откроется. Напряжение на переходе составит доли вольта и энергии, которую при этом получат дырки, будет недостаточно для их для туннелирования через диэлектрик, чтобы в ходе рекомбинации скомпенсировать накопленный ранее заряд электронов.

Поэтому для стирания информации дополнительную энергию электронам, чтобы они смогли покинуть плавающий затвор, сообщают извне. Делается это путем облучения поверхности затвора ультрафиолетовым светом достаточной интенсивности.

Так как один транзистор на кристалле имеет очень малые размеры (единицы и доли микрона), то осветить только требуемый технически невозможно. Поэтому перед новым циклом записи облучают поверхность кристалла и все ячейки накопителя переводятся в непроводящее состояние. Затем требуемые программируют. На таком принципе работают микросхемы серии К573, имеющие информационную емкость до нескольких мегабит. В их корпус встроено специальное окошко для доступа ультрафиолетового излучения к кристаллу. Количество циклов стирания (перезаписи) без ухудшения свойств ППЗУ может достигать тысяч и более. Микросхемы памяти такого типа маркируются буквами РФ (К573РФ4, К573РФ8).

Особенность ППЗУ на ЛИЗМОП транзисторах состоит в том, что время стирания данных измеряется минутами, процедура записи может, в зависимости от емкости, занимать десятки секунд, а чтение информации происходит достаточно быстро с временами выборки в десятки-сотни наносекунд. Поэтому такие запоминающие устройства не могут использоваться в качестве оперативной памяти. Основная область их применения - управляющая память для микроконтроллеров и преобразователи кода. Возможность перезаписи данных позволяет достаточно просто вносить коррективы в программы при отладке.

С целью удешевления аналогичные устройства могут выпускаться в корпусах без окошка и поэтому программируются лишь один раз. Они называются OTPPROM.

Е ще

одна разновидность полевых транзисторов,

которые применяются в перепрограммируемых

запоминающих устройствах, называется

МНОП транзистор. По структуре он похож

на обычный МОП транзистор с индуцированным

каналом, но подзатворный диэлектрик

состоит из двух слоев. Один из них

выполняется из двуокиси кремния, а для

другого используется его нитрид.

ще

одна разновидность полевых транзисторов,

которые применяются в перепрограммируемых

запоминающих устройствах, называется

МНОП транзистор. По структуре он похож

на обычный МОП транзистор с индуцированным

каналом, но подзатворный диэлектрик

состоит из двух слоев. Один из них

выполняется из двуокиси кремния, а для

другого используется его нитрид.

Использование двух типов диэлектриков приводит к тому, что на границе их раздела могут накапливаться электрические заряды. Так как эта граница не связана с внешними цепями, то они могут храниться там достаточно долго, до десятков лет. В зависимости от знака введенного заряда будет меняться пороговое напряжение транзистора, то есть напряжение между затвором и истоком, при котором он начнет проводить ток.

Заряды на границу раздела диэлектриков вводятся путем подачи на затвор импульса соответствующей полярности амплитудой до 15÷20 вольт. При воздействии положительного напряжения происходит туннелирование электронов из подложки и накопление их на границе диэлектрических слоев. Если при программировании напряжение на затворе отрицательно, то в этой области накопятся дырки (на самом деле часть электронов диэлектриков уйдет в подложку).

В первом случае пороговое напряжение транзистора станет меньше, так как под действием отрицательного потенциала накопленных электронов часть дырок из подложки подтянется в подзатворную область, и для образования токопроводящего канала понадобится меньшее внешнее напряжение. Во втором случае дырки будут отталкиваться вглубь подложки и потребуется подать большее напряжение на затвор чтобы перевести транзистор в проводящее состояние.

Е сли

из таких транзисторов выполнить

накопитель, то часть его ячеек можно

перевести в состояние с высоким пороговым

напряжением, а остальные в состояние с

низким. При этом можно будет считать,

что в одних ячейках будут записаны

логические нули, а в других – единицы.

сли

из таких транзисторов выполнить

накопитель, то часть его ячеек можно

перевести в состояние с высоким пороговым

напряжением, а остальные в состояние с

низким. При этом можно будет считать,

что в одних ячейках будут записаны

логические нули, а в других – единицы.

Для считывания состояния ячейки на затвор необходимо подать напряжение, величина которого по модулю больше нижнего порогового и меньше верхнего. Если транзистор находится в низкопороговом состоянии, он откроется и, при наличии напряжения, в цепи сток-исток потечет ток, высокопороговый окажется запертым.

Для записи новых данных в накопитель с такими ячейками предварительного стирания прежней информации не требуется, хотя обычно данную процедуру проводят, причем это можно делать для отдельного транзистора.

Данный тип памяти называется EEPROM. Она обладает такими же особенностями, что и предшествующий вариант (EPROM), то есть значительными временами перезаписи и высоким быстродействием при считывании. Микросхемы такой памяти маркируются буквами РР (К1601РР1).

Д альнейшие

работы в области совершенствования

перепрограммируемых запоминающих

устройств привели к созданию флэш-памяти,

использующей в качестве запоминающих

ячеек двухзатворные ЛИЗМОП транзисторы.

Его упрощенная структура выглядит

следующим образом.

альнейшие

работы в области совершенствования

перепрограммируемых запоминающих

устройств привели к созданию флэш-памяти,

использующей в качестве запоминающих

ячеек двухзатворные ЛИЗМОП транзисторы.

Его упрощенная структура выглядит

следующим образом.

Здесь кроме управляющего затвора используется и плавающий, что позволяет реализовывать процедуры программирования и стирания ячеек при напряжениях на затворе, сравнимых с напряжениями питания аппаратуры в которой такая память устанавливается.

Для того, чтобы не использовать при программировании двуполярные импульсы, возврат ячейки в непроводящее состояние (стирание) осуществляется подачей на затвор нулевого потенциала, а на исток положительного. При этом накопленные в плавающем затворе электроны будут за счет эффекта туннелирования выведены в подложку.

Я чейка

накопителя флэш-памяти может состоять

из одного, либо из двух транзисторов,

среди которых один является обычным.

На основе первой разновидности реализованаNORархитектура, имеющая

вид. Здесь двухзатворные транзисторы

подключены между соответствующими

строками и столбцами матрицы накопителя.

Для получения доступа к содержимому

ячейки на адресную линию строки

(словарную) и столбца (битовую) подается

напряжение высокого уровня, причем

последнее поступает через резистор.

Если на плавающем затворе имеется

соответствующий заряд, то выбранный

транзистор откроется и на битовой линии

сформируется сигнал низкого уровня. В

противном случае потенциал битовой

линии останется высоким.

чейка

накопителя флэш-памяти может состоять

из одного, либо из двух транзисторов,

среди которых один является обычным.

На основе первой разновидности реализованаNORархитектура, имеющая

вид. Здесь двухзатворные транзисторы

подключены между соответствующими

строками и столбцами матрицы накопителя.

Для получения доступа к содержимому

ячейки на адресную линию строки

(словарную) и столбца (битовую) подается

напряжение высокого уровня, причем

последнее поступает через резистор.

Если на плавающем затворе имеется

соответствующий заряд, то выбранный

транзистор откроется и на битовой линии

сформируется сигнал низкого уровня. В

противном случае потенциал битовой

линии останется высоким.

Название архитектуры NORпроисходит от английской аббревиатуры обозначения логической операции ИЛИ-НЕ, результат которой - единица, лишь когда все операнды равны нулю и нулевой в остальных случаях. Под нулевым значением операнда понимается непроводящее состояние ячеек памяти. Единичный сигнал на выбранной битовой линии будет присутствовать только если транзисторы всех ячеек, подключенных к ней закрыты.

А рхитектураNORобеспечивает произвольный

быстрый доступ к ячейкам, однако процессы

записи и стирания происходят достаточно

медленно. Вследствие относительно

высокого напряжения программирования,

для обеспечения изоляции соседних

битовых и словарных линий их приходится

располагать на достаточно большом

расстоянии друг от друга, что увеличивает

средний размер ячейки.

рхитектураNORобеспечивает произвольный

быстрый доступ к ячейкам, однако процессы

записи и стирания происходят достаточно

медленно. Вследствие относительно

высокого напряжения программирования,

для обеспечения изоляции соседних

битовых и словарных линий их приходится

располагать на достаточно большом

расстоянии друг от друга, что увеличивает

средний размер ячейки.

Другой разновидностью архитектуры флэш-памяти является NAND, соответствующая реализации логической операции И-НЕ. Нулевое значение при этом получается, когда все операнды равны единице, а единичное во всех остальных случаях. Как видно из приведенной структуры двухзатворные транзисторы соединяются по столбцу последовательно.

При подаче высокого

напряжения на линии выборки

![]() ,

,![]() к битовой линии оказывается подключенным

столбец запоминающих ячеек. В ходе

программирования часть из них переводятся

в состояние, когда они проводят ток и

при нулевом напряжении на затворе

(хранение логической единицы), а остальные

открываются лишь при положительном

управляющем сигнале.

к битовой линии оказывается подключенным

столбец запоминающих ячеек. В ходе

программирования часть из них переводятся

в состояние, когда они проводят ток и

при нулевом напряжении на затворе

(хранение логической единицы), а остальные

открываются лишь при положительном

управляющем сигнале.

Д ля

выбора строки на все словарные шины

кроме выбираемой поступают сигналы

высокого уровня, открывающие соответствующие

ячейки. Если транзистор, на затвор

которого поступает нулевое напряжение,

открыт то сигнал на битовой шине будет

нулевым, что соответствует считыванию

единичного состояния ячейки. Транзистор,

переведенный в ходе программирования

в состояние с положительным пороговым

напряжением, в этом случае окажется

запертым и на битовой шине появится

сигнал высокого уровня, соответствующий

считыванию логического нуля.

ля

выбора строки на все словарные шины

кроме выбираемой поступают сигналы

высокого уровня, открывающие соответствующие

ячейки. Если транзистор, на затвор

которого поступает нулевое напряжение,

открыт то сигнал на битовой шине будет

нулевым, что соответствует считыванию

единичного состояния ячейки. Транзистор,

переведенный в ходе программирования

в состояние с положительным пороговым

напряжением, в этом случае окажется

запертым и на битовой шине появится

сигнал высокого уровня, соответствующий

считыванию логического нуля.

Архитектура NANDпозволяет добиться более компактного расположения транзисторов и обеспечивает ускорение процесса записи по сравнению с архитектуройNOR.

По основным принципам работы флэш-память подобна EEPROM, однако имеет ряд особенностей. В частности стирание информации осуществляется электрическим путем либо во всем накопителе сразу, либо в достаточно больших его блоках. Кроме того, напряжение программирования не превышает уровня напряжения источника питания, что позволяет перезаписывать данные непосредственно в устройстве, где расположена микросхема памяти.

В современных разновидностях флэш-памяти время доступа составляет десятки наносекунд, при емкости в сотни и более мегабайт. Такие устройства широко используются в качестве сменных накопителей, в цифровых фотокамерах, плейерах, для замены дискет и т.п.

Увеличение емкости, быстродействия и количества рабочих циклов перепрограммируемых ЗУ достигается как совершенствованием технологии, так и использованием новых физических принципов и идеологий.

Ф

ирмойIntelразработан новый вид

флэш-памяти -StrataFlash,

у которой в одном элементе накопителя

могут храниться два бита данных. Это

обеспечивается фиксацией при записи

четырех значений заряда. В этом случае

транзистор будет иметь четыре различных

уровня порогового напряжения

ирмойIntelразработан новый вид

флэш-памяти -StrataFlash,

у которой в одном элементе накопителя

могут храниться два бита данных. Это

обеспечивается фиксацией при записи

четырех значений заряда. В этом случае

транзистор будет иметь четыре различных

уровня порогового напряжения![]() ,

каждому из которых можно поставить в

соответствие двухбитовую комбинацию

– 00, 01, 10 и 11. При считывании ток, протекающий

через такую ячейку, будет зависеть от

установленного в ходе программирования

порогового напряжения. Каждому значению

заряда и тока можно поставить в

соответствие и сформировать на выходе

запоминающего устройства закрепленную

за определенным состоянием транзистора

двухбитовую комбинацию. Такой подход

позволяет при тех же размерах кристалла

вдвое увеличить емкость памяти.

,

каждому из которых можно поставить в

соответствие двухбитовую комбинацию

– 00, 01, 10 и 11. При считывании ток, протекающий

через такую ячейку, будет зависеть от

установленного в ходе программирования

порогового напряжения. Каждому значению

заряда и тока можно поставить в

соответствие и сформировать на выходе

запоминающего устройства закрепленную

за определенным состоянием транзистора

двухбитовую комбинацию. Такой подход

позволяет при тех же размерах кристалла

вдвое увеличить емкость памяти.

Эта идея получила дальнейшее развитие в микросхемах, ячейки которых могут фиксировать несколько сотен уровней заряда, что позволяет использовать такие устройства для записи, хранения и многократного воспроизведения дискретизированных аналоговых сигналов.

Новые физические принципы были реализованы в устройствах перепрограммируемой памяти типа FRAMиMRAM. Первая разновидность относится к ферроэлектрической, а вторая к полупроводниковой магнитной памяти. Ферроэлектрик представляет собой нелинейный диэлектрик, содержащий атомы ферромагнитных материалов. Под действием электрического поля он может быть переведен в состояния с разной поляризацией и сохранять их в течение длительного времени. Конденсатор с использованием такого диэлектрика имеет разную емкость, зависящую от направления поляризации, что приводит к разной скорости его перезаряда. Этот эффект трансформируется в выходные сигналы запоминающего устройства, соответствующие наличию в ячейке логического нуля, либо единицы. Опытные образцы памятиFRAMимеют емкость порядка мегабит при временах доступа менее 60 нС.

Физической основой магнитной (магниторезистивной) памяти являются субмикронные многослойные структуры из материалов, которые могут менять свое состояние под действием внешнего магнитного поля. Аналогичные принципы используются при реализации запоминающих устройств на таких носителях, как дискеты и винчестеры. Однако запись и считывание данных там осуществляется магнитной головкой перемещающейся относительно поверхности движущегося носителя.

В памяти MRAMиз магнитных материалов формируются ячейки с размерами менее микрона, через которые проходят шины записи и считывания. Пропуская по ним соответствующие токи можно либо изменить состояния ячейки, либо его считать, при этом количество циклов записи-чтения не ограничено. По такой технологии разработаны микросхемы с емкостью более 256 Кбайт и временами доступа менее 30 нС, у опытных образцов цикл чтения занимает 6 нС.

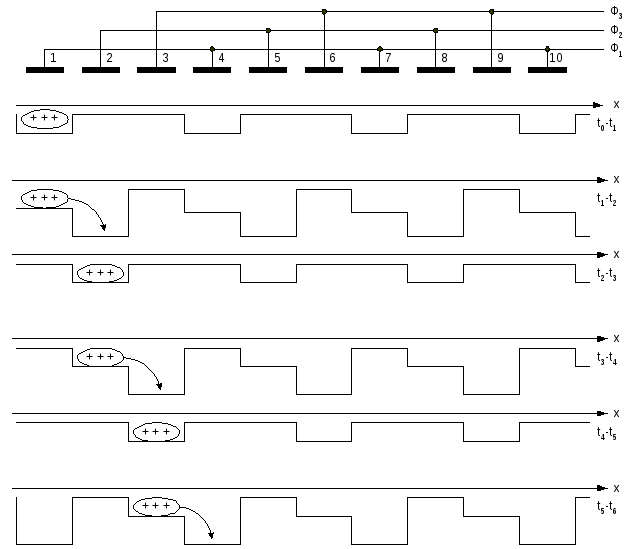

Как уже отмечалось, в группу безадресных запоминающих устройств входят стековые, которые могут быть построены на регистрах сдвига, каждая ячейка которого представляет собой триггер. Однако техническая реализация таких устройств при глубине стека в сотни и тысячи разрядов затруднительна. В этом случае альтернативой схемотехническим решениям выступают структуры на приборах с зарядовой связью (ПЗС).

Они представляют собой набор МОП транзисторов близко расположенных на одной подложке и взаимодействующих друг с другом. Упрощенная структура одного из вариантов такого устройства.

Н а

кристалле кремнияn-типа

наращивается слой окисла и на нем

напыляется ряд металлических затворов

с очень маленьким (доли микрона)

расстоянием между ними, которые

объединяются в три группы. На краях

кристалла формируютсяp-nпереходы, служащие для ввода и вывода

информации.

а

кристалле кремнияn-типа

наращивается слой окисла и на нем

напыляется ряд металлических затворов

с очень маленьким (доли микрона)

расстоянием между ними, которые

объединяются в три группы. На краях

кристалла формируютсяp-nпереходы, служащие для ввода и вывода

информации.

Принцип работы такого прибора заключается в перемещении приповерхностного заряда дырок (зарядового пакета) от левого края подложки к правому, что можно интерпретировать как продвижение логической единицы по разрядам регистра сдвига. Если зарядового пакета нет, то можно считать, что в таком случае перемещается аналог логического нуля.

Для перемещения

пакетов, на группы затворов ПЗС структуры

подаются напряжения отрицательной

полярности

![]() ,

меняющиеся во времени следующим образом.

,

меняющиеся во времени следующим образом.

Пусть в промежутке времени t0-t1на левый (входной)p-nпереход подается импульс напряжения в прямом направлении. При этом через него потечет ток и под первым затвором начнут накапливаться дырки, притягиваемые туда электрическим полем. Зарядовый пакет сгруппируется в области первого затвора, так как потенциалы близлежащих к нему более положительны.

В промежуток

времени t1-t2большее по величине отрицательное

напряжение появится на втором затворе

и дырки переместятся к нему. В интервалеt2-t3движения зарядов не будет, это этап

хранения, в течение которого самый

отрицательный потенциал оказывается

у второго затвора. На следующем этапе

наибольшее отрицательное напряжение

будет приложено к третьему затвору,

пакет дырок переместится к н ему

и так далее.

ему

и так далее.

После прохождения всего кристалла, зарядовый пакет появится у правого p-nперехода, смещенного под действием внешнего напряжения в обратном направлении. Когда потенциал ближайшего затвора станет близким к нулю, пакет втянется в р-область и вызовет протекание импульса тока по нагрузочному резистору. Это можно интерпретировать как появление занесенного ранее единичного сигнала на последнем разряде регистра сдвига.

В процессе перемещения первого зарядового пакета, можно, например на интервале t12-t13, ввести второй, затем третий и т.д. Через 6Nтактов данные будут считаны в том же порядке, в каком они заносились. Здесь, как и в регистре сдвига считывание происходит с разрушением информации. Если потенциалы затворов зафиксировать, то зарядовые пакеты сохранятся под теми они наиболее отрицательны.

Такая достаточно сложная форма сигналов управления необходима чтобы не происходило размазывания зарядов между соседними затворами и с целью обеспечения достаточного времени. для их группировки в пакеты. Картина распределения потенциалов вдоль ПЗС структуры в разные моменты времени выглядит таким образом.

Н а

каждом этапе перемещения зарядовый

пакет "сваливается" в потенциальную

яму всегда находящуюся справа от него,

что и вызывает их направленное перемещение.

а

каждом этапе перемещения зарядовый

пакет "сваливается" в потенциальную

яму всегда находящуюся справа от него,

что и вызывает их направленное перемещение.

П ри

использовании двухуровневых управляющих

сигналов на перетекание зарядов остается

только время фронта импульса и, кроме

того, заряды могут "выдавливаться"

в обе стороны, что приведет к размазыванию

пакета.

ри

использовании двухуровневых управляющих

сигналов на перетекание зарядов остается

только время фронта импульса и, кроме

того, заряды могут "выдавливаться"

в обе стороны, что приведет к размазыванию

пакета.

ПЗС структуры отличает высокая технологичность изготовления, небольшая мощность потребления (единицы микроватт на бит) и малые габариты при большой разрядности. Стек глубиной в десятки килобит можно разместить на кристалле длиной в несколько миллиметров.

ПЗС приборы обладают свойством, которое позволяет использовать их для обработки не только цифровых, но и аналоговых сигналов. Это связано с тем, что процедура перемещения зарядовых пакетов не зависит от их величины. Количество вводимых зарядов пропорционально уровню входного напряжения и времени его воздействия на вход устройства. При этом с соответствующей задержкой на выходе ПЗС будут формироваться сигналы пропорциональным входным уровням напряжений.

П ри

подаче сигналаS(t

его на вход ПЗС, в соответствующие

моменты времени будут формироваться

зарядовые пакеты пропорциональные его

уровням. Они начнут перемещаться по

кристаллу и, через определенное время

достигнув области считывающего электрода,

выйдут в том же порядке.

ри

подаче сигналаS(t

его на вход ПЗС, в соответствующие

моменты времени будут формироваться

зарядовые пакеты пропорциональные его

уровням. Они начнут перемещаться по

кристаллу и, через определенное время

достигнув области считывающего электрода,

выйдут в том же порядке.

На

выходе сформируется поток импульсов с

амплитудами пропорциональными мгновенным

значениям входного сигнала. После

обработки (фильтрации) можно получить

его практически полную копию, задержанную

относительно оригинала на время,

определяемое количеством групп затворов

в ПЗС приборе и частотой следования

тактирующих импульсов. В данном режиме

ПЗС структура будет выполнять роль

линии задержки аналоговых сигналов.

Временем задержки можно оперативно

управлять путем изменения частоты

тактирования

![]() .

.

Пакеты дырок в подзатворные области могут быть введены не только путем перехвата носителей инжектированных входным p-n переходом, но и при освещении соответствующих областей кристалла, если электроды затворов прозрачны. При этом величина накапливаемого за определенное время заряда будет пропорциональна освещенности. В отличие от предыдущей ситуации здесь все зарядовые пакеты вводятся одновременно, а не один за другим.

П ри

организации цепочек транзисторов ПЗС

структуры в прямоугольную матрицу и

соединении выхода нижерасположенной

строки со входом верхней, такое устройство

может использоваться в качестве

формирователя телевизионного сигнала.

ри

организации цепочек транзисторов ПЗС

структуры в прямоугольную матрицу и

соединении выхода нижерасположенной

строки со входом верхней, такое устройство

может использоваться в качестве

формирователя телевизионного сигнала.

Если по окончании засветки начать процедуру тактирования, то импульсы напряжения, пропорциональные освещенности последовательно друг за другом и строка за строкой начнут проходить на выход схемы. С него будет сниматься видеосигнал, который гораздо более сложными способами формируется в электровакуумных телевизионных передающих трубках. Такие фоточувствительные ПЗС матрицы используются в видеокамерах, цифровых фотоаппаратах и подобных устройствах. Количество элементов у них достигает миллионов.

При практической реализации ПЗС структур возникает ряд проблем. Одна из них заключается в том, что дырки из потенциальных ям под затворами частично рекомбинируют с электронами подложки, уменьшая величину зарядового пакета, кроме того, на структуру выходного сигнала влияют управляющие импульсы и т. п. Путем усложнения топологии ПЗС структур и совершенствования технологии их изготовления разработаны приборы с двухфазным управлением, с отводами от ячеек и т.п., используемые в корреляционных системах обработки сигналов.

Список литературы.

Зельдин Е.А. Цифровые интегральные микросхемы в информационно-измерительной аппаратуре.- Л.: Энергоатомиздат, 1986.- 280 с., ил.

Цифровая вычислительная техника. Учебник для вузов. Под. Ред. Евреинова. – М.: Радио и связь, 1991.-464 с., ил.

Опадчий Ю.Ф. и др. Аналоговая и цифровая электроника (Полный курс): Учебник для вузов. - М.: Горячая линия – Телеком, 2000. – 768 с.: ил.

Шило В.Л. Популярные цифровые микросхемы. Справочник М.: Радио и связь, 1987.- 252 с., ил.

Цифровые устройства на комплементарных МДП интегральных микросхемах.- М.: Радио и связь, 1983.-272 с., ил.

Угрюмов Е.П. Цифровая схемотехника. – СПб.: БХВ – Санкт – Петербург, 2000.- 528 с.: ил.

Потемкин И.С., Функциональные узлы цифровой автоматики – М.: Энергоатомиздат, 1988. – 320 с.: ил.

ОГЛАВЛЕНИЕ

Стр.

Последовательностные цифровые устройства…... 3

Триггера………………………………………. 3

Регистры………………………………………. 24

Счетчики ..................….……………………… 51

Делители и синтезаторы частоты……………......... 89

Делители частоты с постоянным

коэффициентом деления…………………………… 89

Делители частоты с управляемым

коэффициентом деления…………………………… 92

Синтезаторы частоты прямого синтеза………. 92

Синтезаторы с фазовой автоподстройкой

частоты……………………………………………….. 97

Полупроводниковые запоминающие устройства………………………................................................ 100

Классификация и структурная организация

запоминающих устройств…………………................ 100

Схемотехника ячеек накопителей

статических запоминающих устройств….................. 122

Принципы работы и методы повышения

быстродействия динамической памяти…………….. 129

Постоянные и перепрограммируемые

запоминающие устройства………………………….. 151

Список литературы………………………………….. 170