- •Министерство образования и науки Российской федерации

- •1. Последовательностные устройства

- •1.1 Триггера.

- •1.2 Регистры.

- •1.3 Счетчики.

- •2. Делители и синтезаторы частоты

- •2.1 Делители частоты с постоянным коэффициентом деления.

- •2.2 Делители частоты с управляемым коэффициентом деления.

- •2.3 Синтезаторы частоты прямого синтеза.

- •2.4 Синтезаторы с фазовой автоподстройкой частоты.

- •3. Полупроводниковые запоминающие

- •3.1 Классификация и структурная организация запоминающих устройств.

- •3.2 Схемотехника запоминающих ячеек накопителей статических запоминающих устройств.

- •3.3 Принципы работы и методы повышения быстродействия динамической памяти.

- •3.4 Постоянные и перепрограммируемые запоминающие устройства.

- •Лехин Сергей Никифорович

- •Часть 3.

3.3 Принципы работы и методы повышения быстродействия динамической памяти.

Уменьшить габариты и энергопотребление запоминающей ячейки удалось при использовании в качестве нее микроконденсатора, который может быть либо заряжен, либо разряжен – то есть способен находиться в двух состояниях. В идеале заряд на конденсаторе сохраняется бесконечно долго и его присутствие соответствует наличию разности потенциалов (напряжения) на обкладках. Состояние конденсатора можно определить путем измерения напряжения между его обкладками.

Л юбой

измерительный прибор потребляет

некоторую мощность из цепи измерения,

при этом через его входной каскад

протекает некоторый ток. Для целей

анализа сам прибор (вольтметр) можно

считать идеальным, но имеющим в цепи

измерения некоторое сопротивление,

называемое входным.

юбой

измерительный прибор потребляет

некоторую мощность из цепи измерения,

при этом через его входной каскад

протекает некоторый ток. Для целей

анализа сам прибор (вольтметр) можно

считать идеальным, но имеющим в цепи

измерения некоторое сопротивление,

называемое входным.

При подключении

вольтметра к разряженному конденсатору

он покажет нулевое напряжение. Если же

конденсатор был заряжен, то в процессе

измерения напряжение на нем станет

уменьшаться с постоянной времени

![]() .

Ее значение соответствует времени,

через которое напряжение в цепи изменится

ве раз, гдее -

основание натуральных логарифмов,

равное 2,7182818…. Если постоянная времени

мала, то в процессе измерения конденсатор

разрядится и имевшаяся в виде наличия

заряда информация окажется разрушенной.

.

Ее значение соответствует времени,

через которое напряжение в цепи изменится

ве раз, гдее -

основание натуральных логарифмов,

равное 2,7182818…. Если постоянная времени

мала, то в процессе измерения конденсатор

разрядится и имевшаяся в виде наличия

заряда информация окажется разрушенной.

Чтобы этого избежать требуется иметь либо измерительный прибор с очень высоким входным сопротивлением, или конденсатор большой емкости.

П ри

использовании конденсатора в качестве

ячейки памяти задача упрощается тем,

что нет необходимости измерять конкретное

значение напряжения, достаточно

определять лишь два его различающихся

уровня. В этом случае в качестве

измерительного устройства можно

использовать полевой транзистор с

изолированным затвором и индуцированным

каналом, вольтамперная характеристика

которого имеет вид, подключив запоминающий

конденсатор между затвором и истоком.

Если напряжение на нем будет больше

порогового, то транзистор окажется

открытым и выходное напряжение будет

близко к нулю. В противном случае он

будет заперт и потенциал выхода станет

практически равным напряжению источника

питания.

ри

использовании конденсатора в качестве

ячейки памяти задача упрощается тем,

что нет необходимости измерять конкретное

значение напряжения, достаточно

определять лишь два его различающихся

уровня. В этом случае в качестве

измерительного устройства можно

использовать полевой транзистор с

изолированным затвором и индуцированным

каналом, вольтамперная характеристика

которого имеет вид, подключив запоминающий

конденсатор между затвором и истоком.

Если напряжение на нем будет больше

порогового, то транзистор окажется

открытым и выходное напряжение будет

близко к нулю. В противном случае он

будет заперт и потенциал выхода станет

практически равным напряжению источника

питания.

Т акой

конденсатор имеется в каждом полевом

транзисторе – это паразитная входная

емкость затвор-исток. Таким образом,

один транзистор может выполнять функции

элементарной ячейки памяти.

акой

конденсатор имеется в каждом полевом

транзисторе – это паразитная входная

емкость затвор-исток. Таким образом,

один транзистор может выполнять функции

элементарной ячейки памяти.

О

днако

на практике при построении такой ячейки

памяти возникает ряд проблем. Емкость

подзатворного конденсатора у транзистора

с небольшими геометрическими размерами

очень мала, она составляет единицы

пикофарад, а диэлектрик является

неидеальным. Он обладает некоторым,

хотя и очень высоким сопротивлением

утечки, имеющим порядок 109– 1010Ом. Постоянная времени цепочки:

подзатворный конденсатор, область

затвор - исток составляет для маломощных

высокочастотных транзисторов единицы

- десятки миллисекунд, то есть через

небольшое время напряжение на заряженных

конденсаторах уменьшится до уровня

ниже порогового и все ячейки накопителя

перейдут в одно состояние.

днако

на практике при построении такой ячейки

памяти возникает ряд проблем. Емкость

подзатворного конденсатора у транзистора

с небольшими геометрическими размерами

очень мала, она составляет единицы

пикофарад, а диэлектрик является

неидеальным. Он обладает некоторым,

хотя и очень высоким сопротивлением

утечки, имеющим порядок 109– 1010Ом. Постоянная времени цепочки:

подзатворный конденсатор, область

затвор - исток составляет для маломощных

высокочастотных транзисторов единицы

- десятки миллисекунд, то есть через

небольшое время напряжение на заряженных

конденсаторах уменьшится до уровня

ниже порогового и все ячейки накопителя

перейдут в одно состояние.

В реальных транзисторах имеется некоторое сопротивление утечки и между областями сток-затвор, что при наличии напряжения на стоке может приводить к подзаряду разряженных конденсаторов и изменению состояния ячейки

Выход из данной ситуации заключается в том, что кроме режимов записи и считывания, для ячеек такого типа вводится дополнительный режим – регенерации. Его суть в том, что через определенные промежутки, меньшие чем время разряда или заряда конденсаторов до порогового напряжения, производится повторная запись тех же данных, которые в ячейке находились. Если конденсатор был заряжен до напряжения большего чем пороговое он подзаряжается, в противном случае разряжается.

Информация при этом периодически восстанавливается и в итоге она хранится как и в обычном ОЗУ с ячейками статического типа, хотя осуществляется ее периодическая регенерация. Поэтому память с такими ячейками называется динамической.

И

сторически

первыми удалось реализовать не одно, а

трехтранзисторные динамические ячейки,

схема одного из вариантов которой имеет

вид. Ячейка состоит из транзисторовVT1÷VT3 и

запоминающего конденсатора С. Остальные

элементы служат для обеспечения

соответствующих режимов ее работы. Сш– представляет собой емкость разрядной

шины, величина которой много больше

емкости хранения С.

сторически

первыми удалось реализовать не одно, а

трехтранзисторные динамические ячейки,

схема одного из вариантов которой имеет

вид. Ячейка состоит из транзисторовVT1÷VT3 и

запоминающего конденсатора С. Остальные

элементы служат для обеспечения

соответствующих режимов ее работы. Сш– представляет собой емкость разрядной

шины, величина которой много больше

емкости хранения С.

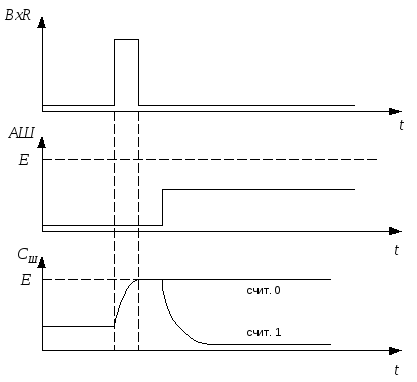

Такая ячейка работает в режимах считывания, записи и хранения (регенерации). Временные диаграммы в первом из них выглядят следующим образом.

Перед

началом этапа считывания на вход R

подается положительный импульс,

открывающий транзистор VT4 через который

происходит заряд конденсатора Сш до

напряжения близкого к нап ряжению

источника питания +Е. Далее на адресную

шину ячейки поступает напряжение

полувыборки под действием которого

транзистор VT3 открывается, а VT1 остается

запертым. Эти транзисторы выполняются

с разными пороговыми напряжениями, у

VT3 оно меньше, чем у VT1. Эквивалентная

схема ячейки при этом имеет вид.

ряжению

источника питания +Е. Далее на адресную

шину ячейки поступает напряжение

полувыборки под действием которого

транзистор VT3 открывается, а VT1 остается

запертым. Эти транзисторы выполняются

с разными пороговыми напряжениями, у

VT3 оно меньше, чем у VT1. Эквивалентная

схема ячейки при этом имеет вид.

Если запоминающий конденсатор С был заряжен до напряжения большего чем пороговое (в ячейке единичное значение бита), то VT2 откроется, конденсатор Сш разрядится через цепочку из открытых транзисторов VT3, VT2 и на выходе усилителя считывания сформируется сигнал логической единицы. В случае, когда С был разряжен, транзистор VT2 на этапе чтения окажется запертым, разряда Сш не произойдет, и на выходе запоминающего устройства появится сигнал логического нуля.

Д

ля

записи в ячейку логической единицы на

разрядную шину должен быть подан сигнал

высокого уровня, а на адресную напряжение

выборки с уровнем порядка +Е. В этом

случае откроются оба транзистораVT1

иVT3, через первый из них

зарядится запоминающий конденсатор.

Для разряда конденсатора (записи нуля)

на шину РШ подается нулевое напряжение,

а на адресную напряжение выборки.

ля

записи в ячейку логической единицы на

разрядную шину должен быть подан сигнал

высокого уровня, а на адресную напряжение

выборки с уровнем порядка +Е. В этом

случае откроются оба транзистораVT1

иVT3, через первый из них

зарядится запоминающий конденсатор.

Для разряда конденсатора (записи нуля)

на шину РШ подается нулевое напряжение,

а на адресную напряжение выборки.

В

ременные

диаграммы работы ячейки и ее эквивалентная

схема в режиме регенерации выглядят

следующим образом. На входRподается сигнал для заряда емкости Сш

, на адресную шину напряжение

полувыборки, а на вход RG,

импульс, открывающий транзисторVT5.

При этом замыкается цепь обратной связи,

так как выходной сигнал поступает во

входную цепь через инвертор (Инв.).

ременные

диаграммы работы ячейки и ее эквивалентная

схема в режиме регенерации выглядят

следующим образом. На входRподается сигнал для заряда емкости Сш

, на адресную шину напряжение

полувыборки, а на вход RG,

импульс, открывающий транзисторVT5.

При этом замыкается цепь обратной связи,

так как выходной сигнал поступает во

входную цепь через инвертор (Инв.).

Его

наличиеприводит к тому, что обратная

связь оказывается положительной. Если

запоминающий конденсатор был заряжен,

то сигнал низкого уровня, формирующийся

РШ при считывании логической единицы,

проинвертируется и в виде высокого

потенциала поступит через сопротивление

канала![]() на заряд конденсатора С. открытого

транзистораVT3. Если он

был не заряжен, то высокий уровень

напряжения на разрядной шине сохранится,

на выходе инвертора появится нулевой

сигнал, который приведет к разряду

запоминающего конденсатора.

на заряд конденсатора С. открытого

транзистораVT3. Если он

был не заряжен, то высокий уровень

напряжения на разрядной шине сохранится,

на выходе инвертора появится нулевой

сигнал, который приведет к разряду

запоминающего конденсатора.

Таким образом, в режиме регенерации заряженные до напряжения больше порогового конденсаторы будут подзаряжаться, а те, у которых напряжение ниже станут разряжаться. Информация в виде наличия или отсутствия заряда запоминающих конденсаторов сохраняется пока этот режим периодически реализуется. В современных вариантах динамических ОЗУ регенерация во всех ячейках строки происходит при обращении к ней и обычно автоматически реализуется в режиме считывания данных.

Рассмотренная ячейка достаточно сложна, но с ними были разработаны первые варианты однокристальных динамических ОЗУ емкостью порядка сотен килобит при средней мощности потребления не превышающей 10 мкВт/бит.

Д альнейшие

работы в области совершенствования

полупроводниковой технологии позволили

реализовать однотранзисторные

динамические запоминающие ячейки, в

которых запоминающий конденсатор

встраивается в цепь истока. Его роль

может выполнять барьерная емкость

запертого перехода исток-подложка.

альнейшие

работы в области совершенствования

полупроводниковой технологии позволили

реализовать однотранзисторные

динамические запоминающие ячейки, в

которых запоминающий конденсатор

встраивается в цепь истока. Его роль

может выполнять барьерная емкость

запертого перехода исток-подложка.

Такая ячейка выбирается подачей сигнала высокого уровня на затвор полевого транзистора. В режиме записи на разрядную шину поступает сигнал низкого, или высокого уровня и запоминающий конденсатор разряжается, либо заряжается.

В режиме считывания на затвор подается сигнал выборки и происходит перераспределение заряда между конденсаторами С и Сш. При этом изменится потенциал шины РШ, что воспринимается усилителем считывания и фиксируется на выходе устройства памяти как логический ноль либо единица. Одновременно осуществляется и регенерация данных.

На основе аналогичных и более совершенных ячеек изготавливаются однокристальные динамические ОЗУ с емкостями в десятки и сотни мегабит. Однако особенности таких ячеек обуславливают и ряд специфических свойств данного вида памяти. На перезаряд запоминающего конденсатора требуется определенное время, кроме того при записи и считывании необходимо предварительно заряжать, либо разряжать и конденсаторы соответствующих шин. Это, а также ряд других причин не позволяют в настоящее время создать ячейки динамические ОЗУ с временами выборки менее десятков нС.

Из-за больших объемов накопителей в таких устройствах используется двухтактный способ адресации, при котором сначала производится выборка строки матрицы запоминающих ячеек, а затем требуемого столбца. Такой подход позволяет резко сократить количество внешних выводов микросхемы ОЗУ и ускоряет процедуру регенерации, осуществляемую для всей cтроки ячеек сразу, однако замедляет доступ к данным.

Работу в режиме чтения обычного динамического ОЗУ, которое называется памятью типа DRAM, можно пояснить временной диаграммой.

Д ля

выбора ячейки накопителя на адресную

шину сначала подается адрес строкиR1

который запоминается в регистре адреса

по спаду сигналаRAS. Затем

на той же шине выставляется адрес столбца

С1, он фиксируется спадом сигналаCAS,

после чего ячейка оказывается выбранной

и через определенное время информацию

из нее можно считать. Данные присутствуют

на выходе ОЗУ, пока сигналCASимеет низкий уровень.

ля

выбора ячейки накопителя на адресную

шину сначала подается адрес строкиR1

который запоминается в регистре адреса

по спаду сигналаRAS. Затем

на той же шине выставляется адрес столбца

С1, он фиксируется спадом сигналаCAS,

после чего ячейка оказывается выбранной

и через определенное время информацию

из нее можно считать. Данные присутствуют

на выходе ОЗУ, пока сигналCASимеет низкий уровень.

Время доступа к данным определяется интервалом от момента активизации сигнала RASдо появления на выходе ОЗУ установившегося значения считываемого бита и для стандартной памяти составляет 30÷50 нС. Для считывания информации из другой ячейки, сигналыRASиCASвозвращают в исходное состояние, и процедура повторяется для нового значения адреса строкиR2 и столбца С2. Интервал между моментами появления данных определяет цикл чтения. Когда сигналCASпринимает единичное значение, выход ОЗУ переходит в высокоимпедансное состояние.

В компьютерах и микропроцессорных устройствах ОЗУ обычно подключается к системной шине процессора FSB(FrontSideBus) и в идеале должно обеспечивать обмен данными со скоростями, определяемыми ее тактовой частотой. Если частота шины 66 МГц, то длительность такта составит около 15 нС и обращение к любой ячейке ОЗУ с временем цикла 70 нС потребует 5 тактов. В этом случае процессор успеет закончить выполнение команды над текущими данными до того, как появится возможность получить новые. Таким образом часть времени процессор будет простаивать. Использование быстродействующие статических ОЗУ большой емкости экономически нецелесообразно из-за их дороговизны, поэтому в качестве оперативной памяти применяется динамическая, но в специальных режимах и с измененной конфигурацией для повышения скорости обмена данными.

В

общем случае, данные необходимые на

последующих этапах обработки могут

располагаться в накопителе произвольным

образом. Это потребует каждый раз при

обращении к памяти задавать свой адрес

строки и столбца. В то же время, если в

ходе записи данные определенным образом

упорядочены, то можно повысить скорость

обмена, используя предположение о

кучности адресов, то есть считая, что

адреса последующих обращений к ОЗУ

вероятнее всего будут расположены в

той же строке рядом с адресом текущей

ячейки. То есть, если процессор получил

из ячейки А1данные

общем случае, данные необходимые на

последующих этапах обработки могут

располагаться в накопителе произвольным

образом. Это потребует каждый раз при

обращении к памяти задавать свой адрес

строки и столбца. В то же время, если в

ходе записи данные определенным образом

упорядочены, то можно повысить скорость

обмена, используя предположение о

кучности адресов, то есть считая, что

адреса последующих обращений к ОЗУ

вероятнее всего будут расположены в

той же строке рядом с адресом текущей

ячейки. То есть, если процессор получил

из ячейки А1данные![]() ,

то последующие будут располагаться в

соседних с нею: А2, А3, А4 и т.д. В большинстве

случаев это можно осуществить, при этом

чем больше длина информационного блока,

тем вероятнее такая ситуация.

,

то последующие будут располагаться в

соседних с нею: А2, А3, А4 и т.д. В большинстве

случаев это можно осуществить, при этом

чем больше длина информационного блока,

тем вероятнее такая ситуация.

Данный подход позволил для стандартных динамических ОЗУ организовать режим быстрого страничного доступа FPM-FastPageMode. Он эффективен, когда после обращения к некоторой ячейке накопителя следующее обращение будет производиться к соседней ячейке, находящейся в той же строке. В этом случае зафиксировав адрес строки, можно поддерживать сигналRASактивным и менять только адреса столбцов, сопровождая их сигналами стробов СAS.

В ременная

диаграмма работы памяти в таком режиме

может быть представлена следующим

образом. Строка в этом случае называется

страницей. Первый цикл чтения при

обращении к произвольной ячейке с

адресом А1 будет занимать столько же

времени (5 тактов), как и в обычном режиме,

но последующие будут короче и потребуют

всего по три такта, так как здесь не

тратится время на фиксацию адресов

строк.

ременная

диаграмма работы памяти в таком режиме

может быть представлена следующим

образом. Строка в этом случае называется

страницей. Первый цикл чтения при

обращении к произвольной ячейке с

адресом А1 будет занимать столько же

времени (5 тактов), как и в обычном режиме,

но последующие будут короче и потребуют

всего по три такта, так как здесь не

тратится время на фиксацию адресов

строк.

Однако информация в этом случае должна передаваться пакетами. Обычно под пакетом понимается блок из четырех соседних бит. Если в обычном режиме пакетный цикл чтения составляет в тактах 5-5-5-5, то в FPM он будет 5-3-3-3 и время цикла внутри страницы уменьшится в среднем с 75 до 50 нС при том же физическом быстродействии ОЗУ.

Дополнительно повысить скорость обмена данными оказалось возможным после разработки модификации ОЗУ, которая получила название EDO DRAM. Память такого типа отличается введением регистра-защелки для выходных данных. Он пропускает сигнал выбранной ячейки на выход при низком уровне строба CAS, а по его подъему фиксирует значение считанного бита до следующего спада. Это позволяет сократить длительность сигнала CAS, так как время, в течение которого данные на выходе ОЗУ будут доступны для чтения, оказывается больше чем в режиме FPM, что видно из соответствующей временной диаграммы. В этом случае адрес следующего столбца можно подавать во время считывания данных с предыдущего.

П

ервый

цикл чтения по длительности практически

не отличается от соответствующих циклов

обычной памяти и занимает 5 тактов, а

последующие потребуют только по два,

при этом пакетный цикл имеет вид 5-2-2-2,

а среднее время доступа при том же

быстродействии ОЗУ составит примерно

40 нС. Здесь основную задержку в процедуру

чтения будет вносить адресный дешифратор

столбцов, так как при смене младших

разрядов адреса могут меняться состояния

большого количества его элементов.

ервый

цикл чтения по длительности практически

не отличается от соответствующих циклов

обычной памяти и занимает 5 тактов, а

последующие потребуют только по два,

при этом пакетный цикл имеет вид 5-2-2-2,

а среднее время доступа при том же

быстродействии ОЗУ составит примерно

40 нС. Здесь основную задержку в процедуру

чтения будет вносить адресный дешифратор

столбцов, так как при смене младших

разрядов адреса могут меняться состояния

большого количества его элементов.

Для уменьшения влияния этого эффекта была предложена структура динамической памяти типа BEDO(BurstEDO- память с расширенным пакетным доступом). У нее при обращении к группе слов (пакету), обычным образом формируется лишь адрес первого столбца, а для выдачи адресов последующих используется быстродействующий счетчик небольшой разрядности, модуль счета которого равен длине пакета.

С труктура

упрощенной системы адресации и временная

диаграмма работы такого типа памяти и

для четырехбитовых пакетов выглядят

следующим образом. Сначала выбирается

столбец С1 и обнуляется счетчик. Затем

с некоторой задержкой начинается его

тактирование фронтами импульсов CAS и

быстрая выборка данных пакета. Далее

устанавливается адрес столбца С5 и

процедура повторяется.

труктура

упрощенной системы адресации и временная

диаграмма работы такого типа памяти и

для четырехбитовых пакетов выглядят

следующим образом. Сначала выбирается

столбец С1 и обнуляется счетчик. Затем

с некоторой задержкой начинается его

тактирование фронтами импульсов CAS и

быстрая выборка данных пакета. Далее

устанавливается адрес столбца С5 и

процедура повторяется.

Задержка чтения первого бита вводится для согласования временных характеристик соответствующих узлов ОЗУ шины FSB. Вследствие этого цикл чтения четырехразрядных пакетов имеет вид 5-1-1-1, что соответствует среднему времени доступа около 30 нС.

Дальнейшее повышение скорости обеспечивается в многобанковых структурах.При этом вся память физически разбивается на блоки, которые называются банками. Если их два, то ячейкам накопителя первого банка присваиваются четные, а второго – нечетные значения адресов. В этом случае при переборе ячеек для считывания или записи обращение к банкам будет происходить поочередно, что приводит к соответствующему выигрышу в быстродействии.

К огда

память не разбита на банки, то сначала

выставляется адрес ячейки

огда

память не разбита на банки, то сначала

выставляется адрес ячейки![]() ,

через некоторое время появляются данные

из нее, которые далее могут быть

зафиксированы в соответствующем

регистре. Следующий адрес

,

через некоторое время появляются данные

из нее, которые далее могут быть

зафиксированы в соответствующем

регистре. Следующий адрес![]() должен подаваться не ранее, чем этот

процесс закончится. Скорость чтения

при этом будет определяться задержками

соответствующих узлов микросхемы

памяти.

должен подаваться не ранее, чем этот

процесс закончится. Скорость чтения

при этом будет определяться задержками

соответствующих узлов микросхемы

памяти.

П ри

разбиении на два банка, образуется два

физических устройства. Скорость выдачи

информации с каждого из них будет такой

же, как и в первом случае. Однако, если

моменты поступления сигналов адресов

в банках сдвинуты во времени на интервал,

соответствующий задержке появления

данных, то информация из четных ячеек

будет появляться в промежутках, когда

данные из нечетных еще выбираются. При

их фиксации на выходе сформируется

поток данных, с частотой следования в

два раза большей, чем в предыдущем

случае.

ри

разбиении на два банка, образуется два

физических устройства. Скорость выдачи

информации с каждого из них будет такой

же, как и в первом случае. Однако, если

моменты поступления сигналов адресов

в банках сдвинуты во времени на интервал,

соответствующий задержке появления

данных, то информация из четных ячеек

будет появляться в промежутках, когда

данные из нечетных еще выбираются. При

их фиксации на выходе сформируется

поток данных, с частотой следования в

два раза большей, чем в предыдущем

случае.

Память BEDORAMдостаточно быстро оказалась вытесненной новой разновидностью – синхронной динамической памятьюSDRAM. В предшествующих вариантах памяти данные на выходе могли появляться в произвольные моменты времени, а считывались процессором по началу следующего такта, что приводило к дополнительным задержкам при обмене.

В синхронной памяти все управляющие сигналы привязаны к тактовой частоте, синхронизированы с нею. Это позволило уменьшить соответствующие задержки, и дало возможность реализовать конвейерный принцип обеспечивающий примерно трехкратный выигрыш в производительности.

П ринципконвейерности можно пояснить следующим

образом. Пусть имеется некоторое

комбинационное устройство УО для

обработки данных, реализующее эту

процедуру за времяτ

и

регистр RG, который фиксирует результат

без задержек. В этом случае следующий

набор данных

ринципконвейерности можно пояснить следующим

образом. Пусть имеется некоторое

комбинационное устройство УО для

обработки данных, реализующее эту

процедуру за времяτ

и

регистр RG, который фиксирует результат

без задержек. В этом случае следующий

набор данных

![]() можно будет подавать, лишь когда

завершится обработка предыдущего

можно будет подавать, лишь когда

завершится обработка предыдущего![]() и фиксация результата в регистре.

Выходные данные начнут появляться через

времяτи с таким же

интервалом.

и фиксация результата в регистре.

Выходные данные начнут появляться через

времяτи с таким же

интервалом.

Если устройство

обработки разбить на два, которые в

совокупности реализуют ту же процедуру,

но обладают в два раза более высоким

быстродействием чем исходное, то

результат частичной обработки каждым

из них можно будет получить с задержкой

![]() .

.

Ч ерез

ерез![]() частично обработанные данные зафиксируются

в регистреRG1 и поступят

на второе устройство обработки. Так как

первое к этому времени уже освободится,

то на него можно будет подавать следующий

блок входных данных

частично обработанные данные зафиксируются

в регистреRG1 и поступят

на второе устройство обработки. Так как

первое к этому времени уже освободится,

то на него можно будет подавать следующий

блок входных данных![]() .

Еще через

.

Еще через![]() на выходе второго регистраRG2

сформируется полностью обработанный

блок данных

на выходе второго регистраRG2

сформируется полностью обработанный

блок данных![]() ,

а на выходе первого появятся прошедшие

частичную обработку данные второго

блока, что позволит начать предварительную

обработку третьего и т. д. При таком

подходе входные и выходные потоки данных

могут следовать с частотой вдвое большей,

чем в предыдущем устройстве, хотя первый

результат появится с той же задержкой.

Здесь реализуется принцип параллельного

функционирования последовательно

активизируемых блоков.

,

а на выходе первого появятся прошедшие

частичную обработку данные второго

блока, что позволит начать предварительную

обработку третьего и т. д. При таком

подходе входные и выходные потоки данных

могут следовать с частотой вдвое большей,

чем в предыдущем устройстве, хотя первый

результат появится с той же задержкой.

Здесь реализуется принцип параллельного

функционирования последовательно

активизируемых блоков.

В динамической памяти DRAMзадержка появления выходных данных определяется суммарными задержками в дешифраторе столбца, усилителе чтения и выходном буфере. Хотя эти устройства являются быстродействующими, но последовательная процедура обработки в такой структуре приводит к тому, что время цикла составляет 60÷70 нС, и уменьшить его достаточно сложно.

И спользуя

трехуровневый конвейер, как это сделано

в памяти типаSDRAM, при том

же быстродействии самих ячеек и других

элементов, частоту выдачи выходных

данных в потоке можно повысить примерно

в три раза, что позволяет запоминающим

устройствам такого типа работать на

частотах системной шины процессора

100, 133 МГц и более.

спользуя

трехуровневый конвейер, как это сделано

в памяти типаSDRAM, при том

же быстродействии самих ячеек и других

элементов, частоту выдачи выходных

данных в потоке можно повысить примерно

в три раза, что позволяет запоминающим

устройствам такого типа работать на

частотах системной шины процессора

100, 133 МГц и более.

В SDRAM, как и у памяти типаBEDOимеется встроенный счетчик столбцов и отношение длительностей циклов первого и последующих обращений также составляет 5-1-1-1, однако время обращения, вследствие конвейерности, получается меньше. В реальных микросхемахSDRAMвозможно регулирование времени запаздывания первого доступа с целью подстройки памяти к частотным требованиям системы.

В синхронной памяти все операции согласованы во времени с процессором, что позволяет дополнительно ускорить процедуры обмена данными. Наиболее распространенные разновидности синхронной памяти обозначались РС100 и РС133. Цифры соответствовали частотам системной шины, на которых такая память функционировала. По структуре, архитектуре, способам управления эти типы памяти идентичны и память, работающая на более высокой частоте способна нормально функционировать и на меньшей.

Одним из важных параметров, которыми характеризуется память является скорость обмена данными, определяемая количеством байт, передаваемых в единицу времени. Современная динамическая память имеет 64-х битную шину, то есть данные передаются блоками по 8 байт. Таким образом, пропускная способность шины РС100 составляет 800 Мбайт/Сек, а для РС133 она имеет значение около 1 Гбайт/Сек. Однако эти показатели реализуются только в случае считывания данных внутри пакета страницы.

Первый цикл обращения в любом случае требует задания адреса строки и столбца и практически для всех рассмотренных типов динамической памяти составляет 50-60 нС. При последующих обращениях в пределах одной страницы это время существенно меньше и составляет порядка 10 нС для РС100 и 7,5 нС для РС133.

Микросхемы памяти SDRAMперед началом цикла чтения, то есть обращением к первой ячейке пакета, должны настраиваться. В ходе настройки в специальных регистрах фиксируются: длина пакетного цикла, порядок счета адресов,CAS-латентность и тип операции с памятью, причем после такта записи в регистр режимов обязательно следует пустой такт.

Длина пакетного цикла - это количество последовательных обращений к ячейкам в пределах одной страницы. Она может быть равной 1,2,4,8 или соответствовать длине полной строки (обычно 256). Порядок счета адресов устанавливается либо последовательный, либо чередующийся. Латентность определяется временем (в тактах) от момента подачи сигнала выбора строки (RAS) до момента, когда на шине данных становится доступным первое слово.

Для синхронной

динамической памяти вводится понятие

тайминга. Оно определяет в тактах

интервалы между моментами подачи сигнала

CASотносительноRAS-![]() ,

время, через которое после выбора столбца

появляются данные -

,

время, через которое после выбора столбца

появляются данные -![]() и время деактивации. Деактивацией

(precharge) называется команда,

которая завершает цикл обращения к

памяти и подается за 2 либо 3 такта перед

выдачей последнего слова данных. Под

ее воздействием перезаряжаются

конденсаторы соответствующих шин и

ячейки подготавливаются к следующему

циклу чтения. ТаймингSDRAMможет принимать значения 2-2-2 или 3-3-3.

и время деактивации. Деактивацией

(precharge) называется команда,

которая завершает цикл обращения к

памяти и подается за 2 либо 3 такта перед

выдачей последнего слова данных. Под

ее воздействием перезаряжаются

конденсаторы соответствующих шин и

ячейки подготавливаются к следующему

циклу чтения. ТаймингSDRAMможет принимать значения 2-2-2 или 3-3-3.

В первом случае латентность равна 4, а для

тайминга 3-3-3 она будет 6, при этом данные

могут быть считаны через пять тактов

после обращения или через 7. Это связано

с тем, что считывание происходит с

появлением положительного фронта

следующего тактирующего импульса.

первом случае латентность равна 4, а для

тайминга 3-3-3 она будет 6, при этом данные

могут быть считаны через пять тактов

после обращения или через 7. Это связано

с тем, что считывание происходит с

появлением положительного фронта

следующего тактирующего импульса.

Временные диаграммы

работы синхронной памяти при считывании

пакетов по четыре элемента из одной

строки имеют вид. По сигналу

![]() фиксируется адрес строки

фиксируется адрес строки![]() ,

затем с задержкой в два такта

,

затем с задержкой в два такта![]() в соответствующий регистр записывается

адрес столбца

в соответствующий регистр записывается

адрес столбца![]() и с задержкой еще в два такта начинают

считываться данные

и с задержкой еще в два такта начинают

считываться данные![]() .За

два такта до окончания этой процедуры

формируется сигнал деактивации

.За

два такта до окончания этой процедуры

формируется сигнал деактивации![]() и цикл повторяется.

и цикл повторяется.

Т айминги

определенным образом связаны с

длительностью пакетных циклов,

определяющих количество тактов для

считывания последовательности из

четырех элементов данных. Для памяти

РС100 типичное значение тайминга 2-2-2, в

этом случае минимальный цикл составит

5-1-1-1, то есть для считывания первых

четырех слов потребуется 8 тактов, что

займет порядка 80 нС. Для РС133 типичным

является тайминг 3-3-3, в этом случае

минимальный цикл 7-1-1-1, и для считывания

такого же блока понадобится 10 тактов

или 75 нС. При меньшей длине пакета память

РС133 может работать медленнее, чем РС100.

айминги

определенным образом связаны с

длительностью пакетных циклов,

определяющих количество тактов для

считывания последовательности из

четырех элементов данных. Для памяти

РС100 типичное значение тайминга 2-2-2, в

этом случае минимальный цикл составит

5-1-1-1, то есть для считывания первых

четырех слов потребуется 8 тактов, что

займет порядка 80 нС. Для РС133 типичным

является тайминг 3-3-3, в этом случае

минимальный цикл 7-1-1-1, и для считывания

такого же блока понадобится 10 тактов

или 75 нС. При меньшей длине пакета память

РС133 может работать медленнее, чем РС100.

Так как времена задержек в цепочке, определяющей тайминг обычно одинаковы, то при маркировке микросхем синхронной памяти часто указывают лишь одну цифру, в частности CL3 соответствует таймингу 3-3-3, аCL2 соответственно 2-2-2.

Память SDRAMимеет структуру, содержащую четыре

независимых банка, что позволяет

совмещать выборку данных из одного с

установкой адреса в другом. Выходной

поток считываемых данных вSDRAMпамяти формируется с частотой системной

шины и они считываются по одному фронту

тактового импульса. В этом случае ядро

памяти (накопитель, а дресные

дешифраторы и усилители записи-считывания)

и выходной буфер работают на частоте

системной шины.

дресные

дешифраторы и усилители записи-считывания)

и выходной буфер работают на частоте

системной шины.

В

более совершенной разновидности

синхронной памятиDDRSDRAMскорость вывода данных увеличена вдвое

при сохранении той же тактовой частоты

ядра, то есть частоты обращения к

накопителю. Они считываются по

положительному и отрицательному фронтам

этого сигнала, что позволяет передавать

данные два раза за такт и вдвое увеличить

пропускную способность памяти.

более совершенной разновидности

синхронной памятиDDRSDRAMскорость вывода данных увеличена вдвое

при сохранении той же тактовой частоты

ядра, то есть частоты обращения к

накопителю. Они считываются по

положительному и отрицательному фронтам

этого сигнала, что позволяет передавать

данные два раза за такт и вдвое увеличить

пропускную способность памяти.

Реально на удвоенной частоте работает лишь узел ввода/вывода, представляющий собой быстродействующий мультиплексор 2→1. За один такт при обращении к накопителю считываются данные сразу из двух ячеек, а далее осуществляется их быстрое переключение на выходную шину . В такой памяти удвоение скорости касается только выдачи данных, а команды воспринимаются как и прежде по положительным фронтам тактовых импульсов системной шины.

DDRпамять, работающую на внутренней частоте 100 МГц обозначают какDDR200, подразумевая при этом, что частота шины данных составляет 200 МГц. Аналогично при работе ядра на частоте 133 МГц используют обозначениеDDR266, а для частоты 200 МГц –DDR400.

Достаточно широко используется и другой подход к обозначению памяти, при котором учитывается пиковая пропускная способность в мегабайтах в секунду. При этом DDR200 представляется какDDRРС1600,DDR266 какDDRРС2100,DDR333 какDDRРС2700 иDDR400 какDDRРС3200.

К ак

иSDRAM, памятьDDRимеет структуру из четырех банков, там

предусмотрен пакетный доступ к данным,

причем длина пакета может составлять

2,4 и 8 элементов. Так как данные вDDRпамяти могут передаваться дважды за

такт, то латентность и тайминг могут

представляться дробными числами, к

примеру 2,5-3-3, 2,5-2-2. Память с меньшей

латентностью является более

быстродействующей, но и более дорогой,

хотя ее преимущество проявляется лишь,

если используется пакетный доступ.

ак

иSDRAM, памятьDDRимеет структуру из четырех банков, там

предусмотрен пакетный доступ к данным,

причем длина пакета может составлять

2,4 и 8 элементов. Так как данные вDDRпамяти могут передаваться дважды за

такт, то латентность и тайминг могут

представляться дробными числами, к

примеру 2,5-3-3, 2,5-2-2. Память с меньшей

латентностью является более

быстродействующей, но и более дорогой,

хотя ее преимущество проявляется лишь,

если используется пакетный доступ.

Дальнейшее

увеличение скорости передачи данных

реализовано в памяти DDRII SDRAM. У нее

данные на выходную шину передаются

четыре раза за такт, хотя само ядро

памяти работает на тех же ч астотах.

Здесь одновременно считываются четыре

элемента данных и мультиплексирование

их на один выход происходит с учетверенной

частотой. Такая память для частоты шины

133МГц обозначается какDDR533,

а работающая с частотой ядра 200МГц –DDR800.

астотах.

Здесь одновременно считываются четыре

элемента данных и мультиплексирование

их на один выход происходит с учетверенной

частотой. Такая память для частоты шины

133МГц обозначается какDDR533,

а работающая с частотой ядра 200МГц –DDR800.

В памяти типа SDRAM напряжение питания ядра составляет 2,5В, в DDRIIоно уменьшено до 1,8В, что позволяет почти вдвое снизить рассеиваемую мощность и соответственно увеличить емкость накопителя, располагаемого на одном кристалле.

В настоящее время ведутся работы по созданию памяти DDRIIIс емкостями накопителя до 4 Гбит, которая будет работать на частоте шины более гигагерца, при напряжении питания ядра 1,2 – 1,5 В. В экспериментальных образцах оно доведено до 0,5В.

При обработке цифровых данных, наибольший интерес представляет не тактовая частота шины, а ее пропускная способность, то есть скорость передачи данных. При частоте 200 МГц и разрядности 8 Байт (64 бита) скорость потока составит 1600 Мбайт/С. Для той же частоты и разрядности 128 бит, скорость будет 3200 Мбайт/С.

Однако техническая реализация увеличения разрядности шин наталкивается на ряд трудностей, одна из которых состоит в том, что чем большее количество сигналов передается одновременно, тем выше окажется уровень помех, что может вызвать неустойчивую работу системы. Кроме того, для технической поддержки такой памяти требуются процессоры и чипсеты, имеющие соответствующую ширину шины данных, то есть 128 бит.

Д

ополнительное

повышение пропускной способности

реализовано в системах с двухканальным

доступом. Здесь используются два

физических модуля памяти, работающих

параллельно и внешний коммутатор,

функционирующий на частоте вдвое

превышающей частоту шины данных. Этот

подход похож на применяемый в памяти

типа DDR SDRAM, однако здесь осуществляется

коммутация внешних данных модулей, а

не внутри них.

ополнительное

повышение пропускной способности

реализовано в системах с двухканальным

доступом. Здесь используются два

физических модуля памяти, работающих

параллельно и внешний коммутатор,

функционирующий на частоте вдвое

превышающей частоту шины данных. Этот

подход похож на применяемый в памяти

типа DDR SDRAM, однако здесь осуществляется

коммутация внешних данных модулей, а

не внутри них.

Идеи пакетной обработки получили свое дальнейшее развитие в памяти типаSLDRAM. Здесь в пакеты группируются не только данные (как в памяти типаEDO), но и адреса.

Еще одной разновидностью быстродействующей динамической памяти является DRDRAM, илиDirectRambusDRAM, в которой применены иные подходы к построению архитектуры подсистемы памяти. Это байт-последовательная память с очень высоким темпом передачи слов. При обмене пакетами по 256 байт средняя частота выдачи данных составляет порядка 400 МГц и более. В такой памяти вместо обычной адресации по комбинированным интерфейсным линиям посылаются пакеты, включающие в себя команды и адреса. Ее особенностью является достаточно большое запаздывание первого доступа к данным. Поэтому она наиболее эффективна при выдаче длинных последовательностей слов, что типично для графических и мультимедийных приложений. Такая память не совместима с другими разновидностями динамических ОЗУ.

Память типа CDRAM(CachedDRAM) содержит на одном кристалле динамическое запоминающее устройство большой емкости и быстродействующую статическую КЭШ память небольшого объема. Разрядность внутренних шин в некоторых образцах достигает 2048, что обеспечивает быстрый обмен большими блоками данных между накопителем динамического ОЗУ и КЭШ памятью. Выходы КЭШ памяти связаны с системной шиной работающей на высокой частоте.