- •Министерство образования и науки Российской федерации

- •1. Последовательностные устройства

- •1.1 Триггера.

- •1.2 Регистры.

- •1.3 Счетчики.

- •2. Делители и синтезаторы частоты

- •2.1 Делители частоты с постоянным коэффициентом деления.

- •2.2 Делители частоты с управляемым коэффициентом деления.

- •2.3 Синтезаторы частоты прямого синтеза.

- •2.4 Синтезаторы с фазовой автоподстройкой частоты.

- •3. Полупроводниковые запоминающие

- •3.1 Классификация и структурная организация запоминающих устройств.

- •3.2 Схемотехника запоминающих ячеек накопителей статических запоминающих устройств.

- •3.3 Принципы работы и методы повышения быстродействия динамической памяти.

- •3.4 Постоянные и перепрограммируемые запоминающие устройства.

- •Лехин Сергей Никифорович

- •Часть 3.

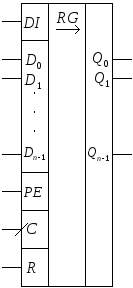

1.2 Регистры.

Регистрами называются последовательностные устройства, используемые для хранения и обработки многоразрядных двоичных слов. Регистры классифицируются по способам ввода-вывода и представления входной и выходной информации.

П араллельные

регистры, обозначаемые на схемах

следующим образом, используются для

оперативного хранения, поступающего

на информационные входы

араллельные

регистры, обозначаемые на схемах

следующим образом, используются для

оперативного хранения, поступающего

на информационные входы![]() многоразрядного слова. В таком регистре

под действием сигнала записи (синхронизации)

разряды входного слова заносятся в

соответствующие ячейки и сохраняются

там. Зафиксированное в разрядах регистра

слово может быть считано с его выходов.

многоразрядного слова. В таком регистре

под действием сигнала записи (синхронизации)

разряды входного слова заносятся в

соответствующие ячейки и сохраняются

там. Зафиксированное в разрядах регистра

слово может быть считано с его выходов.

В последовательном или сдвиговом регистре

обычно имеется один информационный

вход

последовательном или сдвиговом регистре

обычно имеется один информационный

вход![]() и один выход с последнего разряда

и один выход с последнего разряда![]() .

Такой регистр содержит

.

Такой регистр содержит![]() одноразрядных ячеек, соединенных между

собой следующим образом.

одноразрядных ячеек, соединенных между

собой следующим образом.

П од

действием сигнала синхронизации

(тактирования) происходит перемещение

по ячейкам данных поступающих в

последовательном виде на информационный

вход. Через

од

действием сигнала синхронизации

(тактирования) происходит перемещение

по ячейкам данных поступающих в

последовательном виде на информационный

вход. Через![]() тактов бит, пришедший первым может быть

считан с выхода регистра. Затем на выходе

появится второй бит, третий и т.д.

тактов бит, пришедший первым может быть

считан с выхода регистра. Затем на выходе

появится второй бит, третий и т.д.

В таком режиме

данный регистр выполняет функцию

устройства задержки входной импульсной

последовательности на время

![]() ,

где

,

где![]() - период сигналов тактирования. Если

тактирование после заполнения разрядов

регистра прекратить, то последовательно

занесенное входное слово будет храниться

в ячейках регистра до возобновления

подачи сигналов синхронизации.

- период сигналов тактирования. Если

тактирование после заполнения разрядов

регистра прекратить, то последовательно

занесенное входное слово будет храниться

в ячейках регистра до возобновления

подачи сигналов синхронизации.

П араллельно-последовательный

регистр отличается от последовательного

тем, что входное слово под действием

специального сигнала

араллельно-последовательный

регистр отличается от последовательного

тем, что входное слово под действием

специального сигнала![]() (parallelenable)

может быть загружено одновременно во

все ячейки регистра, а далее последовательным

образом (разряд за разрядом) выведено

через его выход

(parallelenable)

может быть загружено одновременно во

все ячейки регистра, а далее последовательным

образом (разряд за разрядом) выведено

через его выход![]() .Такие

регистры используются для преобразования

параллельной формы представления данных

в последовательную.

.Такие

регистры используются для преобразования

параллельной формы представления данных

в последовательную.

П оследовательно-параллельный

регистр выполняет обратную процедуру.

У него имеется один информационный вход

и выводы выходов каждого из разрядов.

Такое устройство осуществляет

преобразование последовательной формы

представления информации в параллельную.

Регистры, выполняющие все вышеперечисленные

функции, относятся к классу универсальных.

оследовательно-параллельный

регистр выполняет обратную процедуру.

У него имеется один информационный вход

и выводы выходов каждого из разрядов.

Такое устройство осуществляет

преобразование последовательной формы

представления информации в параллельную.

Регистры, выполняющие все вышеперечисленные

функции, относятся к классу универсальных.

Их внутренняя

структура представляет собой комбинацию

последовательного и параллельного

регистров. Обычно в таких регистрах

реализуется дополнительная функция

принудительного обнуления всех ячеек,

которая выполняется при подаче

определенного сигнала на вход сброса

![]() .

.

Особую группу

универсальных регистров составляют

реверсивные, позволяющие осуществлять

перемещение данных по разрядам как от

младших к старшим (слева направо), т ак

и наоборот (справа налево). Направление

сдвига определяется значением

соответствующего управляющего сигнала.

Для обозначения таких регистров под

символом

ак

и наоборот (справа налево). Направление

сдвига определяется значением

соответствующего управляющего сигнала.

Для обозначения таких регистров под

символом![]() вводится значок

вводится значок![]() .

.

Внутренняя структура

параллельного регистра представляет

собой набор одноразрядных ячеек памяти

с общим сигналом фиксации данных. В

качестве таких ячеек обычно используются

![]() триггера, синхронизируемые фронтом,

либо потенциалом. В последнем случае

регистр относится к классу защелок.

Структура варианта четырехразрядного

параллельного регистра-защелки имеет

следующий вид.

триггера, синхронизируемые фронтом,

либо потенциалом. В последнем случае

регистр относится к классу защелок.

Структура варианта четырехразрядного

параллельного регистра-защелки имеет

следующий вид.

В последовательном регистре могут

использоваться как

последовательном регистре могут

использоваться как![]() ,

так

,

так![]() и

и![]() триггера, синхронизируемые фронтом и

соединенные следующим образом.

триггера, синхронизируемые фронтом и

соединенные следующим образом.

Построить

такой регистр на триггерах защелках

невозможно, так как при наличии потенциала,

при котором триггер воспринимает входной

сигнал (становится прозрачным), все его

Построить

такой регистр на триггерах защелках

невозможно, так как при наличии потенциала,

при котором триггер воспринимает входной

сигнал (становится прозрачным), все его

разряды

установятся в состояние соответствующее

значению входного бита. Если в схеме

имеются выводы от выходов всех триггеров,

то данный регистр будет выполнять

функции последовательно-параллельного.

Работа последовательного регистра

может быть описана выражением

разряды

установятся в состояние соответствующее

значению входного бита. Если в схеме

имеются выводы от выходов всех триггеров,

то данный регистр будет выполнять

функции последовательно-параллельного.

Работа последовательного регистра

может быть описана выражением![]() ,

где

,

где![]() текущий момент времени,

текущий момент времени,![]() - разрядность регистра, либо

- разрядность регистра, либо![]() .

.

В ременные

функционирования и таблица состояний

четырехразрядного последовательно-параллельного

регистра, при записи набора бит

1-1-0-0-1-1-1-1, выглядят следующим образом.

Из них видно, что форма и структура

сигналов на каждом выходе регистра

повторяет соответствующие параметры

входного, причем сигналы на выходах

регистра сдвинуты во времени друг

относительно друга на период тактирующей

последовательности. В случае, когда

моменты поступления импульсов тактирования

не совпадают с фронтами входного сигнала,

длительности интервалов на выходах

регистра будут отличаться от соответствующих

у входной последовательности.

ременные

функционирования и таблица состояний

четырехразрядного последовательно-параллельного

регистра, при записи набора бит

1-1-0-0-1-1-1-1, выглядят следующим образом.

Из них видно, что форма и структура

сигналов на каждом выходе регистра

повторяет соответствующие параметры

входного, причем сигналы на выходах

регистра сдвинуты во времени друг

относительно друга на период тактирующей

последовательности. В случае, когда

моменты поступления импульсов тактирования

не совпадают с фронтами входного сигнала,

длительности интервалов на выходах

регистра будут отличаться от соответствующих

у входной последовательности.

Если первый

единичный бит, поступающий на вход

регистра условно пометить звездочкой,

то он появится на его последнем выходе

с задержкой на четыре такта. В

![]() разрядном регистре эта задержка будет

составлять

разрядном регистре эта задержка будет

составлять![]() периодов тактирования. Последовательные

регистры такого типа часто называются

стеками типа

периодов тактирования. Последовательные

регистры такого типа часто называются

стеками типа![]() (firstinput–firstoutput, что

означает – первый на входе – первый на

выходе).

(firstinput–firstoutput, что

означает – первый на входе – первый на

выходе).

Через четыре такта последовательно поступивший блок из четырех бит распределится по разрядам регистра и может быть в параллельной форме считан с его выходов. Это позволяет использовать данный регистр для преобразования последовательной формы представления входных данных в параллельную.

Д ля

построения параллельно-последовательного

регистра необходимо, сохранив структуру

межразрядных связей последовательного,

обеспечить возможность принудительной

установки его ячеек в произвольные

состояния. С этой целью в регистрах

такой структуры используются

комбинированные триггера, способные

функционировать как

ля

построения параллельно-последовательного

регистра необходимо, сохранив структуру

межразрядных связей последовательного,

обеспечить возможность принудительной

установки его ячеек в произвольные

состояния. С этой целью в регистрах

такой структуры используются

комбинированные триггера, способные

функционировать как![]() и

и![]() ,

,![]() и

и![]() и т.п. Один из вариантов

параллельно-последовательного регистра

имеет вид.

и т.п. Один из вариантов

параллельно-последовательного регистра

имеет вид.

Здесь при нулевом

значении сигнала разрешения параллельной

записи

![]() на

на![]() и

и![]() входы всех триггеров поступают логические

нули с выходов элементов 2И. В этом случае

ячейки функционируют, как синхронизируемые

фронтом

входы всех триггеров поступают логические

нули с выходов элементов 2И. В этом случае

ячейки функционируют, как синхронизируемые

фронтом![]() триггера, объединенные в структуру

регистра сдвига. Единичный сигнал,

поступающий на вход нижнего элемента

2И обеспечивает прохождение импульсов

синхронизации на соответствующие входы

триггера, объединенные в структуру

регистра сдвига. Единичный сигнал,

поступающий на вход нижнего элемента

2И обеспечивает прохождение импульсов

синхронизации на соответствующие входы![]() триггеров.

триггеров.

С поступлением на

вход

![]() уровня логической единицы, нижний

элемент 2И блокирует подачу синхросигналов,

а на входы

уровня логической единицы, нижний

элемент 2И блокирует подачу синхросигналов,

а на входы![]() и

и![]() поступают прямые и инверсные значения

бит входных данных.

поступают прямые и инверсные значения

бит входных данных.

В этом случае

ячейки регистра функционируют как

асинхронные

![]() триггера и устанавливаются в состояния,

определяемые данными на соответствующих

информационных входах. Если выходной

сигнал снимается лишь с одного из выходов

регистра, то он может быть использован

для преобразования параллельного кода

в последовательный. При наличии выходов

с каждого из разрядов данный регистр

выполняет функции универсального.

триггера и устанавливаются в состояния,

определяемые данными на соответствующих

информационных входах. Если выходной

сигнал снимается лишь с одного из выходов

регистра, то он может быть использован

для преобразования параллельного кода

в последовательный. При наличии выходов

с каждого из разрядов данный регистр

выполняет функции универсального.

Аналогичные устройства широко используются в системах последовательной передачи данных, структура одной из разновидностей которых имеет вид.

Д о

начала передачи в левый регистр

(передатчик) заносится в параллельном

виде

о

начала передачи в левый регистр

(передатчик) заносится в параллельном

виде![]() разрядное слово, а затем на входы

синхронизации обоих регистров подаются

импульсы тактирования. С приходом

первого импульса сигнал

разрядное слово, а затем на входы

синхронизации обоих регистров подаются

импульсы тактирования. С приходом

первого импульса сигнал![]() с

выхода

с

выхода![]() регистра передатчика запишется в первую

ячейку регистра приемника и появится

на его выходе

регистра передатчика запишется в первую

ячейку регистра приемника и появится

на его выходе![]() .

Одновременно происходит сдвиг слова в

регистре передатчике на один разряд в

сторону старших.

.

Одновременно происходит сдвиг слова в

регистре передатчике на один разряд в

сторону старших.

Следующий импульс,

поступающий в момент времени

![]() вызовет сдвиг данных в обоих регистрах

и занесение в младший разряд регистра

приемника бита

вызовет сдвиг данных в обоих регистрах

и занесение в младший разряд регистра

приемника бита![]() и т. д. Через

и т. д. Через![]() тактов входное слово распределится по

ячейкам регистра приемника и может быть

считано с его выходов. Таким образом,

здесь при передаче слов любой разрядности

понадобится всего две сигнальные линии.

тактов входное слово распределится по

ячейкам регистра приемника и может быть

считано с его выходов. Таким образом,

здесь при передаче слов любой разрядности

понадобится всего две сигнальные линии.

Направление сдвига информации в регистре можно изменить, сохранив местоположение триггеров, но поменяв структуру связей между ними, как показано на рисунке.

Д ля

построения реверсивного регистра

сдвига, необходимо осуществлять

перекоммутацию соединений между входами

и выходами триггеров. Схема такого

устройства будет иметь следующий вид.

ля

построения реверсивного регистра

сдвига, необходимо осуществлять

перекоммутацию соединений между входами

и выходами триггеров. Схема такого

устройства будет иметь следующий вид.

Е сли

все переключатели коммутировать

одновременно, то в нижнем состоянии

переключающего контакта регистр будет

осуществлять сдвиг информации слева

направо, а в верхнем – справа налево.

сли

все переключатели коммутировать

одновременно, то в нижнем состоянии

переключающего контакта регистр будет

осуществлять сдвиг информации слева

направо, а в верхнем – справа налево.

Т ак

как использовать механические контакты

для коммутации цифровых сигналов по

ряду причин нецелесообразно, то для

этой цели могут применяться мультиплексоры

2→1, внутренняя структура которого

ывглядит таким образом.

ак

как использовать механические контакты

для коммутации цифровых сигналов по

ряду причин нецелесообразно, то для

этой цели могут применяться мультиплексоры

2→1, внутренняя структура которого

ывглядит таким образом.

Промышленностью в составе ТТЛ , ТТЛШ и КМОП серий цифровых микросхем выпускается большой ассортимент регистров: К1533ТМ8 – четырехразрядный параллельный регистр с прямыми и инверсными выходами разрядов, К1533ТМ9 – шестиразрядный параллельный регистр, К1533ИР23 – восьмиразрядный параллельный регистр, К555ИР8 восьмиразрядный последовательно-параллельный регистр, К555ИР16 – четырехразрядный универсальный регистр со с двигом вправо и тремя состояниями выходов, К155ИР13 – восьмиразрядный универсальный реверсивный регистр.

Область

применения регистров очень широка.

Параллельные регистры, в частности,

являются составляющим накапливающих

сумматоров. Если обычный сумматор

складывает два числа, то накапливающий

производит суммирование последовательности

чисел,

![]() поступающих друг за другом в определенные

моменты времени.

поступающих друг за другом в определенные

моменты времени.

С

читаяисходное состояние такого устройства

нулевым, его работу можно описать

следующим образом. Данные выражения

могут быть преобразованы к виду, откуда

следует, что для получения текущего

результата, необходимо к предыдущему

значению суммы прибавить поступающее

в данный момент число. В таком устройстве

происходит постепенное накопление

суммы последовательности чисел.

читаяисходное состояние такого устройства

нулевым, его работу можно описать

следующим образом. Данные выражения

могут быть преобразованы к виду, откуда

следует, что для получения текущего

результата, необходимо к предыдущему

значению суммы прибавить поступающее

в данный момент число. В таком устройстве

происходит постепенное накопление

суммы последовательности чисел.

Так как сумматор

является комбинационным устройством,

а предыдущий результат сложения требуется

запоминать, то для этой цели можно

использовать параллельный регистр

соответствующей разрядности и структура

накапливающего сумматора будет иметь

вид. Накопленный результат сохраняется

в регистре, поэтому для начала нового

этапа суммирования его требуется

обнулить, для чего используется вход

сброса

![]() .

.

И з

временных диаграмм работы следует, что

при поступлении на его вход первого

числа

з

временных диаграмм работы следует, что

при поступлении на его вход первого

числа![]() ,

на выходе сумматора появится такой же

результат, а на выходе устройства будет

присутствовать нулевое значение. С

приходом импульса записи результат

сложения зафиксируется в регистре и

одновременно поступит на входы

,

на выходе сумматора появится такой же

результат, а на выходе устройства будет

присутствовать нулевое значение. С

приходом импульса записи результат

сложения зафиксируется в регистре и

одновременно поступит на входы![]() сумматора и на его выходах сформируется

число

сумматора и на его выходах сформируется

число![]() .

.

С приходом второго

числа

![]() ,

сумматор сформирует результат, равный

,

сумматор сформирует результат, равный![]() ,

который зафиксируется в регистре и

поступит на выход накапливающего

сумматора в момент поступления очередного

импульса записи.

,

который зафиксируется в регистре и

поступит на выход накапливающего

сумматора в момент поступления очередного

импульса записи.

Такие устройства

находят широкое применение в системах

обработки цифровой информации, они, в

частности, используются в качестве

цифровых интеграторов. Известно, что

определенный интеграл равен площади

под кривой, представляющей собой график

подынтегральной функции. Если эту кривую

разбить на небольшие участки длительностью

![]() и каждому из них поставить в соответствие

число

и каждому из них поставить в соответствие

число![]() равное его площади, то площадь под всей

кривой будет равна сумме площадей таких

участков. Таким образом,

равное его площади, то площадь под всей

кривой будет равна сумме площадей таких

участков. Таким образом,![]() .

.

Т ак

как сигнал меняется во времени, то числа,

соответствующие площадям участков,

будут появляться последовательно друг

за другом и при их суммировании

сформируется текущее значение

определенного интеграла от функции,

представляющей сигнал

ак

как сигнал меняется во времени, то числа,

соответствующие площадям участков,

будут появляться последовательно друг

за другом и при их суммировании

сформируется текущее значение

определенного интеграла от функции,

представляющей сигнал![]() .

Если длительность промежутка принять

равной единице, то при малой его величине,

площадь участка с большой степенью

точности будет равна высоте соответствующего

прямоугольника, то есть мгновенному

значению сигнала.

.

Если длительность промежутка принять

равной единице, то при малой его величине,

площадь участка с большой степенью

точности будет равна высоте соответствующего

прямоугольника, то есть мгновенному

значению сигнала.

П оследовательный

регистр представляет собой систему с

внутренними обратными связями,

реализованными в триггерах. При соединении

его информационного входа со схемой,

определенным образом обрабатывающей

сигналы с выходов, образуется система

с внешней цепью обратной связи, результат

воздействия которой проявится лишь в

следующем такте работы. Такая обратная

связь носит запаздывающий характер.

оследовательный

регистр представляет собой систему с

внутренними обратными связями,

реализованными в триггерах. При соединении

его информационного входа со схемой,

определенным образом обрабатывающей

сигналы с выходов, образуется система

с внешней цепью обратной связи, результат

воздействия которой проявится лишь в

следующем такте работы. Такая обратная

связь носит запаздывающий характер.

Состояние регистра,

определяемое комбинацией сигналов на

всех его выходах зависит, от набора

последовательно заносимых входных

данных. То есть

![]() .

При наличии цепи внешней обратной связи

.

При наличии цепи внешней обратной связи![]() .

Так как сигнал в текущий (

.

Так как сигнал в текущий (![]() -тый)

момент времени на любом из выходов

регистра со сдвигом вправо определяется

предшествующим состоянием предыдущего

разряда (

-тый)

момент времени на любом из выходов

регистра со сдвигом вправо определяется

предшествующим состоянием предыдущего

разряда (![]() ),

то

),

то![]() .

В этом случае на значение входного

сигнала, а следовательно и на текущее

состояние любого из выходов системы

влияет вся предыстория ее работы за

.

В этом случае на значение входного

сигнала, а следовательно и на текущее

состояние любого из выходов системы

влияет вся предыстория ее работы за![]() шагов.

шагов.

Такие устройства обладают рядом специфических особенностей, одна из которых заключается в том, что их состояния циклически повторяются через определенное количество входных импульсов.

Простейшим вариантом

регистра с внешней обратной связью

является схема, в которой сигнал с

последнего выхода подается на его

информационный вход без изменений. Для

четырехразрядного варианта регистра

формула, описывающая состояние

информационного входа системы выглядит

следующим образом

![]() .

.

Если в младший

разряд регистра был записан единичный

сигнал, то под воздействием тактирующих

импульсов, следующих с частотой

![]() ,

он начнет перемещаться по разрядам.

Когда логическая единица появится на

последнем выходе регистра и на его

входе, то следующим положительным

фронтом тактирующего сигнала она

запишется в первый разряд, и далее

процессы будут циклически повторяться.

,

он начнет перемещаться по разрядам.

Когда логическая единица появится на

последнем выходе регистра и на его

входе, то следующим положительным

фронтом тактирующего сигнала она

запишется в первый разряд, и далее

процессы будут циклически повторяться.

В процессе работы на каждом из выходов

регистра формируются сдвинутые друг

относительно друга на интервал времени

процессе работы на каждом из выходов

регистра формируются сдвинутые друг

относительно друга на интервал времени![]() идентичные импульсные последовательности.

Их период

идентичные импульсные последовательности.

Их период![]() ,

а частота повторения импульсов в такое

же число раз меньше. При использовании

в аналогичной схеме

,

а частота повторения импульсов в такое

же число раз меньше. При использовании

в аналогичной схеме![]() разрядного регистра

разрядного регистра![]() ,

а

,

а![]() .

Таким образом данное устройство может

быть использовано в качестве делителя

частоты в

.

Таким образом данное устройство может

быть использовано в качестве делителя

частоты в![]() раз.

раз.

Если единичные сигналы предварительно занесены в несколько разрядов регистра, к примеру нулевой и второй, то по его выходам будет распределяться комбинация 1 0 1 0. Отличие временных диаграмм работы системы в данной ситуации показано штриховыми линиями.

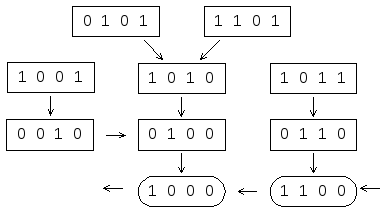

Р аботу

такого и аналогичных устройств можно

описать, используя графы переходов. Для

ситуации, с одним единичным сигналом,

он выглядит следующим образом. Переход

из одного состояния в другое осуществляется

под действием тактирующего импульса.

Так как состояния периодически

повторяются, то граф переходов оказывается

замкнутым, что характерно для всех

циклически работающих систем. Число

узлов графа равно количеству устойчивых

состояний, которые сохраняются в

отсутствии внешних воздействий.

аботу

такого и аналогичных устройств можно

описать, используя графы переходов. Для

ситуации, с одним единичным сигналом,

он выглядит следующим образом. Переход

из одного состояния в другое осуществляется

под действием тактирующего импульса.

Так как состояния периодически

повторяются, то граф переходов оказывается

замкнутым, что характерно для всех

циклически работающих систем. Число

узлов графа равно количеству устойчивых

состояний, которые сохраняются в

отсутствии внешних воздействий.

П

ри

наличии единиц в нулевом и втором

разрядах, граф переходов будет иметь

вид. Здесь количество различимых и

устойчивых состояний равно двум.

Формально можно считать, что число

состояний в данной ситуации остается

прежним, но некоторые из них совпадают,

то есть неразличимы. При таком подходе

структура графа переходов будет

следующей.

ри

наличии единиц в нулевом и втором

разрядах, граф переходов будет иметь

вид. Здесь количество различимых и

устойчивых состояний равно двум.

Формально можно считать, что число

состояний в данной ситуации остается

прежним, но некоторые из них совпадают,

то есть неразличимы. При таком подходе

структура графа переходов будет

следующей.

Р![]() ассмотренное

устройство может иметь и одно устойчивое

состояние, когда во все разряды регистра

занесены нули или единицы. Граф переходов

в этом случае имеет вид, что соответствует

зацикливанию системы.

ассмотренное

устройство может иметь и одно устойчивое

состояние, когда во все разряды регистра

занесены нули или единицы. Граф переходов

в этом случае имеет вид, что соответствует

зацикливанию системы.

Регистр с обратной связью, функционирующий в соответствии с первым вариантом графа переходов называется распределителем импульсов или кольцевым счетчиком. Это связано с тем, что в процессе работы единичный сигнал последовательно появляется (распределяется) на всех разрядах (выходах) устройства. Второе название отражает возможность определения (подсчета) по состоянию выходов устройства числа входных воздействий, поступивших на его вход.

И з

таблицы отражающей зависимость комбинации

сигналов на выходах регистра от количества

импульсов, поступивших на вход

синхронизации следует, что в

отсутствии входных сигналов (когда их

количество равно нулю), логическая

единица формируется на выходе с номером

ноль. После прохождения одного импульса,

единичный сигнал появляется на первом

выходе и т. д. То есть, определив, на каком

выходе регистра присутствует единичный

сигнал, можно сделать вывод о количестве

входных воздействий (тактирующих

импульсов) поступивших к моменту

наблюдения.

з

таблицы отражающей зависимость комбинации

сигналов на выходах регистра от количества

импульсов, поступивших на вход

синхронизации следует, что в

отсутствии входных сигналов (когда их

количество равно нулю), логическая

единица формируется на выходе с номером

ноль. После прохождения одного импульса,

единичный сигнал появляется на первом

выходе и т. д. То есть, определив, на каком

выходе регистра присутствует единичный

сигнал, можно сделать вывод о количестве

входных воздействий (тактирующих

импульсов) поступивших к моменту

наблюдения.

Однако, если их число превысит четыре, то состояния системы начнут повторяться, то есть она не позволяет получить однозначную оценку. В общем случае определяемое по виду кодовой комбинации число соответствует остатку от деления количества входных воздействий на количество различимых рабочих состояний.

Р абота

любых реальных цифровых систем происходит

в условиях воздействия помех, и, кроме

того, они сами являются их источниками.

Это может привести к тому, что в процессе

переключения распределителя импульсов

состояние одного или нескольких разрядов

изменятся не в соответствии с требуемым

алгоритмом работы. Произойдет сбой

системы и в ряде ситуаций она не вернется

в рабочее состояние, что можно пояснить

с помощью следующего графа переходов,

где в прямоугольные контура заключены

сбойные (нерабочие для распределителя)

комбинации.

абота

любых реальных цифровых систем происходит

в условиях воздействия помех, и, кроме

того, они сами являются их источниками.

Это может привести к тому, что в процессе

переключения распределителя импульсов

состояние одного или нескольких разрядов

изменятся не в соответствии с требуемым

алгоритмом работы. Произойдет сбой

системы и в ряде ситуаций она не вернется

в рабочее состояние, что можно пояснить

с помощью следующего графа переходов,

где в прямоугольные контура заключены

сбойные (нерабочие для распределителя)

комбинации.

Логическая причина возникновения сбоев заключается в том, что в рассматриваемом устройстве количество рабочих состояний меньше числа возможных. В системе из четырех триггеров может быть 16 комбинаций их состояний, а рабочими для распределителя являются лишь четыре. Поэтому существует определенная вероятность перехода устройства в одно из возможных, но нерабочих состояний.

Е сли

требуется реализовать систему,

функционирующую по заданному алгоритму

без сбоев, то необходимо обеспечить

условия, при которых система восстанавливала

бы свою работоспособность. Существует

несколько подходов к созданию

помехоустойчивых последовательностных

устройств. Один из них заключается в

анализе состояний системы и принудительном

возврате ее в рабочее при обнаружении

сбоя.

сли

требуется реализовать систему,

функционирующую по заданному алгоритму

без сбоев, то необходимо обеспечить

условия, при которых система восстанавливала

бы свою работоспособность. Существует

несколько подходов к созданию

помехоустойчивых последовательностных

устройств. Один из них заключается в

анализе состояний системы и принудительном

возврате ее в рабочее при обнаружении

сбоя.

Применительно к

кольцевому счетчику это можно сделать

используя параллельно-последовательный

регистр и анализатор

![]() ,

формирующий нулевой сигнал при правильной

работе распределителя импульсов и

единичный в случае возникновения сбоя.

,

формирующий нулевой сигнал при правильной

работе распределителя импульсов и

единичный в случае возникновения сбоя.

Этот сигнал, поступив на вход разрешения параллельной установки, вызовет запись в разряды регистра поданной на его информационные входы рабочей комбинации (к примеру, 1-0-0-0) и восстановление функционировании системы как распределителя импульсов. Анализатор представляет собой комбинационную схему, состояния выходов которой задаются следующей таблицей. Рабочие состояния распределителя импульсов в ней заключены в контура.

С

амовосстановление

такой схемы происходит либо сразу же

после возникновения сбоя, либо в следующем

такте, если процедура параллельной

записи реализуется с приходом сигнала

тактирования. Полный граф переходов

кольцевого счетчика свободного от сбоев

имеет вид.

амовосстановление

такой схемы происходит либо сразу же

после возникновения сбоя, либо в следующем

такте, если процедура параллельной

записи реализуется с приходом сигнала

тактирования. Полный граф переходов

кольцевого счетчика свободного от сбоев

имеет вид.

Второй подход к

построению схем с самовосстановлением

заключается в изменении способа

формирования сигналов на информационном

входе регистра сдвига. Как следует из

таблицы, описывающей работу распределителя

импульсов и из самой его структуры, в

данной схеме

![]() .

При этом сигнал на информационном входе

никак не зависит от состояний остальных

разрядов регистра, что и приводит к

возможности возникновения сбоев.

.

При этом сигнал на информационном входе

никак не зависит от состояний остальных

разрядов регистра, что и приводит к

возможности возникновения сбоев.

Д ля

их устранения необходимо формировать

сигнал

ля

их устранения необходимо формировать

сигнал![]() ,

как функцию, значения которой определяются

всеми выходными сигналами регистра, то

есть для четырехразрядного варианта в

виде

,

как функцию, значения которой определяются

всеми выходными сигналами регистра, то

есть для четырехразрядного варианта в

виде![]() .

Кроме того, от такой функции требуется

выполнении двух дополнительных условий

- при нулевых значениях аргументов она

должна обращаться в единицу, а при

единичных в ноль.

.

Кроме того, от такой функции требуется

выполнении двух дополнительных условий

- при нулевых значениях аргументов она

должна обращаться в единицу, а при

единичных в ноль.

Из приведенной

выше таблицы, следует, что

![]() .

Однако функция такого вида при нулевых

сигналах разрядов регистра также

становится равной нулю. В этом случае

возможно зацикливание распределителя

в состоянии все нули.

.

Однако функция такого вида при нулевых

сигналах разрядов регистра также

становится равной нулю. В этом случае

возможно зацикливание распределителя

в состоянии все нули.

Для того, чтобы

функция удовлетворяла дополнительным

требованиям, в ее состав необходимо

ввести компоненту, которая при нулевых

значениях

![]() обращала бы ее в единицу, а на остальных

наборах сигналов не влияла на значения,

определяемые соотношением

обращала бы ее в единицу, а на остальных

наборах сигналов не влияла на значения,

определяемые соотношением![]() .

Такая компонента представляет собой

конъюнкцию инверсных сигналов с выходов

всех разрядов. При этом выражение для

функции будет иметь вид

.

Такая компонента представляет собой

конъюнкцию инверсных сигналов с выходов

всех разрядов. При этом выражение для

функции будет иметь вид![]() .

Его можно упростить, вынеся за скобки

.

Его можно упростить, вынеся за скобки![]() ,

тогда

,

тогда![]() .

Аналогичное соотношение будет справедливо

и для кольцевых счетчиков любой

разрядности

.

Аналогичное соотношение будет справедливо

и для кольцевых счетчиков любой

разрядности![]() .

.

С хема

кольцевого счетчика с самовосстановлением

имеет вид. Анализ его состояний, начиная

с рабочего 0-0-0-1, показывает, что

последовательность их смены соответствует

рабочему циклу.

хема

кольцевого счетчика с самовосстановлением

имеет вид. Анализ его состояний, начиная

с рабочего 0-0-0-1, показывает, что

последовательность их смены соответствует

рабочему циклу.

П ри

возникновении сбоя 0-0-0-0, на входе

ри

возникновении сбоя 0-0-0-0, на входе![]() сформируется единичный сигнал, который

в следующем такте запишется в младший

разряд регистра сдвига и схема перейдет

в рабочее состояние. Выход из сбоя

0-0-1-1 займет три такта, но в итоге

сформируется единичный сигнал, который

в следующем такте запишется в младший

разряд регистра сдвига и схема перейдет

в рабочее состояние. Выход из сбоя

0-0-1-1 займет три такта, но в итоге схема

начнет функционировать правильно.

Отличие данного метода самовосстановления

от предыдущего состоит в постепенном

выходе схемы из некоторых вариантов

сбоев. Полный граф переходов такого

распределителя импульсов имеет вид.

схема

начнет функционировать правильно.

Отличие данного метода самовосстановления

от предыдущего состоит в постепенном

выходе схемы из некоторых вариантов

сбоев. Полный граф переходов такого

распределителя импульсов имеет вид.

В схемах с самовосстановлением не требуется предварительная установка устройства в какое-либо из рабочих состояний.

В

рассмотренном устройстве

рассмотренном устройстве![]() ,

но с другой стороны, для распределителя

справедливо соотношение

,

но с другой стороны, для распределителя

справедливо соотношение![]() .

Таким образом, сигналы, формируемые на

выходе схемы самовосстановления и

последнем разряде регистра при правильной

работе устройства идентичны. Данное

обстоятельство позволяет реализовать

четырехразрядный распределитель

импульсов на трехразрядном регистре

сдвига, используя в качестве последнего

разряда выход элемента ИЛИ-НЕ, несмотря

на то, что он является комбинационной

схемой, а регистр - последовательностной.

.

Таким образом, сигналы, формируемые на

выходе схемы самовосстановления и

последнем разряде регистра при правильной

работе устройства идентичны. Данное

обстоятельство позволяет реализовать

четырехразрядный распределитель

импульсов на трехразрядном регистре

сдвига, используя в качестве последнего

разряда выход элемента ИЛИ-НЕ, несмотря

на то, что он является комбинационной

схемой, а регистр - последовательностной.

Э то

связано с тем, что среди восьми возможных

состояний системы из трех триггеров

четыре имеют вид, соответствующий

комбинациям нулей и единиц для

распределителя импульсов. При этом

недостающий бит является функцией от

состояний разрядов

то

связано с тем, что среди восьми возможных

состояний системы из трех триггеров

четыре имеют вид, соответствующий

комбинациям нулей и единиц для

распределителя импульсов. При этом

недостающий бит является функцией от

состояний разрядов![]() ,

причем

,

причем![]() .

.

Еще один способ реализации устройств с самовосстановлением заключается в задании полного графа переходов. Если, к примеру, необходимо создать трехразрядный распределитель импульсов, то такой граф может выглядеть следующим образом.

В

соответствии с графом составляется

таблица переходов, которая связывает

состояния разрядов регистра до

переключения системы и после. Наборы

сигналов

соответствии с графом составляется

таблица переходов, которая связывает

состояния разрядов регистра до

переключения системы и после. Наборы

сигналов![]() можно считать функциями от аргументов

можно считать функциями от аргументов![]() и выразить их в алгебраической форме:

и выразить их в алгебраической форме:![]() ,

,![]() .

Для представления

.

Для представления![]() удобно воспользоваться картой Карно и

используя правила минимизации получить

ее представление

удобно воспользоваться картой Карно и

используя правила минимизации получить

ее представление![]() .

.

Т

ак

как функция возбужденияDтриггера имеет вид

ак

как функция возбужденияDтриггера имеет вид![]() ,

то при подаче на информационные входы

триггеров (разрядов) полученных комбинаций

сигналов, устройство будет работать в

соответствии с заданным алгоритмом.

Схема такого трехразрядного распределителя

импульсов с самовосстановлением имеет

вид.

,

то при подаче на информационные входы

триггеров (разрядов) полученных комбинаций

сигналов, устройство будет работать в

соответствии с заданным алгоритмом.

Схема такого трехразрядного распределителя

импульсов с самовосстановлением имеет

вид.

Е сли

проинвертировать сигнал обратной связи

подаваемый с последнего выхода регистра

подать на его информационный вход, то

получится схема, которая называется

счетчиком Джонсона. Граф переходов,

таблица состояний и временные диаграммы

работы четырехразрядного варианта

устройства имеют вид.

сли

проинвертировать сигнал обратной связи

подаваемый с последнего выхода регистра

подать на его информационный вход, то

получится схема, которая называется

счетчиком Джонсона. Граф переходов,

таблица состояний и временные диаграммы

работы четырехразрядного варианта

устройства имеют вид.

У

этого устройства восемь рабочих

состояний, меняющихся так, что сначала

по разрядам регистра пробегает волна

единиц, а затем ее сменяет волна нулей.

Формируемый при этом набор кодовых

комбинаций называется кодом Джонсона

или кодом Либау-Крейга.

этого устройства восемь рабочих

состояний, меняющихся так, что сначала

по разрядам регистра пробегает волна

единиц, а затем ее сменяет волна нулей.

Формируемый при этом набор кодовых

комбинаций называется кодом Джонсона

или кодом Либау-Крейга.

Из временных

диаграмм видно, что на выходах регистра

формируются сдвинутые на один такт

симметричные импульсные последовательности

(меандры) с периодом в восемь раз

превышающим период следования тактирующих

сигналов. Отсюда следует, что счетчик

Джонсона может быть использован в

качестве делителя частоты. Для nразрядной структуры соотношение между

частотами входных и выходных сигналов

имеет вид![]() .

.

Данное устройство также может быть использовано и в качестве счетчика, так как по виду выходной кодовой комбинации можно однозначно определить количество воздействий в пределах от нуля до семи.

В

следствие

того, что число возможных состояний

четырехразрядного регистра 16, а рабочих

у счетчика Джонсона восемь, то в такой

схеме также могут возникать сбои. Если

для реализации счетчика с самовосстановлением

воспользоваться вторым подходом, то из

таблицы функционирования будем иметь

следствие

того, что число возможных состояний

четырехразрядного регистра 16, а рабочих

у счетчика Джонсона восемь, то в такой

схеме также могут возникать сбои. Если

для реализации счетчика с самовосстановлением

воспользоваться вторым подходом, то из

таблицы функционирования будем иметь

П ри

данном способе формирования сигнала

на информационном входе, рабочие

состояния будут самоподдерживающимися,

а процесс выхода из сбоев и полный граф

переходов имеют вид. Максимальная по

длительности процедура самовосстановления

займет три такта.

ри

данном способе формирования сигнала

на информационном входе, рабочие

состояния будут самоподдерживающимися,

а процесс выхода из сбоев и полный граф

переходов имеют вид. Максимальная по

длительности процедура самовосстановления

займет три такта.

О днако

это не единственный вариант формирования

сигнала на входе регистра для построения

счетчика Джонсона с самовосстановлением.

днако

это не единственный вариант формирования

сигнала на входе регистра для построения

счетчика Джонсона с самовосстановлением.

П олучить

представление функции, описывающей

состояние информационного входа в

минимальной форме можно воспользовавшись

картой Карно, которая в соответствии с

таблицей будет иметь следующий вид.

Функция

олучить

представление функции, описывающей

состояние информационного входа в

минимальной форме можно воспользовавшись

картой Карно, которая в соответствии с

таблицей будет иметь следующий вид.

Функция![]() является неполностью определенной, так

как ее значения конкретизированы лишь

на восьми наборах переменных, которые

являются рабочими. Так как остальных

комбинаций выходных сигналов не должно

быть, то значения функции на них могут

быть произвольными.

является неполностью определенной, так

как ее значения конкретизированы лишь

на восьми наборах переменных, которые

являются рабочими. Так как остальных

комбинаций выходных сигналов не должно

быть, то значения функции на них могут

быть произвольными.

Их карты видно,

что нижний контур охватывает все единицы,

отсюда следует, что

![]() и это предельный случай минимизации,

который приводит к исходной ситуации.

Однако на карте Карно можно вводить

дополнительные контура склейки, не

меняющие значений функции, но приводящие

к изменению формы ее представления.

Кроме того, такие контура позволяют в

ряде случаев решить задачу борьбы с

гонками, которые могут нарушить работу

последовательностных устройств.

и это предельный случай минимизации,

который приводит к исходной ситуации.

Однако на карте Карно можно вводить

дополнительные контура склейки, не

меняющие значений функции, но приводящие

к изменению формы ее представления.

Кроме того, такие контура позволяют в

ряде случаев решить задачу борьбы с

гонками, которые могут нарушить работу

последовательностных устройств.

Один из вариантов

введения дополнительных контуров

приведен на карте Карно штриховыми

линиями. При такой их конфигурации,

функция, описывающая сигнал на

информационном входе имеет вид

![]() .

Ее можно преобразовать для устранения

и

.

Ее можно преобразовать для устранения

и нверсий

переменных

нверсий

переменных![]() ,

и схема четырехразрядного счетчика

Джонсона с самовосстановлением будет

выглядеть следующим образом. Самый

длинный путь самовосстановления займет

три такта.

,

и схема четырехразрядного счетчика

Джонсона с самовосстановлением будет

выглядеть следующим образом. Самый

длинный путь самовосстановления займет

три такта.

П

ри

таком подходе структура выражения,

описывающего сигнал на информационном

входе счетчика Джонсона любой разрядности,

окажется аналогичной

ри

таком подходе структура выражения,

описывающего сигнал на информационном

входе счетчика Джонсона любой разрядности,

окажется аналогичной![]() .

.

Использование

иных дополнительных контуров склейки

приведет к тому, что соотношение,

описывающее сигнал

![]() для устройства произвольной разрядности

не будет таким регулярным.

для устройства произвольной разрядности

не будет таким регулярным.

При других вариантах формирующих устройств в цепи обратной связи регистра сдвига система будет формировать последовательности импульсов определенной длины с соответствующими характеристиками.

Для решении ряда задач, связанных с цифровой обработкой данных возникает необходимость в так называемых шумоподобных или случайных сигналах. Они представляют собой наборы кодовых комбинаций, соответствующих числам, следующим друг за другом случайным образом.

Если, к примеру, имеется ряд целых чисел от 0 до 15, то их последовательность 0,1,2,3…..14,15 будет детерминированной, так как здесь прослеживается определенная закономерность, зная которую можно предугадать следующее число. Если же закономерность не просматривается (например для ряда 11,2,5,4,15,1….), то такую последовательность при выполнении некоторых условий относят к классу случайных. Одно из таких условий состоит в том, чтобы заранее было невозможно точно определить, какое из чисел появится на следующем шаге.

Аналогичным образом можно рассмотреть случайные последовательности двоичных символов при этом значительный интерес представляют последовательности в которых вероятность появления 0 или 1 на следующем шаге одинакова и равна 0,5. Для таких последовательностей заранее нельзя предсказать каким будет следующий символ, но в последовательности любой длины количество единиц и нулей одинаково.

Пример детерминированной

двоичной последовательности может

выглядеть следующим образом 0000111100001111

и т.д., а отрезок случайной – 1100010011010110.

Такие последовательности применяются,

в частности в системах шифрации сообщений.

Здесь используется свойство операции

суммирования по модулю два (логической

неравнозначности), заключающееся в том,

что

![]() и

и![]() .

.

Е сли

обработать в элементе логической

неравнозначности цифровую последовательность

сли

обработать в элементе логической

неравнозначности цифровую последовательность![]() ,

содержащую какую-либо информацию и

случайную

,

содержащую какую-либо информацию и

случайную![]() такой же длины, то в итоге получится

поток двоичных символов

такой же длины, то в итоге получится

поток двоичных символов![]() не похожий ни на первую, ни на вторую.

Условно можно считать, что информация,

содержащаяся в сигнале как бы размазывается

по всем символам случайной последовательности.

не похожий ни на первую, ни на вторую.

Условно можно считать, что информация,

содержащаяся в сигнале как бы размазывается

по всем символам случайной последовательности.

Если провести

аналогичную операцию с сигналом

![]() и случайной последовательностью

и случайной последовательностью![]() ,

то восстановится исходный

,

то восстановится исходный![]() ,

а если с исходным, то сформируется

использованная ранее случайная

последовательность, так как

,

а если с исходным, то сформируется

использованная ранее случайная

последовательность, так как![]() ,

а

,

а![]() .

.

Т

Исходная 0000111100001111 Случайная 1100010011010110 Результат

обработки 1100101111011001 Восстановленная 0000111100001111

Случайные последовательности с разными свойствами требуются и в других областях, в частности при моделировании работы систем в условиях помех, решении математических задач методом Монте – Карло и т. п.

Для аппаратного синтеза случайных сигналов применяются так называемые полиноминальные счетчики или генераторы псевдослучайных последовательностей – ГПСП. Они представляют собой регистры сдвига с обратными связями, реализованными через элементы «исключающее ИЛИ» (сумматоры по модулю два). Один из вариантов такого устройства выглядит следующим образом.

П ри

определенном выборе точки подключения

(разряда с номеромn),

система будет генерировать псевдослучайную

последовательность максимальной длины,

или М - последовательность. Ее длина

составит

ри

определенном выборе точки подключения

(разряда с номеромn),

система будет генерировать псевдослучайную

последовательность максимальной длины,

или М - последовательность. Ее длина

составит![]() символов (нулей и единиц), после чего

такая последовательность начнет

генерироваться вновь.

символов (нулей и единиц), после чего

такая последовательность начнет

генерироваться вновь.

Количество символов в ней оказывается на единицу меньше числа возможных состояний регистра, так как состояние разрядов «все нули» является запрещенным. В нем система зацикливается. Поэтому единиц в генерируемой последовательности будет на одну больше, чем нулей.

Сигналы с такими свойствами называются псевдослучайными так как с одной стороны они обладают свойствами случайных сигналов, а с другой – повторяются через определенные интервалы времени. Кроме того, раз существует алгоритм их генерации, то появление в следующем такте нуля или единицы для конкретного ГПСП можно предсказать. Однако, если период повторения последовательности больше интервала наблюдения, то предсказание становится практически невозможным.

Так как в ГПСП используется регистр сдвига, то с каждого из его выходов можно снимать идентичные последовательности, смещенные во времени на один такт. Сложение по модулю два последовательностей, снимаемых с разных выходов регистра, дает псевдослучайную последовательность, идентичную исходной, но сдвинутую во времени на определенное число шагов. При изменении мест подключения сумматоров по модулю два, структура псевдослучайных последовательностей будет меняться.

Если состояния всех выходов регистра сдвига рассматривать как двоичные коды, то можно считать, что в каждом такте будут формироваться случайные числа, с равномерным законом распределения. Для приведенной выше псевдослучайной последовательности эти кодовые комбинации при начальной установке разрядов регистра в единичные состояния, выглядят следующим образом.

И спользуя

методы цифровой, либо аналоговой

фильтрации, из псевдослучайной

последовательности можно сформировать

аналоговые случайные (шумовые) сигналы

с заданными характеристиками.

спользуя

методы цифровой, либо аналоговой

фильтрации, из псевдослучайной

последовательности можно сформировать

аналоговые случайные (шумовые) сигналы

с заданными характеристиками.

Существует множество вариантов построения генераторов псевдослучайных последовательностей с одной и нескольким цепями обратной связи, позволяющих формировать последовательности максимальной длины. Если, к примеру, использовать 33 –х разрядный регистр, то при тактовой частоте 10 МГц, период повторения генерируемой им псевдослучайной последовательности составит около 12 мин., а у ГПСП на 100 разрядном регистре период повторения превысит возраст вселенной.