KonspLektsy

.pdf

Сумматоры групповой структуры.

Различают: с параллельно-последовательным переносом единицы;

споследовательно-параллельным переносом единицы;

спараллельно-параллельным переносом единицы.

Втаких сумматорах вся совокупность разбивается на группы меньшей размерности. Для каждой группы строятся сумматоры, и они объединяются между собой. При параллельной передаче единицы переноса между группами каждой группа снабжается блоком формирования единицы переноса, которая реализуется с помощью уравнений, аналогичных уравнениям для параллельных сумматоров с параллельным переносом.

Pi гр. Gi Hi Pi 1гр. ,

Hi hij hij 1...hi0

где Gi – определяется так же как и Pi – внутри разряда группы.

2.3 Цифровые компараторы

Компараторы (устройства сравнения) определяют отношение между двумя словами. Основными отношениями можно считать отношения на равенство и

на больше. |

|

|

|

|

Пусть имеется |

словo A: аn-1…a1a0 и словo B: bn-1…b1b0. Тогда |

|

|

1, A B |

|

1, A B |

FA B |

|

FA B |

|

|

0, A B |

|

0, A B |

Для отношений неравенства, меньше и строгих неравенств можно записать

F F

F

F

A B FA B A B FB A A B FB A A B FA B

31

Эти отношения используются как логические условия в микропрограммах,

в устройствах контроля и диагностики ЭВМ и т.д.

Устройства сравнения на равенство.

Устройства сравнения на равенство строятся на основе поразрядных операций над одноименными разрядами обоих слов.

Введем признак равенства разрядов

ri ai bi ai bi ai bi

Слова равны, если все их одноименные разряды равны. Тогда признак

|

n 1 |

||

равенства слов: R rn 1 rn 2 ... r1 r0 |

( |

ai bi |

) |

|

i 0 |

||

a0 |

|

|

|

|

M2 |

||

|

|

b0 |

|

|

|

|

|

|

|

F(A B) |

|

|

|

|

|

|

& |

|

|||

|

|

|

|

|

|

||||

am 1 |

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

M2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

||

bm 1 |

|

|

|

|

|

|

|

|

|

Рис. 2.10

A

B

|

0 |

CMP |

|

|

|

||

|

: |

= = |

F(A B) |

|

m-1 |

|

|

|

|

|

|

|

0 |

|

|

|

: |

|

|

|

m-1 |

|

|

|

|

|

|

Устройство сравнения на больше.

Для начала рассмотрим случай, когда слова А и В одноразрядные. Тогда

FA>B определяется согласно таблице |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

A |

B |

FA>B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

|

|

|

|

|

FA B |

A B |

|||||||

|

|

|

|

|

||||

|

0 |

1 |

0 |

|

|

|

||

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

По такому принципу могут сравниваться одноименные разряды многоразрядных чисел. Пусть нужно сравнить два двухразрядных числа:

32

А = а1а0; В = b1b0.

Сначала сравниваются старшие разряды a1 и b1.

Если a1 > b1 , то независимо от младших разрядов FA>B = 1; a1 < b1 , то независимо от младших разрядов FA>B = 0;

если a1 = b1 , то переходят к сравнению младших разрядов.

Далее сравниваются младшие разряды a0 и b0.

Если a0 > b0 , то FA>B = 1;

если a0 ≥ b0 , то FA>B = 0.

Таким образом, для двухразрядных слов можем записать

a1 b1 a 0 b 0 r1 , где r1 – признак равенства старших разрядов.

Тогда для трехразрядных слов:

FA B a2 b2 a1 b1 r2 a0 b0 r2 r1

В общем случае для n-разрядного компаратора:

|

|

|

|

|

|

|

|

|

FA B an 1 bn -1 an -2 bn -2 rn -1 ... |

a0 b0 rn -1 ... |

r1 |

||||||

2.4 Дешифраторы.

Двоичный дешифратор преобразует двоичный код в код “1 из N”

(унитарный код). В кодовой комбинации такого типа только одна позиция занята единицей, все остальные – нулевые.

Двоичный дешифратор вырабатывает единичный сигнал на определенном выходе только в том случае, если на вход поступает код числа,

соответствующий номеру этого выхода.

Рассмотрим принцип построения дешифратора на примере распознавания двухэлементного кода.

В зависимости от входного кода возбуждается одна и только из выходных цепей. Видно, что двоичный дешифратор, имеющий n входов, должен иметь 2n

выходов. Таким образом, двоичный дешифратор реализует на выходе 2n

минтермов.

33

|

|

Входы |

|

|

Выходы |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

y0 |

x1 |

|

x0 |

|||||||

|

|

|

|

|

|

|

|

|

|

||||||

N |

x1 |

|

х0 |

y0 |

y1 |

|

y2 |

y3 |

|

||||||

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

y1 x1 х0 |

||||||

0 |

0 |

|

0 |

1 |

0 |

|

0 |

0 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

|

1 |

0 |

1 |

|

0 |

0 |

|

|

|

|

|

|

|

y2 |

x1 |

|

x0 |

||||||||||||

|

|

|

|

|

|

|

|

|

|

||||||

2 |

1 |

|

0 |

0 |

0 |

|

1 |

0 |

|

||||||

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

x1 |

x0 |

||||

3 |

1 |

|

1 |

0 |

0 |

|

0 |

1 |

y3 |

||||||

|

|

|

|

|

|

|

|

|

|||||||

Если часть входных наборов не используется, то дешифратор называется неполным ( например, дешифратор с 4 входами и 10 выходами).

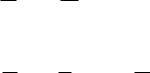

Изобразим схему двоичного дешифратора с инверсными выходами.

Рис. 2.11

Такой дешифратор называется матричным. В нем каждый конъюнктор получает информацию обо всех разрядах входного кода. Достоинство такого дешифратора: дешифрация осуществляется в 1 такт. Недостаток: при большой разрядности входного кода необходимы многовходовые конъюнкторы.

При большой разрядности входного кода применяются пирамидальные дешифраторы. В таких схемах конъюнкции входных переменных образуются

34

постепенно. Время на дешифрацию увеличивается, но используются только двухвходовые конъюнкторы.

Условное обозначение дешифратора (информационные входы обозначают их двоичными весами):

|

x0 |

|

|

1 |

DC |

0 |

|

|

|

y0 |

|

||

|

|

|

|

|

|||||||||

|

x1 |

|

|

2 |

4x16 |

1 |

|

|

|

y1 |

|

||

|

|

|

|

|

|

||||||||

|

x2 |

|

3 |

|

2 |

|

|

|

y2 |

|

|||

|

|

|

|

|

|

||||||||

|

x3 |

|

4 |

|

... |

|

|

|

y15 |

|

|||

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

EN |

|

15 |

|

|

|

Рис. 2.12 |

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EN (Enable) – вход разрешения работы. На этот вход подается стробирующий импульс. Стробирование позволяет вырабатывать выходные сигналы только в определенные интервалы времени.

Различают стробирование по выходу и по входу:

по выходу – вход разрешения вводится параллельно информационным входам последней ступени дешифратора;

по входу – все элементы блокируются через одну из входных цепей.

При нулевом значении сигнала разрешения искусственно формируются нули в цепях прямого и одновременно инверсного значений какой-то одной переменной хi. Поскольку каждая из входных переменных в прямом или инверсном значении поступает на все элементы дешифратора, то все выходы обнуляются.

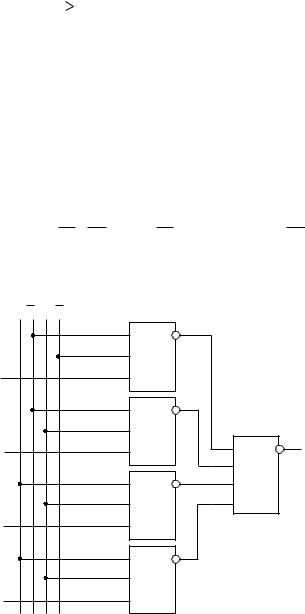

Наращивание размерности дешифратора

Корпуса интегральных схем с большим числом выводов сложны в изготовлении и дороги. С этой точки зрения дешифраторы относятся к крайне неудачным схемам, так как у них при простой внутренней структуре много внешних выводов. Поэтому в сериях интегральных схем не существует дешифраторов с числом информационных входов больше четырех.

Дешифраторы большой разрядности строятся из малоразрядных дешифраторов. Для этого входное слово делится на поля. Разрядность поля

35

младших разрядов определяется числом входов имеющихся дешифраторов.

Оставшееся поле старших разрядов служит для получения сигналов разрешения работы одного из дешифраторов, декодирующих поле младших разрядов.

Пусть требуется дешифратор на 32 выхода. Такой дешифратор должен иметь 5 входов. Пусть число входов имеющихся дешифраторов не больше трех.

Тогда для получения 32 выходов нам понадобиться четере дешифратора 3Х8.

Пятиразрядное входное слово делим на два поля:

х2 х1 х0 – поле младших разрядов;

х4 х3– поле старших разрядов.

Для декодирования поля старших разрядов можно использовать дешифратор с двумя информационными входами (2Х4).

Схема полученного дешифратора показана на рис. 2.12

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x2 x1 x0 |

|

|

|

|

|

|

|||||||

|

|

x3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

DC |

0 |

|

|

|

y0 |

||||

|

|

|

1 |

DC |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

x |

4 |

|

2 |

2x4 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

2 |

3x8 |

1 |

|

|

|

y1 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

y2 |

||

|

|

|

|

|

|

|

|

|

x0 |

2 |

|

|

|

|

|

|

|

|

|

|

|

|

3 |

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

... |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

y7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EN |

|

7 |

|

|

|

|

|

|

|

|

|

|

|

|

EN |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

y8 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

DC |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

3x8 |

1 |

|

|

|

y9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

|

2 |

|

|

y10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

... |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

y15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EN |

|

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

... |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

y24 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

DC |

0 |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

3x8 |

1 |

|

|

y25 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

|

2 |

|

|

y26 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

... |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

y31 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EN |

|

7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Рис. 2.12 Наращивание разрядности дешифратора.

36

Дешифратор как универсальный логический модуль (УЛМ).

Дешифратор совместно со схемами ИЛИ можно использовать для воспроизведения произвольных логический функций. Действительно, на выходе дешифратора вырабатываются минтермы входных переменных, а

логическая функция в СДНФ является дизъюнкцией некоторого числа минтермов.

Например, чтобы получить функцию

y x1 x1 x0 x1 x0 x0 x1 x0 x1 x0 x1 x0 x1 x0 ,

мы должны объединить по ИЛИ 1, 2 и 3 выходы дешифратора.

Такой подход целесообразен при выработке нескольких функций одних и тех же переменных.

2.5 Двоичные и приоритетные шифраторы.

Двоичный шифратор (или кодер) выполняет операцию, обратную дешифрации, т.е. преобразует унитарный код в двоичный.

Имеет 2m – входов; m – выходов; где m – разрядность кода.

x0 |

|

0 |

CD |

1 |

|

|

|

y0 |

|

|

|

||||||||

|

|

|

|

Х |

|

|

|

|

y |

x1 |

1 |

2 |

|

|

|||||

4x16 |

1 |

||||||||

x |

|

|

2 |

|

4 |

|

|

|

y2 |

2 |

|

|

|

||||||

|

|

|

|

||||||

|

|

|

|

|

|

|

|

||

|

|

|

|

|

8 |

|

|

|

y |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

3 |

|||

x |

|

|

15 |

|

|

|

|

|

|

15 |

|

|

|

|

|

Рис. 2.13 |

|||

|

|

|

|

|

|

|

|

|

|

При возбуждении одного из входов на выходе формируется двоичный код номера возбужденного входа. Таблица истинности для 4-х входового шифратора показана на рис. 2.14

x3 |

x2 |

x1 |

x0 |

y1 |

y0 |

|

|

|

|

|

|

|

|

1 |

0 |

0 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

0 |

1 |

0 |

0 |

1 |

1 |

|

|

|

|

|

|

|

|

0 |

0 |

1 |

0 |

0 |

1 |

Рис.2.14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

1 |

0 |

0 |

|

|

|

|

|

|

|

|

37

Приоритетный шифратор выполняет более сложную операцию.

При работе ЭВМ и в других устройствах часто решается задача

определения приоритетного претендента на пользование каким-либо ресурсом. Несколько конкурентов выставляют свои запросы на обслуживание, которые не могут быть удовлетворены одновременно. Нужно выбрать то устройство, которому предоставляется право первоочередного обслуживания.

Простейший вариант решения такой задачи – присвоение каждому

источнику запросов фиксированного приоритета.

Например, группа из восьми запросов R7…R0 формируется так, что высший приоритет имеет источник №7, а далее приоритет уменьшается от номера к номеру. Источник запроса R7 обслуживается первым; если на нем нет запроса, то обслуживается R6 и т.д. Самый младший приоритет у нулевого источника, он будет обслуживаться только при отсутствии запросов с других источников. Таким образом, если одновременно имеются несколько запросов,

то обслуживается источник с наивысшим приоритетом.

Приоритетный шифратор вырабатывает на выходе двоичный код номера

старшего запроса.

Заметим, что при наличии только одного возбужденного входа приоритетный шифратор работает так же, как и двоичный. Поэтому в сериях ИС двоичный шифратор как самостоятельный элемент часто отсутствует.

Режим его работы – частный случай работы приоритетного шифратора.

|

|

|

R0…R3 – запросы на входе шифратора; |

|

|

|

|

а0а1 – разряды выходного кода; |

|

R3 |

HPRI |

a1 |

||

|

||||

R2 |

|

a0 |

EI – сигнал разрешения работы; |

|

R1 |

|

|

|

|

R0 |

|

G |

EO – сигнал, отмечающий отсутствие запросов на |

|

EI |

|

EO |

входах данного шифратора. |

|

|

|

|||

|

|

|

|

G – сигнал, отмечающий наличие запросов на входах

Рис. 2.15 |

данного шифратора. |

|

|

Таблица истинности: |

|

38

|

EI |

|

|

R3 |

|

R2 |

|

|

R1 |

|

|

R0 |

a1 |

a0 |

G |

E0 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

|

|

x |

|

|

x |

|

|

x |

1 |

1 |

1 |

0 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

|

|

1 |

|

|

x |

|

|

x |

1 |

0 |

1 |

0 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

|

|

0 |

|

|

1 |

|

|

|

x |

0 |

1 |

1 |

0 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

|

|

0 |

|

|

0 |

|

|

|

1 |

0 |

0 |

1 |

0 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

0 |

|

|

0 |

|

|

0 |

|

|

|

0 |

0 |

0 |

0 |

1 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

x |

|

x |

|

|

x |

|

|

x |

0 |

0 |

0 |

0 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

Получим выражения для выходных функций: |

|

|

|

||||||||||||||||||

а1 R3 |

|

|

R2 EI R3 |

R2 EI |

|

|

|

|

|

||||||||||||

R3 |

|

|

|

|

|

||||||||||||||||

а0 R3 |

|

|

|

R1 |

EI |

R3 |

|

R1 EI |

|

|

|

|

|||||||||

R3 |

R2 |

R2 |

|

|

|

|

|||||||||||||||

EO R3 R2 R1 R0 EI

G R3 R2 R1 R0 EI

2.6 Мультиплексоры.

Мультиплексор осуществляет подключение одного из входных каналов к выходному под воздействием адресующего слова.

Входы мультиплексора разделяются на информационные и адресные.

Таким образом, мультиплексор – это логическая схема, которая представляет собой коммутатор каналов. Двоичный адрес служит для выбора входа, сигнал c которого должен поступать на выход. Содержит 2m

информационных входов; m адресных входов; один выход. На адресные входы подаются адресные переменные.

39

|

x |

0 |

MUX |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|||||

|

|

4 |

|

|

|

y |

|

|

|

|

|

|

x1 |

|

1 |

|

|

|

|

|

|||

|

|

|

|

a1 |

a0 |

y |

|||||

|

x2 |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||

|

x3 |

|

|

|

|

|

|

0 |

0 |

x0 |

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

a1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

1 |

x1 |

||

|

|

|

|

|

|

|

|||||

|

a0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

Рис.2.16 |

1 |

0 |

x2 |

||

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

1 |

x3 |

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

Работа мультиплексора описывается мультиплексной функцией:

у х0 а1 а0 х1 а1 a0 х2 а1 а0 х3 a1 a0 .

Логическая схема мультиплексора:

a0 |

a0 a1 a1 |

|

|

& |

|

x0 |

|

|

|

& |

|

x1 |

& |

y |

|

& |

|

x2 |

|

|

|

& |

|

x3 |

Рис. 2.17 |

|

|

|

40