- •Разработка и исследование мультимикропроцессорной системы

- •Исходные данные:

- •Ход работы:

- •Определение параметров средней задачи

- •Определение количества вычислительных модулей системы

- •Определение количества накопителей взу

- •Уточнение структурной электрической схемы многопроцессорной системы

- •Разработка модели Маркова вычислительного процесса

- •Расчет характеристик вычислительного блока

Расчет характеристик вычислительного блока

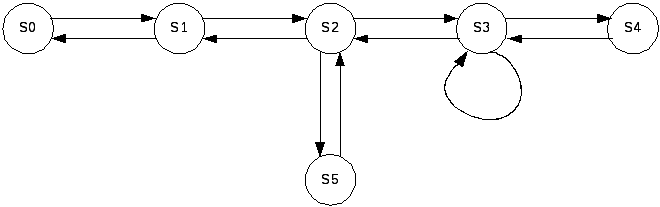

Организации вычислительного процесса в исполнительном вычислительном модуле строится согласно графу Маркова, представленном на рисунке 7.

Рисунок 7

S0: Начальное и конечное состояние – формирование потока команд и данных поступающих и исходящих из БВМ.

S1: Прием запросов ввода-вывода с СШВВ и СШМО в БВМ и обратно; передача запросов на шину БВМ, СШВВ и СШМО.

S2: Передача запросов между процессором, КЭШ-памятью, ОЗУ и КВВ БВМ.

S3: Выполнение вычислительных операций, операций переходов по программе.

S4: Чтение и запись данных и команд, расположенных в КЭШ-памяти.

S5: Чтение и запись данных и команд, расположенных в ОЗУ БВМ.

Вероятности переходов задач в системе для данного графа будут иметь значения, представленные в таблице.

|

|

S0 |

S1 |

S2 |

S3 |

S4 |

S5 |

|

S0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

S1 |

0.5 |

0 |

0.5 |

0 |

0 |

0 |

|

S2 |

0 |

Р21 |

0 |

Р23 |

0 |

Р25 |

|

S3 |

0 |

0 |

Р32 |

Р33 |

Р34 |

0 |

|

S4 |

0 |

0 |

0 |

1 |

0 |

0 |

|

S5 |

0 |

0 |

1 |

0 |

0 |

0 |

Количество переходов от КВВ к ОЗУ через шину определяется средним объемом передаваемых данных, а также разрядностью внутренней шины БВМ и количеством БВМ. При этом стоит учесть, что средний объем данных передается два раза: при считывании файлов, при межмодульном обмене. Пусть разрядность внутренней шины составляет 128 бит, тогда данное количество переходов будет определяться следующим образом:

N15=2*710*1024/(128*850) = 7.4921.

В обратном направлении данные передаются при выдаче результатов и при межмодульном обмене. Т.о. количество переходов будет таким же.

Процент попадания в КЭШ примем равным средней величине – 90%, а долю команд и данных, передаваемых с процессора через КВВ и обратно примем равной 10% от средней трудоемкости задачи. И количество переходов от процессора к процессору будет равно 40% от средней трудоемкости.

Таким образом, вероятности переходов задач будут иметь следующие значения:

Р21=7.5/(15+0.5*0.2*38.2/4)=0.355;

Р23=0.5*0.1*38.2/4/(15+0.5*0.2*38.2/4) =0.009459;

Р25=(7.5+0.5*0.1*38.2/4)/(15+0.5*0.2*38.2/4) =0.636;

Р32=((0.5*0.1+0.1)*38.2/4)/(38.2/4)=0.15;

Р33=(0.4*38.2/4)/(38.2/4)=0.4;

Р34=(0.5*0.9*38.2/4)/(38.2/4)=0.45;

С помощью математической модели системы выше было выяснено, что в вычислительный блок заявки поступают с интенсивностью, равной λсшмо*0.5.

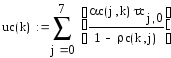

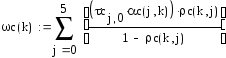

Таким образом, решая аналитическую модель, состоящую из системы уравнений, полученной из матрицы вероятностей переходов и начальной интенсивности λсшмо*0.5, получим значения интенсивностей поступления на каждый блок вычислительного модуля и рассчитаем коэффициенты передачи для каждого модуля как отношение соответствующей интенсивности к начальной. Затем в соответствии и временными задержками на каждом блоке вычислим загрузку блока, время ожидания и время обслуживания:

![]()

![]()

![]()

-

Результаты моделирования

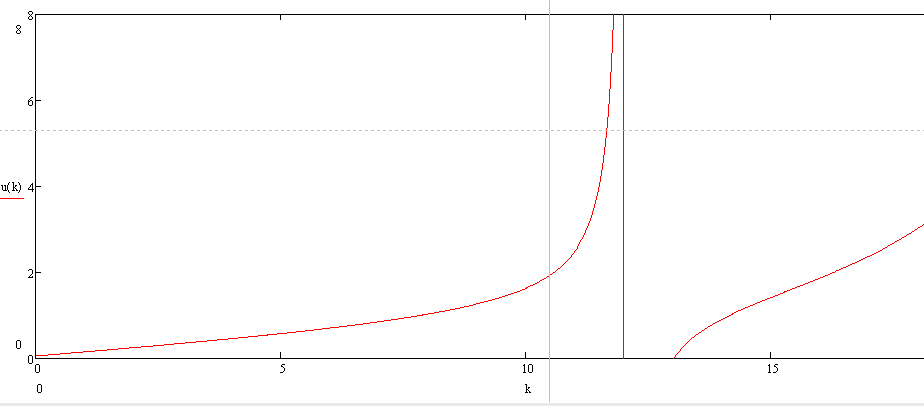

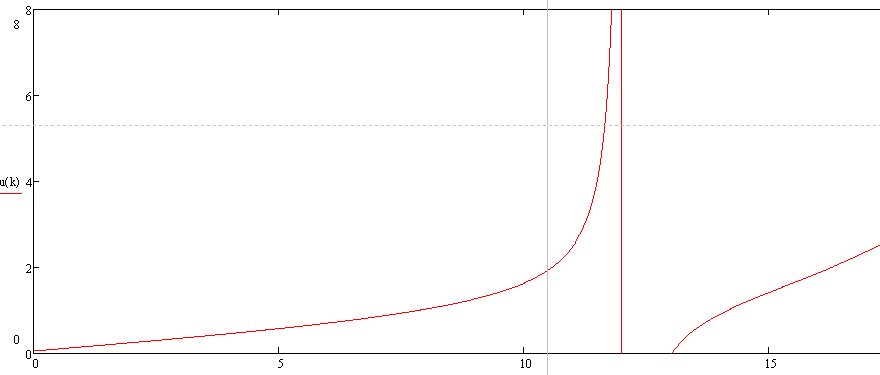

Результаты моделирования представлены графиками зависимостей времени ожидания и пребывания в системе.

Рисунок 1 – Время ожидания задачи в системе

Рисунок 2 – Время пребывания задачи в системе

Вывод:

По результатам расчетов определено, что для успешной работы системы в ее составе необходимо иметь:

-

1453 процессорных блоков с производительностью 0.2 Тфлоп/с ;

-

16 накопителей на МЛ или 73 накопителей на МД;

-

общий объем обрабатываемых файлов составляет 18 Тбайт;

-

общий объем ОЗУ системы составляет 3,12 Тбайт

Для балансировки нагрузки в функциональных узлах системы целесообразно организовать из однотипных накопителей две подсистемы ВЗУ: подсистему ВЗУ на НМЛ и подсистему ВЗУ на НМД.

Таким образом, на графике видна точка разрыва, соответствующая границе стационарного режима для усредненной задачи.

Блок, имеющий наибольшее значение загрузки является узким местом в рассматриваемой системе. В данном случае это процессор.

Достоинствами данной системы являются:

-

Простота архитектуры;

-

Простота масштабирования;

-

Однородная структура модулей всех типов;

-

Высокая надежность, с точки зрения выхода из строя вычислительного модуля.

К недостаткам данной системы относятся:

-

Невысокая масштабируемость, вследствие использования межмодульного обмена;

-

Хорошая степень параллелизма только для ограниченного класса задач;

-

Низкая надежность с точки зрения выхода из строя шины и УВМ;

-

Сложность выгрузки файлов данных, вследствие большого их объема;

Низкая степень сбалансированности системы с точки зрения загрузки отдельных