- •1 Структура, зміст та оформлення проекту

- •Розміри

- •2 Основні теоретичні відомості щодо побудови та режимів роботи мікропроцесорних систем та їхніх основних блоків

- •3 Варіанти завдань

- •Список літератури

- •Міністерство освіти і науки україни

- •Розрахунково-графічна робота

- •За темою: «розроблення мікропроцесорнї системи вводу-виводу аналогових сиґналів»

- •Кременчук 2013

Розміри

Стилі

Формули і рівняння у рукописі (за винятком формул і рівнянь, наведених у додатках) слід нумерувати порядковою нумерацією в межах розділу.

Номер формули або рівняння складається з номера розділу і порядкового номера формули або рівняння, відокремлених крапкою, наприклад, формула (1.3) – третя формула першого розділу.

Номер формули або рівняння зазначають арабськими цифрами на рівні формули або рівняння в дужках у крайньому правому положенні на рядку.

Пояснення позначень величин і числових коефіцієнтів, якщо вони не пояснені раніше у тексті, має бути наведено безпосередньо під формулою з нового рядка з абзацу зі слова «де» без двокрапки у тій послідовності, у якій вони наведені у формулі. Після формули перед словом «де» ставлять кому. Пояснення значення кожного символу та числового коефіцієнта слід давати з нового рядка через крапку з комою.

Якщо необхідно навести числове значення величини, то його записують після розшифрування.

Переносити формули чи рівняння на наступний рядок допускається тільки на знаках виконуваних операцій, повторюючи знак операції на початку наступного рядка. Коли переносять формули чи рівняння на знакові операції множення, застосовують знак «х».

Формули, що йдуть одна за одною й не розділені текстом, відокремлюють комою.

Порядок розміщення джерел у списку використовуваної літератури –за абеткою або хронологією. Кожне джерело має свій порядковий номер, а весь список–єдину наскрізну нумерацію.

Ілюстративний матеріал, таблиці, проміжні математичні доведення, формули і розрахунки, а також текст допоміжного характеру може бути оформлено як додатки.

Додатки є продовженням документа і мають наскрізну нумерацію сторінок, спільну з документом. Кожний додаток має починатися з нової сторінки. Слово “Додаток”пишуть з правого боку рядка малими літерами з першої великої.

Додатки послідовно позначають великими літерами українського алфавіту, за винятком літер Ґ, Є, З, І, Ї, Й, О, Ч, Ь.

Заголовки розділів, підрозділів, пунктів і підпунктів у додатках виконують за загальними правилами.

Ілюстрації, таблиці та формули нумерують у межах кожного додатка. Якщо додаток розділено на розділи, то нумерація ілюстрацій, таблиць, формул має бути також у межах додатка. Якщо у додатку одна таблиця, рисунок чи формула, їх також нумерують.

Переліки, примітки та посилання у тексті додатків оформлюють за загальними правилами.

На всі додатки у тексті документа мають бути посилання.

Креслення оформлюють згідно з вимогами та правилами ЄСКД. Приклад їхнього оформлення наведено в додатку В.

2 Основні теоретичні відомості щодо побудови та режимів роботи мікропроцесорних систем та їхніх основних блоків

Побудова та структура мікропроцесорних систем

Слід пам’ятати, що мікропроцесор (МП) – це програмно-керований пристрій оброблення інформації, виконаний у вигляді однієї або декількох ВІС.

У найзагальнішому вигляді структуру програмованої системи оброблення інформації може бути подано так, як це показано на рис. 1, а. Ядром цієї системи є центральний процесорний пристрій (ЦПП), що призначено для виконання необхідного набору арифметичних і логічних операцій над інформацією, що надходить до його входу. Програма оброблення інформації, що вказує, які саме операції та у якій послідовності потрібно виконувати, зберігається у спеціальному пристрої пам’яті. З виходу ЦПП до споживача надходить оброблена інформація.

Рисунок 2.1 – Схеми, що пояснюють принцип побудови мікропроцесорних систем

Ввід даних до ЦПП може виконуватись як автоматично від деяких пристроїв, що формують відповідні електричні сиґнали (наприклад, від датчиків фізичних величин), так і вручну за допомогою сиґналів, що задаються ззовні. В останньому випадку як пристрій вводу зазвичай використовують клавіатуру, тобто набір кнопкових перемикачів. Вивід інформації також може здійснюватися з розрахунку на сприйняття наступними пристроями автоматичного керування, реєстрації, оброблення тощо, так і розраховуючи на сприйняття цієї інформації оператором. Подання інформації оператору найчастіше здійснюють за допомогою монітора, терміналу або набору цифрових індикаторів.

Під час побудови мікропроцесорних систем отримала поширення магістральна схема зв’язку між блоками. При такій схемі реалізується одна кодова магістраль, до якої приєднуються всі функціональні блоки системи (рис. 2.1,б). У кожний момент часу по магістралі може передаватися тільки одне повідомлення, надіслане одним джерелом і призначене для одного або декількох приймачів. Окремі кодові розряди повідомлення вказують на адресу інформації, тобто визначають, яким саме функціональним блокам її призначено.

Запам’ятовуючий пристрій, що на рис. 2.1,а показано у вигляді одного блока, на рис. 2.1,б подано двома блоками: постійним запам’ятовуючим пристроєм (ПЗП) і оперативним запам’ятовуючим пристроєм (ОЗП). ПЗП слугує для зберігання незмінної частини програми й може працювати тільки в режимі видачі інформації. ОЗП використовується для зберігання проміжних даних і може не тільки приймати на зберігання, але й видавати записану раніше інформацію. У мікропроцесорній техніці прийняті терміни «запис» і «читання» інформації. Процеси читання й запису завжди супроводжують один одного. Наприклад, інформація читається з ОЗП і записується в буферний регістр ЦПП. Для того, щоб не було неоднозначності в описі подібних процесів, прийнято, що всі вони визначаються відповідно до ЦПП як головного діючого об’єкта. Отже, якщо говорять «читання інформації», то це означає, що ЦПП читає інформацію, записану, наприклад, в ОЗП. Відповідно слова «запис коду» означають, що інформація з ЦПП переноситься на зберігання в ОЗП.

Для того, щоб погодити пристрої вводу-виводу інформації з маґістраллю, слугують адаптери вводу-виводу (АВВ) – рис. 2.1,б. У тих випадках, коли розробники системи передбачають для споживача приєднання до маґістралі якихось додаткових функціональних блоків (так званий “відкритий варіант системи”), маґістраль звичайно забезпечується буфером маґістралі (БМ), що збільшує її навантажувальну спроможність, або адаптером магістралі – у тих випадках, коли потрібно не тільки підсилювати за потужністю, але й перетворювати сиґнали.

На рис. 2.1,б показано набір основних функціональних блоків, що входять до мікропроцесорної системи (МПС). Кожний з цих блоків може складатися з однієї або декількох ВІС. Існують також однокристальні мікро-ЕОМ, сконструйовані таким чином, що одна мікросхема містить у тому або іншому вигляді всі блоки, необхідні для побудови МПС. Сукупності ВІС, що мають єдині принципи організації й дозволяють будувати на їхній основі функціонально завершені МПС, називають мікропроцесорними наборами.

Мікропроцесорні набори, сумісні за прийнятими системами команд, рівнями сигналів, принципами передачі сигналів по магістралях, називають мікропроцесорними сімействами. Широко відомі, наприклад, МП-сімейства типів 8080 і 6800. Перше сімейство містить у собі МП-набори типів 8080, 8085, 280, 8088, 8086, 28001, друге – МП-набори типів 6800, 6802, МD46802, 6809, 68000. Вітчизняні аналоги мікропроцесорів 8080, 8085, 8086, 8088 – це МП типів КР580ВМ80, КМ1821ВМ85, КР1810ВМ86, КР1810ВМ88, на основі яких і пропонують розв’язувати завдання, поставлені в даному курсовому проекті.

Найбільш відомим серед вітчизняних є 8-розрядний МП серії К580 – аналог 8080. Значною мірою це, імовірно, пояснюється його доступністю й наявністю детальних описів у технічній літературі. До цієї ж самої групи належать 8-розрядний мікропроцесор типу КР1821ВМ85, 16-розрядні МП КР1810ВМ86 і КР1810ВМ88. Окремі завдання вимірювальної техніки можуть ефективно розв’язувати однокристальні 8-розрядні мікро-ЕОМ серії К1816 (аналог МDS-48) і однокристальна мікро-ЕОМ КМ1813ВЕ1 із убудованими 4-канальним АЦП і 8-канальним ЦАП (аналог 2920 Intel).

Загальні питання побудови МП, їхнього програмування, особливості ввімкнення ВІС МП-наборів описано в літературі [1, 2, 4].

Режими роботи МПС. МПС – це в кінцевому підсумку цифровий автомат, що виконує операції з цифровою інформацією відповідно до програми, яка зберігається в пам’яті. Тому робота за програмою і є основним режимом роботи такої системи.

Розглянемо режими роботи на прикладі МПС, побудованої на основі МП КР580ВМ80. Після початкового запуску (скидання) у програмному лічильнику (регістр РС) установлюється число 0000Н. Буква Н у кінці числа вказує, що число подано в шістнадцятирічному коді. Установлення у стан 0000Н регістра РС приведе до того, що на адресну шину буде видано адресу 0000Н і ЦПП виконає читання байта інформації,що зберігається в комірці пам’яті, розташованій за цією адресою.

Вміст цього байта буде розшифровано в ЦПП як код відповідної операції. Одержавши код операції (КО), ЦПП визначає число байтів, з якого складається повний код команди. У розглянутому мікропроцесорі команди бувають одно-, двох- і трибайтними, причому за змістом коду операції МП однозначно встановлює довжину коду команди. Якщо команда описується двома або трьома байтами, то ЦПП зчитує відсутні один або два байти з наступних комірок пам’яті. Нехай, наприклад, КО, зчитаний з комірки 0000Н, указує на те, що команда трибайтна. Тоді у наступних циклах буде зчитано слова з комірок з номерами 0001Н і 0002Н. Зчитавши утакий спосіб повний код команди, ЦПП її виконує. Далі ЦПП зчитує слово з наступної комірки (за адресою 0003Н) і розшифровує його як код операції. Після цього повторюються ті ж сам дії, що і під час виконання першої команди. Так буде тривати робота із програмою доти, доки не зустрінеться команда переходу. Така команда порушує монотонне наростання числа,яке зберігається у програмному лічильнику РС. Це число змінюється стрибком відповідно до змісту команди переходу, а далі знову код, видаваний на адресну шину, буде збільшуватися на одиницю після кожного зчитування з пам’яті.

Таким чином, однобайтні слова, що зберігаються в пам’яті системи (ПЗП й ОЗП), можуть являти собою як коди операцій, так і восьмирозрядні двійкові числа, що є для процесора простими числовими константами. Зміст самого слова не дозволяє визначити його признаяення. І тільки переглядаючи команди від початку програми, можна встановити, чи є дане слово кодом операції або числом, що являє собою, наприклад, другий або третій байт команди.

У процесі виконання програми МПС може перейти у режим очікування. Справа в тому, що під час роботи із запам’ятовуючим пристроєм або пристроєм вводу-виводу (ПВВ) мікропроцесор має одержати по шині керування сиґнал RDY,що підтверджує готовність цих пристроїв до обміну інформацією з ЦПП. Якщо ж RDY=0, то МПС буде перебувати в режимі очікування. З наступною появою цього сиґналу робота системи відновлюється.

Припинити роботу МПС можна також програмним шляхом за допомогою спеціальної команди зупинення НLТ. Подальша робота після зупинення може бути здійснена шляхом скидання або подачі сиґналу переривання.

Режим переривання – це такий режим роботи МП, у якому за сиґналом від деякого зовнішнього пристрою ініціалізуєтьсявиконання спеціальної підпрограми. Якщо система в момент надходження цього сиґналу працювала за програмою, то спочатку завершуються дії, передбачені поточною командою, а потім виконання основної програми переривається. ЦПП запитує адресу комірки, в якій зберігається КО першої команди підпрограми оброблення переривання. Цю адресу називають вектором переривання. Отримавши вектор переривання, МП далі виконує команди, що зчитуються з області пам’яті, початок якої відповідає вектору переривання. Останньою командою підпрограми оброблення переривання звичайно забезпечується повернення до виконання основної програми. Для того, щоб це виявилося можливим, потрібно, як правило, на початку підпрограми оброблення переривання запам’ятати в стеку стани всіх регістрів ЦПП, а наприкінці підпрограми знову відновити ці стани.

У МПС можуть діяти декілька входів переривання зі своїми векторами, можливе встановлення різних режимів і пріоритетів переривань.

Ще один режим роботи МПС – це режим прямого доступу до пам’яті (ПДП). За звичайних умов під час роботи за програмою обміну інформацією між, наприклад, одним із зовнішніх пристроїв, приєднаних через адаптер вводу-виводу (АВВ), і пристроєм пам’яті (ОЗП або ПЗП) здійснюється через ЦПП. Інформація від джерела спочатку зчитується в ЦПП, а потім з ЦПП переписується до приймача інформації. Якщо мова іде про пересилання великих масивів інформації, то, природно, виникає бажання спростити й прискорити процедуру обміну за рахунок виключення з неї проміжної ланки у вигляді ЦПП. Саме таке пересилання інформації із джерела до приймача і здійснюється в режимі ПДП. При цьому ЦПП відключається від шин даних і адреси: буфери цих шин переходять у високоімпендансний стан. Відбувається так зване “захоплення” шин контролером ПДП – спеціальним модулем, складеним з однієї або декількох спеціальних ВІС. Цей модуль керує роботою шин і організує обмін інформацією в режимі ПДП.

Режим ПДП не часто реалізується в мікропроцесорних пристроях керування та вимірювальних пристроях. Але оскільки МП застосовують у пристроях різного призначення, у тому числі й у мікро-ЕОМ, то входи керування, що дозволяють реалізувати режим ПДП, мають практично всі МП.

Рис. 2.2,а показує схему ввімкнення МП типу КР580ВМ80.

До складу пристрою в цьому випадку, крім самого МП, входять також тактовий ґенератор (DD1) КР580ГФ24, системний контролер (DD3) KP580BK28 і два буферних регістри (DD4, DD5) типу КР580ВА87 або КР580ВА86 (перший з них інвертує сиґнали, другий не інвертує).

Тактовий ґенератор формує позитивні імпульси, що не перекриваються, F1 і F2 амплітудою 12В, які синхронізують роботуМПС. Крім того, у ґенераторі формуються імпульси F2TTL, які збігаються за часом з імпульсами F2, але мають амплітуду,що відповідає ТТЛ-схемам.

Рисунок 2.2 – Схема ввімкнення МП КР580ВМ80 та часові діаграми основних циклів

Ці імпульси за необхідності

можуть використовуватись

для синхронізації роботи зовнішніх

пристроїв. Частота

тактових імпульсів стабілізується

кварцовим резонатором ZQ,

резонансну частоту

якого слід вибирати в 9 разів

більшою за необхідну тактову частоту

![]() процесора. Типове значення

процесора. Типове значення![]() =2МГц,

для чого потрібний кварцовий резонатор

на 18МГц.

=2МГц,

для чого потрібний кварцовий резонатор

на 18МГц.

Разом з

видачею тактових імпульсів тактовий

ґенератор здійснює

формування й синхронізацію деяких

керуючих сиґналів:

скидання (RESIN

– RES),

готовності (RDYIN

– READY),

стробу (SYNC

–

![]() ).

Скидання ЦПП під час

увімкнення живлення

реалізується за допомогою RС-кола

(наприклад,

).

Скидання ЦПП під час

увімкнення живлення

реалізується за допомогою RС-кола

(наприклад,

![]() 1=10кОм,

1=10кОм,

![]() 1=1мкФ),

приєднаного до входу

RESIN.

Надалі скидання може здійснюватися за

допомогою кнопки

SA1.

1=1мкФ),

приєднаного до входу

RESIN.

Надалі скидання може здійснюватися за

допомогою кнопки

SA1.

Вхідний сигнал готовності RDYIN надходить на ґенератор від пристроїв пам’яті або вводу-виводу. Якщо ці пристрої мають достатню швидкодію для того, щоб вчасно реагувати на команди ЦПП, то можна на вхід RDYIN подати постійний сигнал готовності, з’єднавши цей вхід резистором (R2 на рис. 2, а) з джерелом живлення +5В.

Системний контролер SC

виконує роль буфера

шини даних і формує сиґнали

керування для пристроїв

пам’яті та вводу-виводу. Для даного

МП частина сиґналів

керування передається

з ЦПП по шині даних у

режимі розподілу за

часом. Ці сиґнали

керування фіксуються

системним контролером на початку

кожного циклу команди за сиґналом

стробу

![]() .

Крім того, три сигнали

керування: HLDA

(підтвердження переходу в режим ПДП),

DBIN

(перемикання шини даних

на ввід) і

.

Крім того, три сигнали

керування: HLDA

(підтвердження переходу в режим ПДП),

DBIN

(перемикання шини даних

на ввід) і

![]() (запис інформації) – подаються наSC

з ЦПП

безпосередньо по окремих лініях. На

підставі прийнятих сиґналів

системний контролер формує керуючі

сигнали

(запис інформації) – подаються наSC

з ЦПП

безпосередньо по окремих лініях. На

підставі прийнятих сиґналів

системний контролер формує керуючі

сигнали

![]() (підтвердження переривання),

(підтвердження переривання),![]() (читання з комірки пам’яті),

(читання з комірки пам’яті),![]() (читання з пристрою

вводу-виводу),

(читання з пристрою

вводу-виводу),

![]() (запис до комірки пам’яті),

(запис до комірки пам’яті),![]() (запис до пристрою

вводу-виводу).

(запис до пристрою

вводу-виводу).

Як показано на рис. 2.2, а, до шини керування входять також лінії,за якими подають сиґнали від зазначених пристроїв на процесор. Це сиґнал запиту переривання INT, сиґнал запиту на захоплення шин від контролера прямого доступу до пам’яті HOLD, сиґнал готовності пристрою до виконання операції RDYIN.

Крім згаданих, ЦПП формує ще два сиґнали керування, що може бути використано під час побудови МПС. До них належить сиґнал WAIT,який свідчить, що ЦПП перебуває в режимі очікування сиґналу готовності READY, і сиґнал дозволу переривання INTE,що інформує про те, що ЦПП готовий реагувати на сиґнал переривання INT.

Буферні каскади шини адреси RG (рис. 2.2, а) може бути реалізовано не тільки за допомогою мікросхем КР580ВА86/87, але й за допомогою мікросхем серії ТТЛ, наприклад типу К155ЛП10/11, К155ЛН6.

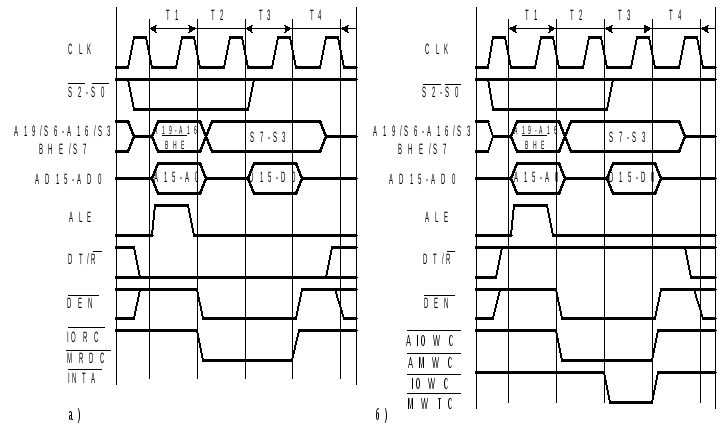

Часові діаграми, що пояснюють основні цикли роботи мікропроцесорної системи, наведено на рис. 2.2, б.

Розглянемо ряд питань,що стосуються

організації вводу-виводу

інформації в даній МП-системі. МП

КР580ВМ80

може адресуватися до 65536 комірок пам’яті,

до 256 пристроїв вводу

та до 256 пристроїв

виводу. Як видно з рис.

2.2, а, шина адреси – спільна

для пристроїв пам’яті

та вводу-виводу. Тому, якщо по цій шині

передається, наприклад, код 0101Н, то це

значить, що ЦПП підготовлює

до роботи комірку пам’яті або пристрій

вводу чи виводу

з такою адресою. Що ж

саме ініціалізується,

визначають сиґнали

керування

![]() ,

,![]() ,

,![]() ,

,![]() .

Якщо, наприклад, із цих сиґналів

тільки

.

Якщо, наприклад, із цих сиґналів

тільки

![]() дорівнює нулю, то це

значить, що буде виконуватися

запис до комірки пам’яті, тобто МП

звертається до блока

ОЗП. Якщо ж нульовий

рівень виставлено на лінії

дорівнює нулю, то це

значить, що буде виконуватися

запис до комірки пам’яті, тобто МП

звертається до блока

ОЗП. Якщо ж нульовий

рівень виставлено на лінії

![]() (на інших трьох лініях – одиниця), це

говорить про те, що МП

буде виконувати читання

із пристрою вводу.

(на інших трьох лініях – одиниця), це

говорить про те, що МП

буде виконувати читання

із пристрою вводу.

Оскільки під час адресації до пристроїв вводу-виводу достатньо тільки одного байта адресного коду, то, звертаючись до таких пристроїв, ЦПП дублює в старшому байті адреси зміст молодшого байта.

Для пристроїв вводу-виводу виділено окремі сигнали керування, тому що в тому випадку, якщо помістити їх на місце певних комірок пам’яті, пристрої має бути оснащено дешифратором двобайтної адреси, тобто дешифратором 16-розрядного двійкового числа. Якщо ж ці пристрої ввімкнені як пристрої вводу-виводу, то досить дешифратора на 8 входів. Більше того, у тих випадках, коли число пристроїв вводу й пристроїв виводу не більше восьми, що найчастіше й буває, можна обійтися взагалі без дешифратора, використовуючи як адреси цих пристроїв однобайтнічисла, що містять тільки по одній одиниці (наприклад, 00000001, 00000010, 00000100 і тощо). Крім того, скорочення адреси під час звертання до пристроїв вводу-виводу робить відповідні команди звертання більш короткими, а наявність окремих команд для звертання до пам’яті й до пристроїв вводу-виводу дозволяє одержувати більш наочні програми.

Мікропроцесор КМ1821ВМ85 (аналог МП 8085) являє собою істотно поліпшений варіант МП типу ВМ80 (аналог МП 8080), виконаний за КМОП-технологією (потужність споживання – менша за 0,1Вт). Для його живлення потрібно тільки одне джерело, у нього підвищена швидкодія як за рахунок збільшення тактової частоти, так і за рахунок більш раціональної організації циклів виконання команд. У цього мікропроцесора молодший байт адреси мультиплексований з шиною даних: використовують ті самі виводи мікросхеми в режимі поділу часу. Це дозволило вивільнити частину виводів мікросхеми для передачі сиґналів керування. Усі сиґнали керування в цьому МП, на відміну від МП ВМ80, передаються без мультиплексування. МП ВМ85 має розвинену систему переривань. У МП є вбудований тактовий ґенератор і передбачено можливість послідовного вводу та виводу інформації. У мінімальній конфіґурації для побудови МПС на основі цього МП потрібно тільки три корпуси ВІС: це ЦПП і ще дві спеціальні ВІС цього комплекту.

Система команд МП ВМ85 містить у собі всі команди ВМ80 і, більш за те, дві додаткові команди керування системою переривань. У цих двох МП ідентичний склад і призначення внутрішніх регістрів, розмір адресного простору, розрядність оброблюваних слів.

Схему ввімкнення та часові діаграми основних циклів роботи МП ВМ85 показано на рис. 2.3. У цьому випадку до складу пристрою входять ЦПП і три мікросхеми буферів шини адреси та шини даних. До виводів X1 і Х2 приєднується кварцовий резонатор,що задає частоту внутрішнього ґенератора. Тактова частота МП (3МГц) утворюється шляхом ділення на два частоти імпульсів цього ґенератора. Для завдання тактової частоти замість кварцового резонатора може бути використано LC- або RС-коло, а також зовнішні синхронізуючі імпульси.

Коло Rl, C1 так само, як і в пристрої за схемою рис. 2.2, а, здійснює скидання МПС у початковий стан під час увімкнення напруги живлення. Сиґнали,наявні на виходах S0 і S1, характеризують стан МП. Наприклад, комбінація цих сиґналів 00 говорить про те, що МП перебуває в режимі зупинення. До виходів МП CLK і RESOUT може бути приєднано входи синхронізації й скидання різних пристроїв МПС. Вхід SID і вихід SOD – відповідно вхід і вихід послідовних даних.

Як видно зі схеми рис. 2.3,

а, старші (А8

– А15)

і молодші

(А0

– А7)

розряди адреси фіксуються

регістрами DD3

і DD4

типу КР580ИР82

або ИР83 за стробуючим

сиґналом ALE.

Буфери шини даних

виконано на мікросхемі DD2

типу КР580ВА86/87.

У цих буферах напрямок

передачі змінюється залежно від

значення сиґналу

на виході

![]() МП. При цьому мікросхеми КР580ИР82

і КР580ВА86

забезпечують підсилення за потужністю

сиґналів без інвертування,

а КР580ИР83

і КР580ВА87

підсилюють та інвертують

сиґнали.

МП. При цьому мікросхеми КР580ИР82

і КР580ВА86

забезпечують підсилення за потужністю

сиґналів без інвертування,

а КР580ИР83

і КР580ВА87

підсилюють та інвертують

сиґнали.

Рисунок 2.3 – Схема ввімкнення

МП КМ1821ВМ85

та часові діаграми основних циклів

Рисунок 2.3 – Схема ввімкнення

МП КМ1821ВМ85

та часові діаграми основних циклів

Керування пристроями

пам’яті та вводу-виводу в даній

МПС здійснюють за

допомогою трьох сиґналів:

![]() (ввід-вивід

або пам’ять),

(ввід-вивід

або пам’ять),![]() (запис) і

(запис) і![]() (читання). Враховуючи, що в системі з МП

типу ВМ80 використовувуються

для аналогічних цілей чотири

сиґнали:

(читання). Враховуючи, що в системі з МП

типу ВМ80 використовувуються

для аналогічних цілей чотири

сиґнали:

![]() ,

,![]() ,

,![]() ,

,![]() ,

одна з цих систем сиґналів

може бути досить просто перетворена

на іншу.

,

одна з цих систем сиґналів

може бути досить просто перетворена

на іншу.

У даному МП є п’ять входів переривань, один з яких (INTR) аналогічний за функціональним призначенням входу INT МП ВМ80. Як було сказановище, після одержання сигналу переривання за цим входом МП вводить з шини даних вектор переривання – команду,що виставляється пристроєм,який запросив переривання. Звичайно це команда RST п, за якою здійснюється перехід програми до команди, код якої зберігається в комірці з адресою 8п (адреса, з якої здійснений перехід, запам’ятовується у стеку). У МП ВМ85 є три входи переривання RST п, сиґнали на які відразу ініціюють перехід до команди,що зберігається в комірці пам’яті з адресою 8п. Таким чином, під час використання цих входів переривання немає необхідності в тому, щоб зовнішній пристрій виставляв на шині даних потрібну команду. Адреси переходів для переривань по входах RST 5.5, RST 6.5, RST 7.5 наступні: 002СН, 0034Н, 003СН. Дані переривання можуть маскуватися (заборонятися) програмним способом командою SIM (установлення маски). Читання маски переривань здійснюється за командою RIM.

Переривання по входу TRAP – це переривання без маскування, за яким здійснюється перехід за адресою 24Н (таким чином, ця команда могла б бути названа RST 4.5). Переривання за цим входом звичайно формуєтьсяпід час аварійної ситуації (наприклад, відключення живлення), тому не передбачено команди, які могли б заборонити його оброблення.

Якщо після надходження сиґналу одного з переривань до початку його оброблення надійдуть також інші сигнали переривань, то МП здійснить перехід,що відповідає старшому за пріоритетом сигналу. Пріоритети при цьому розставлено в такийспосіб (в порядку зменшення): TRAP, RST 7.5, RST 6.5, RST 5.5, INTR. Якщо ж оброблення переривання вже почалося, то воно може перерватися черговим незабороненим сиґналом переривання незалежно від його пріоритету. По входах RST 5.5, RST 6.5 і INTR МП реагує на одиничний рівень сиґналу, по входу RST 7.5 – на позитивний фронт сиґналу (у МП є внутрішній тригер,що спрацьовує по фронту), по входу TRAP – і на одиничний рівень, і на позитивний фронт.

Мікропроцесор КР1810ВМ88 (аналог МП 8088), на відміну від розглянутих вище, є 16-розрядним МП, тобто виконує різні арифметичні, логічні та інші операції над 16-розрядними двійковими числами. Але, разом з тим, він має зовнішню 8-розрядну шину даних. Це дає можливість сполучити розвинену систему команд 16-розрядного МП із простотою реалізації 8-розрядної МПС. Природно, при цьому трохи втрачається швидкодія порівняно з процесом ВМ86,що має 16-розрядну шину даних. При 8-розрядній шині доводиться одне 16-розрядне слово вводити або виводити побайтно за два цикли. Однак для типових застосувань, наприклад, у вимірювальних пристроях, швидкодії такого процесора цілком достатньо. Крім того, МП ВМ88 може оперувати й з однобайтними словами. Його швидкодія під час виконання таких команд істотно вища, ніж у поданих вище МП. Для порівняння, на виконання простих операцій мікропроцесори типів ВМ80, ВМ85, ВМ88 витрачають час відповідно 2; 1,3 і 0,4 мкс [3].

Великою перевагою МП ВМ88 є наявність вбудованого апаратного помножувача, що дозволяє швидко виконувати за відповідними командами операції множення й ділення чисел. Об’єм безпосередньо адресованої пам’яті в цього МП становить 1024 кілобайти. Молодший байт адреси, як і в МП ВМ85, передається по шині даних у режимі поділу часу та стробуєтся сиґналом ALE.

Система команд МП ВМ88 збігається з системою команд МП ВМ86. Значною мірою збігається й внутрішня структура цих МП. Опис їхньої структури й короткий огляд системи команд наведено в [1, 3].

Схему ввімкнення МП ВМ88 показано на рис. 2.4. Цей МП не містить внутрішнього тактового ґенератора, він виконаний у цьому випадку на мікросхемі DD1 типу КР1810ГФ84. ЦПП (DD2) має входи маскованого INTR і немаскованого NMI переривань.

Рисунок 2.4 – Схема ввімкнення МП КР1810ВМ88

Вхід MN/MX дозволяє перебудовувати внутрішню структуру МП із метою його використання в мінімальному або максимальному режимі. В останньому випадку можливості МП розширюються, але необхідне включення в систему спеціального системного контролера, тому частіше використовуютьмінімальний режим.

Як видно зі схеми рис. 2.4,

організація буферів шин даних і адреси

в цьому випадку така ж сама, як і під

час застосування МП ВМ85.

Збігаються й сиґнали

керування пристроями

пам’яті та вводу-виводу. У пристрої

за схемою рис. 2.4 установлено буфери

тільки для двобайтної

адреси пам’яті А0

– А15.

Якщо потрібно, то

можна додати ще буфер для старших

розрядів адреси А16

– А19.

Напрямок передачі

буфера даних

(вхід T

мікросхеми DD3)

встановлюється

сиґналом з

виходу МП

![]() (передача даних – читання). Переведення

цих буферів до високоімпедансного або

робочого стану

відбувається за сиґналом

DEN

(дозвіл даних).

(передача даних – читання). Переведення

цих буферів до високоімпедансного або

робочого стану

відбувається за сиґналом

DEN

(дозвіл даних).

Центральний процесор на базі БІС серії К1810

На рис. 2.5 зображено схему ЦП на базі МП К1810ВМ86. У її основі лежить типова 8-кристальна структура [8], до складу якої, крім МП, входять ГТІ К1810ГФ84, системний контролер К1810ВК88, реалізований на трьох мікросхемах КР580ИР82 21-розрядний адресний регістр і двонаправлений 16-розрядний формувач шини даних на двох мікросхемах КР580ВА86.

У зображеній схемі ЦП

використано максимальний

режим роботи МП. Це зроблено з метою

уніфікації внутрішньомодульної шини

й забезпечення поступового переходу

на співпроцесорні

розширення центрального

МП. Як елементи розширення,

розглядають співпроцесор цифрового

оброблення К1810ВМ87 і

співпроцесор 80130 операційної системи

RMX86 [8].

Лінії

![]() і

і![]() резервуються для такого типу розширень

ЦП.

резервуються для такого типу розширень

ЦП.

Мікропроцесор ВМ86 вимагає наявності синхросиґналів CLK із крутими фронтами (≤10нс) і шпаруватістю 3, частота проходження яких 2-5 МГц. Існування мінімального значення частоти проходження імпульсів CLK пояснюється тим, що у МП ВМ86 використано запам’ятовуючі елементи динамічного типу, тому будь-яку маніпуляцію із синхросигналом заборонено.

Усі ці вимоги задовольняє

тактовий сиґнал,

сформований ГТІ

на базі К1810ГФ84. Пристрій

працює від кварцового резонатора (режим

![]() =0),що має в три рази більшу

частоту коливань, ніж

бажана для CLK.

Для одержання більше

точного й стабільного сиґналу

рекомендують використовувати

основну частоту кварцового резонатора.

=0),що має в три рази більшу

частоту коливань, ніж

бажана для CLK.

Для одержання більше

точного й стабільного сиґналу

рекомендують використовувати

основну частоту кварцового резонатора.

Між кварцовим резонатором і виводом Х2 необхідно ввімкнути конденсатор невеликої ємності (близько 15 пФ), яка має бути такою, щоб коефіцієнт підсилення кола зворотного зв’язку ґенератора не був меншим ніж 1. Для цього необхідно, щоб сума опорів кварцового резонатора й конденсатора на робочій частоті не перевищувала 1 кОм.

Рисунок 2.5 – Схема центрального процесора на базі К1810ВМ86

Ґенерований ГТІ

тактовий сиґнал ПП

PCLK

(він же – сиґнал системних

тактових імпульсів CCLK,що виходить на системну

маґістраль) має

шпаруватість 2 і частоту коливань, яка

дорівнює половині

частоти CLK.

Варіант прямого використання PCLK

як системних тактів

забезпечує вихідний струм

![]() ≤5

мА і припустиму ємність

навантаження

≤5

мА і припустиму ємність

навантаження

![]() ≤100пФ.

≤100пФ.

Для загального

скидання МП ВМ86 вимагає

подачі на свій вхід RESET

імпульсу тривалістю більше ніж

чотири періоди тактової частоти CLK,

за винятком випадку ввімкнення

джерела живлення, коли

тривалість імпульсу має становити

як мінімум 50 мкс.

Ґенератор ГФ84

має вбудовану логіку,що

спрощує формування даного сиґналу.

Для формування сиґналу

RESET

досить на вході

![]() організувати простеRC-коло

(рис. 7.8), що під час подачі напруги

живлення або натискання

клавіші RESET

автоматично забезпечує формування

імпульсу скидання необхідної тривалості.

Цей імпульс також використовують

як сиґнал загального

скидання INIT

всієї системи з

максимальним вихідним струмом

організувати простеRC-коло

(рис. 7.8), що під час подачі напруги

живлення або натискання

клавіші RESET

автоматично забезпечує формування

імпульсу скидання необхідної тривалості.

Цей імпульс також використовують

як сиґнал загального

скидання INIT

всієї системи з

максимальним вихідним струмом

![]() =5мА.

Для збільшення навантажувальної

здатності лінії скидання

INIT

використовують додаткові

маґістральні підсилювачі.

=5мА.

Для збільшення навантажувальної

здатності лінії скидання

INIT

використовують додаткові

маґістральні підсилювачі.

Ще однією функцією, що може підтримувати ГТІ, є прийом і синхронізація двох сиґналів готовності ПП до обміну. Звичайно один сиґнал готовності надходить від локальної шини МП, а інший – від системної маґістралі.

Умова готовності:

![]() ,

деRDY1,

RDY2

– сиґнали готовності

від ПП, a

,

деRDY1,

RDY2

– сиґнали готовності

від ПП, a

![]() і

і![]() – керуючі сиґнали,що визначають,

з якою шиною в даному

машинному циклі працює МП. Лінії

готовності звичайно формують за схемою

з відкритим колектором

і можуть мати як високий

(ХАСК), так і низький

(

– керуючі сиґнали,що визначають,

з якою шиною в даному

машинному циклі працює МП. Лінії

готовності звичайно формують за схемою

з відкритим колектором

і можуть мати як високий

(ХАСК), так і низький

(![]() )

рівень активності. Використовуючи

симетрію елементів париRDY,

)

рівень активності. Використовуючи

симетрію елементів париRDY,

![]() ,

користувач вибирає відповідний вхід

(прямій або інверсний)

для прийому сигналу

готовності від ПП. Інший

елемент при цьому слугує

для допоміжних цілей, наприклад для

керування вибором шини.

У схемі на рис. 2.5, орієнтованій

на одномаґістральну

архітектуру, використовується

одна лінія готовності або підтвердження

до обміну ХАСК із високим

рівнем активності (готовий за

замовчуванням).

,

користувач вибирає відповідний вхід

(прямій або інверсний)

для прийому сигналу

готовності від ПП. Інший

елемент при цьому слугує

для допоміжних цілей, наприклад для

керування вибором шини.

У схемі на рис. 2.5, орієнтованій

на одномаґістральну

архітектуру, використовується

одна лінія готовності або підтвердження

до обміну ХАСК із високим

рівнем активності (готовий за

замовчуванням).

Додаткову можливість

забезпечує вхід

![]() ,

що керує способом синхронізації

прийнятого сиґналу

готовності. При

,

що керує способом синхронізації

прийнятого сиґналу

готовності. При

![]() =0

виконується двоступінчаста синхронізація

сиґналу за фронтом

і зрізом тактової

частоти CLK.

Якщо на

=0

виконується двоступінчаста синхронізація

сиґналу за фронтом

і зрізом тактової

частоти CLK.

Якщо на

![]() подається напруга високого рівня,

реалізується процедура одноступінчатої

синхронізації за зрізом

CLK.

Орієнтація на лінію ХАСК

із високим рівнем активності вимагає

застосування одноступінчатого способу

синхронізації, коли зумовлена процедурою

синхронізації затримка сиґналу

готовності мінімальна. У такті Т3

кожного машинного

циклу МП опитує вхід готовності READY.

Для правильного

призупинення МП у

поточному циклі необхідно, щоб сиґнал

ХАСК був установлений

в 0 за 35 нс до початку Т3.

подається напруга високого рівня,

реалізується процедура одноступінчатої

синхронізації за зрізом

CLK.

Орієнтація на лінію ХАСК

із високим рівнем активності вимагає

застосування одноступінчатого способу

синхронізації, коли зумовлена процедурою

синхронізації затримка сиґналу

готовності мінімальна. У такті Т3

кожного машинного

циклу МП опитує вхід готовності READY.

Для правильного

призупинення МП у

поточному циклі необхідно, щоб сиґнал

ХАСК був установлений

в 0 за 35 нс до початку Т3.

Ще одна лінія CSYNC (зовнішня синхронізація) дозволяє декільком ГТІ ГФ84 синхронізувати свою роботу. У найпростішому випадку вивід CSYNC має бути заземлено.

Орієнтація на максимальний режим роботи МП ВМ86 зумовила введення до складу ЦП системного контролера ВК88, однак можлива досить проста імітація його роботи (рис. 2.6). Не виключений також варіант переходу до мінімального режиму роботи, коли необхідна для формування сиґналів керування системної шини додаткова логіка мінімальна.

Рисунок 2.6 – Схема контролера

шини для ВМ86,що

працює в максимальному режимі (MN/![]() =0)

=0)

Системний контролер ВК88

запрограмовано для роботи в режимі

системної маґістралі

(IOВ=0). Напруга

низького рівня на вході дозволу

адреси

![]() вказує контролеру на

монопольне володіння системною шиною,

завдяки чому команди маґістралі

формуються контролером з

мінімально можливими затримками.

вказує контролеру на

монопольне володіння системною шиною,

завдяки чому команди маґістралі

формуються контролером з

мінімально можливими затримками.

Контролер ВК88

працює синхронно із МП ВМ86.

Він приймає код поточного машинного

циклу

![]() і формує весь набір сиґналів,

необхідний для його виконання. Часові

діаграми циклів вводу й виводу

в максимальному режимі без тактів

очікування наведено

на рис. 2.7.

і формує весь набір сиґналів,

необхідний для його виконання. Часові

діаграми циклів вводу й виводу

в максимальному режимі без тактів

очікування наведено

на рис. 2.7.

Відповідно до коду

![]() системний контролер формує п'ять

стандартних ліній

керування

системний контролер формує п'ять

стандартних ліній

керування

![]() ,

,![]() ,

,![]() ,

,![]() ,

,![]() ,

навантажувальна здатність

яких

,

навантажувальна здатність

яких

![]() ≤32

мА,

≤32

мА,![]() ≤300

пФ.

≤300

пФ.

Дві лінії керування з

упередженням

![]() ,

,

![]() мають ту ж саму навантажувальнуздатність. Вибір між

стандартним варіантом і варіантом з

упередженнямвідповідної лінії

керування покладається

накористувача. Строби

мають ту ж саму навантажувальнуздатність. Вибір між

стандартним варіантом і варіантом з

упередженнямвідповідної лінії

керування покладається

накористувача. Строби

![]() й

й![]() (див. рис. 2.7, б) ґенеруються

в третьому такті машинного циклу, тому

для забезпечення можливості роботи

системної шини з тактами

очікування рекомендується

зупинити свій вибір на керуванні

з упередженням. У цьому

випадку час між початком стробу

керування й першою

перевіркою сиґналу

ХАСК становить

близько 130 нс. Це той час, що надається

ПП на ухвалення рішення

й установлення сиґналу

ХАСК в 0 для введення

тактів очікування.

(див. рис. 2.7, б) ґенеруються

в третьому такті машинного циклу, тому

для забезпечення можливості роботи

системної шини з тактами

очікування рекомендується

зупинити свій вибір на керуванні

з упередженням. У цьому

випадку час між початком стробу

керування й першою

перевіркою сиґналу

ХАСК становить

близько 130 нс. Це той час, що надається

ПП на ухвалення рішення

й установлення сиґналу

ХАСК в 0 для введення

тактів очікування.

Рисунок 2.7 – Часові діаграми циклів читання (а) і запису (б) центрального процесора

Окрім сиґналів

системного керування,

контролер формує ряд допоміжних

сиґналів, використовуваних

в інтерфейсній логіці

ЦП: ALE

– строб

знімання адреси з

мультиплексованих

ліній

![]() /S7,

A19/S6

– A16/S3,

AD15 – AD0; DT/

/S7,

A19/S6

– A16/S3,

AD15 – AD0; DT/![]() – сиґнал керування

напрямком передачі

через шинний драйвер; DEN

– строб включення

шинного драйвера; МСЕ

– строб дозволу

зчитування адресної інформації CAS2

– CAS0

із ведучого контролера

переривань у циклі підтвердження

переривання. Максимальний вихідний

струм цих ліній IOL≤16

мА, ємність навантаження

CL≤80

пФ. За сиґналом ALE

адресна інформація фіксується в

21-розрядному буферному регістрі,

побудованому на основі

трьох мікросхем КР580ИР82.

– сиґнал керування

напрямком передачі

через шинний драйвер; DEN

– строб включення

шинного драйвера; МСЕ

– строб дозволу

зчитування адресної інформації CAS2

– CAS0

із ведучого контролера

переривань у циклі підтвердження

переривання. Максимальний вихідний

струм цих ліній IOL≤16

мА, ємність навантаження

CL≤80

пФ. За сиґналом ALE

адресна інформація фіксується в

21-розрядному буферному регістрі,

побудованому на основі

трьох мікросхем КР580ИР82.

Вихідні лінії регістра

організують потужну

демультиплексовану

адресну шину (![]() ≤32 мА,

≤32 мА,

![]() ≤300

пФ), що забезпечує адресацію 1 Мбайта

пам'яті й 64 Кбайтів

простору ВВ.

Можлива заміна регістрів КР580ИР82

на регістри КР580ИР83

з інверсією або на

будь-які інші аналогічного типу.

≤300

пФ), що забезпечує адресацію 1 Мбайта

пам'яті й 64 Кбайтів

простору ВВ.

Можлива заміна регістрів КР580ИР82

на регістри КР580ИР83

з інверсією або на

будь-які інші аналогічного типу.

Мультиплексована шина адреси/даних AD19 – AD0 є внутрішньоплатною шиною даних: усі резидентні ресурси МК можуть підключатися до неї. Мультиплексована шина AD19 – AD0 має малий вихідний струм IOL≤2 мА і ємність навантаження CL≤100 пФ, що може не забезпечити в багатоплатних розширеннях ґарантованих характеристик на змінному струмі.

Для усунення цього недоліку до складу ЦП введено двонаправлений 16-розрядний драйвер міжмодульної шини даних (дві мікросхеми КР580ВА86). При орієнтації на системну маґістраль з інверсною шиною мікросхеми КР580ВА86 має бути замінено на КР580ВА87 або еквівалентні їм.

У випадку звертання до

ресурсів, розташованих

поза платою (![]() =1 і

=1 і

![]() =1),

драйвер керується сиґналом

DT/

=1),

драйвер керується сиґналом

DT/![]() . У противному випадку (

. У противному випадку (![]() =0 і/або

=0 і/або

![]() =0)

драйвер здійснює передачу інформації

з мультиплексованої

шини на системну, що дає можливість

спостерігати за процесом проходження

даних усередині модуля.

Цю властивість МП можна використати в

налагоджувальних і

тестових цілях.

=0)

драйвер здійснює передачу інформації

з мультиплексованої

шини на системну, що дає можливість

спостерігати за процесом проходження

даних усередині модуля.

Цю властивість МП можна використати в

налагоджувальних і

тестових цілях.

Побудова модулів пам’яті МПС

Вихідними «цеглинками» під час побудови модулів пам’яті МПС слугують окремі ВІС статичної або динамічної оперативної пам’яті, а також ВІС ПЗП. ВІС пам’яті, що випускаються різними фірмами, більшою мірою стандартизовані за зовнішнім інтерфейсом, а у більшості випадків навіть і за нумерацією виводів порівняно з іншими типами мікропроцесорних ВІС.

Для МП-комплектів випускають 1-, 4-, 8- і 16-розрядні ВІС пам’яті. Слід зазначити, що однорозрядна організація дозволяє при заданому числі виводів корпусу мікросхеми «упакувати» у неї максимальне число бітів.

Під час побудови модулів пам’яті виникають задачі нарощування інформаційної ємності шляхом об’єднання ВІС у відповідну матрицю, а також буферизації шин адреси, даних і керування. Нарощування ємності може проводитися двома шляхами. По-перше, можна розширювати розрядність шляхом паралельного ввімкнення ВІС. Останні в цьому випадку поєднуються за всіма виводами, крім інформаційних, які в сукупності утворюють розширену інформаційну шину.

Другий шлях

нарощування інформаційної ємності

– об’єднання ВІС

пам’яті за інформаційними входами –

виходами. Крім них, поєднуються

всі інші входи за винятком входів

![]() (вибір чипа). Сиґнали

на цих входах визначають,

якій з мікросхем

необхідно включатися в роботу. Максимальне

число поєднуваних у

такий спосіб ВІС визначається

припустимим ємнісним навантаженням

на виході мікросхеми.

(вибір чипа). Сиґнали

на цих входах визначають,

якій з мікросхем

необхідно включатися в роботу. Максимальне

число поєднуваних у

такий спосіб ВІС визначається

припустимим ємнісним навантаженням

на виході мікросхеми.

ПЗП, як правило, випускаються багаторозрядними. Розрядність ПЗП, так само, як і розрядність МП, становить 4, 8, 16. Це зв’язано, у першу чергу, зі зручністю занесення й зміни інформації в ПЗП. Дійсно, записувати інформацію в ПЗП цілими словами набагато зручніше, ніж, припустимо, по одному розряду в кожне з декількох ПЗП, що утворюють задану довжину слова.

Освоєно випуск і ВІС

статичних ОЗП,

аналогічних за виводами

та їхнім призначенням

виводам програмованих

ПЗП. Наприклад, ОЗП

типу К537РУ9 має, як і

мікросхеми ПЗП типу

К573РФ2, РФ5, організацію 2Кх8

і аналогічну цокольовку,

за винятком одного виводу

(21). У ПЗП

на цей вивід подається

напруга програмування, а в мікросхемі

ОЗП – це вхід керування

записом

![]() .

.

Таким чином, можна задати резервування на друкованій платі посадкових місць під мікросхеми пам’яті з практично ідентичним розведенням виводів, куди залежно від розв’язуваного завдання можна встановлювати мікросхеми ОЗП й ПЗП в необхідному співвідношенні.

Приклад схеми ввімкнення пристроїв пам’яті в МПС показано на рис. 2.8.

У цьому випадку використовують мікросхеми ПЗП з ультрафіолетовим стиранням типу К573РФ2 або К573РФ5 і мікросхеми статичного ОЗП типу К537РУ9. Кожна з цих мікросхем здатна зберігати 2 кбайти інформації, поданої представленої у вигляді 2048 восьмирозрядних слів.

Вибір потрібного слова

проводять за допомогою

одинадцяти адресних

сиґналів А0

– А10.

Крім того, ці мікросхеми

мають входи

![]() (вибір чипа), на які подаються сиґнали,що залежать від стану

старших розрядів адресної шини МПС А11

– А15.

Як видно з рис. 2.8,

керування цими входами

здійснюється за допомогою дешифратора

типу К555ИД7.

(вибір чипа), на які подаються сиґнали,що залежать від стану

старших розрядів адресної шини МПС А11

– А15.

Як видно з рис. 2.8,

керування цими входами

здійснюється за допомогою дешифратора

типу К555ИД7.

Рисунок

2.8 – Схема ввімкнення

пристроїв пам’яті

Рисунок

2.8 – Схема ввімкнення

пристроїв пам’яті

Мікросхеми ПЗП (ROM) і ОЗП (RAM) включаються в роботу тоді, коли старші розряди адресної шини А15 – A11 будуть перебувати в станах 00000 і 00001. Таким чином, комірки ПЗП й ОЗП займають в адресному просторі відповідно області 0000Н – 07FF Н и 0800H – 0FFFН.

Переведення виходів

мікросхем пам’яті до високоімпедансного

стану здійснюється під

час подачі логічної одиниці на входи

![]() (дозвіл виходу) з

лінії

(дозвіл виходу) з

лінії

![]() шини керування МП.

Напрямок передачі

інформації в ОЗП

змінюється залежно від сиґналу

на лінії

шини керування МП.

Напрямок передачі

інформації в ОЗП

змінюється залежно від сиґналу

на лінії

![]() шини керування.

шини керування.

У ПЗП є вхід увімкнення режиму програмування PG. Оскільки звичайно програмування ПЗП здійснюється не в складі МПС, у режимі читання на цей вхід подається напруга живлення (+5В).

За необхідності об’єм

пам’яті в пристрої за

схемою рис. 2.8 може бути збільшено. Це

досягається шляхом увімкнення

додаткових ПЗП

або ОЗП. При цьому

мікросхеми К573РФ2 або К537РУ9

вмикають точно так само, як це показано

на рис. 2.8, але їхні входи приєднуються

до інших виходів

![]() дешифратораDC.

Найбільше число

мікросхем пам’яті, що включають

паралельно на шину даних без додаткових

буферів, звичайно обмежено

припустимим ємнісним навантаженням

виходів мікросхем пам’яті.

дешифратораDC.

Найбільше число

мікросхем пам’яті, що включають

паралельно на шину даних без додаткових

буферів, звичайно обмежено

припустимим ємнісним навантаженням

виходів мікросхем пам’яті.

Розглянуту схему ввімкнення

пристроїв пам’яті

розраховано на керуючу шину МП типу

ВМ80. Якщо ж застосовується

МП типу ВМ85, то замість

сигналів

![]() і

і![]() використовують сиґнали

використовують сиґнали

![]() й

й![]() ,

а на один із входів

дозволу дешифратора

DC подається

сиґнал

,

а на один із входів

дозволу дешифратора

DC подається

сиґнал

![]() .

.

Пристрої вводу-виводу МПС

Ввід і вивід інформації в МПС здійснюється, як правило, за допомогою спеціальних ВІС. Схему ввімкнення типових ВІС вводу-виводу показано на рис. 2.9.

Рисунок 2.9 – Схема ввімкнення пристроїв вводу-виводу

Однією з найбільш уживаних мікросхем вводу-виводу є ВІС паралельного периферійного адаптера. На рис. 2.9 – це мікросхема типу КР580ВВ55. Такий адаптер дозволяє перемикати шину даних МПС на роботу з одним із трьох портів вводу-виводу: РА, РВ або PC. Керування адаптером здійснюється програмно. Після початкового установлення по входу RES у мікросхему через шину даних записується керуюча інформація,що визначає режим роботи кожного з портів. Таких режимів три – простий ввід-вивід (режим 0), стробована односпрямована передача інформації (режим 1) і стробована двонаправлена передача інформації (режим 2) [3].

Адресація до конкретного порту адаптера реалізується за допомогою адресних сиґналів А0 і А1 (рис. 6). При цьому сполученням А1, А0 виду 00, 01, 10 відповідають порти РА, РВ і PC. За наявності двох одиниць на входах А1, А0 мікросхеми відбувається запис із шини даних у внутрішній керуючий регістр призначеної для адаптера керуючої інформації.

Як і у випадку включення пристроїв пам’яті (рис. 2.8), у цьому випадку дешифрація старших розрядів адреси пристроїв вводу-виводу здійснюється за допомогою дешифратора К555ИД7.

З рис. 2.9 неважко встановити, що портам РА, РВ, PC і керуючому регістру паралельного периферійного адаптера ВВ55 задано адреси 28Н, 29Н, 2АН, 2ВН.

До портів РА й РВ може бути підключено різні джерела й приймачі інформації, наприклад, аналого-цифрові й цифро-аналогові перетворювачі. Порт PC частіше використовують для прийому й формування сиґналів,що супроводжують обмін інформацією, зокрема для вироблення сиґналів переривання.

Детально питання програмування й застосування паралельного периферійного адаптера, так само як і інших пристроїв вводу-виводу висвітлено в [6].

Програмований таймер КР580ВИ53 може бути використано для вводу в МП сиґналів, що відповідають частоті або тривалості імпульсів, для підрахунку числа подій, для завдання часових інтервалів тощо. Цей таймер містить три 16-розрядні лічильники (0; 1; 2), що працюють на віднімання. Лічильники можуть бути запрограмовані як для двійкового, так і для двійково-десяткового рахунку. Програмним способом можна також здійснювати й початкову установку лічильників, записуючи в них довільне число.

Адресація трьох лічильників

розглянутого таймера, так само, як і

портів розглянутого вище паралельного

адаптера, реалізується

за допомогою двох адресних входів А0,

А1

і входу

![]() .

Внутрішній керуючий регістр, у який

під час програмування режиму таймера

записуються керуючі слова, під час

адресації виступає як четвертий канал

таймера. У пристрої за

схемою рис. 2.9 лічильникам 0; 1; 2 і керуючому

регістру таймера

відповідають адреси 24Н, 25Н, 26Н, 27Н.

.

Внутрішній керуючий регістр, у який

під час програмування режиму таймера

записуються керуючі слова, під час

адресації виступає як четвертий канал

таймера. У пристрої за

схемою рис. 2.9 лічильникам 0; 1; 2 і керуючому

регістру таймера

відповідають адреси 24Н, 25Н, 26Н, 27Н.

Кожний з лічильників таймера

має тактовий вхід (![]() ),

вхід керування – дозволу

рахунку (

),

вхід керування – дозволу

рахунку (![]() )

і вихід (

)

і вихід (![]() ).

Лічильники можуть

працювати в одному з шести

режимів, формуючи на виході однократні

або періодичні, позитивні або неґативні

перепади та імпульси. Кодовий стан

кожного з лічильників може бути зчитаний

мікропроцесором. Причому можливі два

режими зчитування: із зупинкою або без

зупинки рахунку (з

переписуванням числа з лічильника в

спеціальний внутрішній регістр таймера).

).

Лічильники можуть

працювати в одному з шести

режимів, формуючи на виході однократні

або періодичні, позитивні або неґативні

перепади та імпульси. Кодовий стан

кожного з лічильників може бути зчитаний

мікропроцесором. Причому можливі два

режими зчитування: із зупинкою або без

зупинки рахунку (з

переписуванням числа з лічильника в

спеціальний внутрішній регістр таймера).

Останній із пристроїв вводу-виводу, зображених на рис. 2.9 – це послідовний периферійний адаптер (адаптер послідовного інтерфейсу) КР580ВВ51. Цей адаптер дозволяє передавати й приймати інформацію в синхронному й асинхронному режимах у вигляді послідовного коду. При цьому в асинхронному режимі кожна кодова посилка забезпечується спеціальними стартовими й стоповими бітами, що дозволяють установити її початок і кінець. Першим іде стартовий біт, що дорівнює нулю, далі потрібний код інформації – до 8 біт, наступний біт – це біт контролю на парність або непарність і, нарешті, завершують слово стопові біти, що дорівнюють одиниці. Тривалість стопового сигналу може становити 1; 1,5 або 2 біти.

Для роботи послідовного

адаптера необхідні тактові імпульси

(вхід CLK),

частота яких не має значення, але вона

має не менше ніж

в 4,5 раза в асинхронному

й в 30 разів у синхронному

режимі перевищувати частоту бітів,

що передаються або приймаються.

У пристрої за схемою

рис. 6 з цією метою

використовують тактові

імпульси

![]() ,

одержувані з

тактового генератора системи. Швидкість

видачі бітів на вихід

передавача Tx

або швидкість прийому

бітів із входу приймача

Rx

призначається програмно залежно від

частоти синхронізуючих

імпульсів, щоподаються

на входи ТхС і RxС.

При цьому може бути встановлена частота

передачі або прийому,

що дорівнює частоті синхронізуючих

імпульсів або менша цієї частоти в 16

або 64 рази.

,

одержувані з

тактового генератора системи. Швидкість

видачі бітів на вихід

передавача Tx

або швидкість прийому

бітів із входу приймача

Rx

призначається програмно залежно від

частоти синхронізуючих

імпульсів, щоподаються

на входи ТхС і RxС.

При цьому може бути встановлена частота

передачі або прийому,

що дорівнює частоті синхронізуючих

імпульсів або менша цієї частоти в 16

або 64 рази.

Якщо орієнтуватися на швидкість передачі й прийому 9600 біт/с, і взяти, що частота синхронізуючих імпульсів буде ділитися всередині послідовного адаптера на 16, то на входи ТхС і RxС необхідно подавати імпульси,що мають частоту 153,6 кГц. У розглянутому пристрої (рис. 6) синхронізуючі імпульси виробляються дільником на 13, побудованим на лічильнику К555ИЕ7. На вхід цього дільника подається тактова частота МП, що дорівнює 2 МГц. Відповідно частота вихідних імпульсів дорівнює 153,8 кГц. Як видно, ми не одержуємо точно потрібної частоти (153,6 кГц). Але це не має вирішального значення. Справа в тому, що адаптер автоматично настроюється так, щоб фіксувати стартовий біт кожної кодової посилки в момент часу, що відповідає його середині. Інші біти фіксуються в моменти, зумовлені частотою синхронізуючих імпульсів. Отже, досить забезпечити рівність частот прийому й передачі з похибкою кілька відсотків. За цієї умови всі біти прийнятої інформації будуть зафіксовані правильно.

Оскільки послідовний код можна досить просто передавати по лінії зв’язку на значні відстані, то адаптери такого типу можуть забезпечити обмін інформацією між МПС і деяким віддаленим периферійним об’єктом. Як лінія зв’язку, при цьому може виступати звичайна телефонна лінія. Природно, що для організації послідовного каналу потрібні як мінімум два адаптери, один з яких буде передавати, а другий – одержувати інформацію. Обидва адаптери має бути настроєно узгоджено.

У режимі асинхронної передачі кодові посилки можуть чергуватися з паузами довільної тривалості. При цьому на лінії підтримується сиґнал «одиниця» і приймач перебуває в режимі очікування. Із приходом стартового біта починається прийом чергової посилки. При синхронній передачі кодові посилки безупинно ідуть одна за одною.

Для програмування послідовного

адаптера в його керуючі регістри

завантажують керуючі слова. Ці регістри

підключають до шини даних за наявності

сиґналу 1 на вході

![]() (команда – дані). Перші слова (одне або

два), подані

після початкового скидання по входу

RES,

визначають загальний

режим роботи адаптера. Наступні слова

(команди), подані при

(команда – дані). Перші слова (одне або

два), подані

після початкового скидання по входу

RES,

визначають загальний

режим роботи адаптера. Наступні слова

(команди), подані при

![]() =1,

уточнюють або змінюють цей режим.

=1,

уточнюють або змінюють цей режим.

По входах

![]() і

і![]() установлюється напрямок

передачі інформації: з внутрішніх

регістрів даних адаптера на шину даних

МП або навпаки.

установлюється напрямок

передачі інформації: з внутрішніх

регістрів даних адаптера на шину даних

МП або навпаки.

Для включення

в роботу послідовного адаптера

використовують вхід

![]() .

Приєднання адресної лініїА0

або А1

до входу

.

Приєднання адресної лініїА0

або А1

до входу

![]() адаптера дозволяє розділити канали

керуючих регістрів і регістрів даних.

У пристрої за схемою

рис. 2.9 керуючим регістрам відповідає

одна з адрес 22Н або 23Н, а регістрам даних

– 20Н або 21Н.

адаптера дозволяє розділити канали

керуючих регістрів і регістрів даних.

У пристрої за схемою

рис. 2.9 керуючим регістрам відповідає

одна з адрес 22Н або 23Н, а регістрам даних

– 20Н або 21Н.

Виходи RxRD – готовність приймача й TxRD – готовність передавача можуть використовуватися для того, щоб інформувати МП (наприклад, по входах переривання) про готовність адаптера видати на шину даних або прийняти з шини даних черговий байт інформації.

Слід зазначити, що номенклатура ВІС вводу-виводу на сьогодні достатньо широка. Можна згадати, зокрема, суміщені ВІС пам’яті та вводу-виводу, що входять до серії К1821 (наприклад, 2 кбайти ПЗП, два паралельні порти й один послідовний канал вводу-виводу).

Розрахунок сумарної споживаної потужності МПС

Сумарна споживана потужність МПС з невеликою похибкою являє собою потужність, споживану мікросхемами системи. Під час визначення споживаних потужностей окремих елементів можливі 3 варіанти:

1. В технічній документації в явному виді задано значення споживаної або розсіюваної потужності, що у такому випадку й приймається за розрахункове.

Відомі значення напруг живлення й споживаних струмів. У цьому випадку

![]() ,

,

де

![]() -

число джерел живлення мікросхеми.

-

число джерел живлення мікросхеми.

Для мікросхем елементарної логіки

![]() ,

,

де

![]() -

споживані струми при різних логічних

станах виходів мікросхеми.

-

споживані струми при різних логічних

станах виходів мікросхеми.

Модель розподілу адресного простору

Подібну модель наочніше зображувати у вигляді таблиці. Як приклад, для МПС, принципову схему якої наведено в додатку В, модель розподілу адресного простору буде мати вигляд, показаний на рис. 2.10 (з урахуванням того, що в даному випадку МПС побудовано на базі МП КР580ВМ80, під час звертання до мікросхем ІВВ у старших двох тетрадах адреси дублюється стан молодших).

Рисунок 2.10 – Приклад моделі розподілу адресного простору МПС

Часові діаграми режимів роботи МПС

Для МП КР580ВМ80 діаграми читання пам’яті аналогічні діаграмам читання зовнішніх пристроїв (також аналогічні діаграми запису до пам’яті й у зовнішні пристрої). У них є одна особливість: команди роботи з пам’яттю MOV M,R і MOV R,M - двобайтні й на їхнє виконання йде два машинні цикли (МЦ), а команди роботи із зовнішніми пристроями IN і OUT – трибайтні – на їхнє виконання йде три МЦ. Причому перший МЦ для команд MOV і перші два для команд IN і OUT ідуть на добування команди, в останньому МЦ ці команди виконуються. Цикл добування команди звичайно пов’язаний із читанням пам’яті. Розглянемо його докладніше (див. діаграми на рис. 2.11-2.12).

У першому такті Т1 по передньому фронту

F2 на виході SYNCз’являється сиґнал

високого рівня, визначаючи перший такт

МЦ. Крім того, на ШД у цьому такті

з’являється слово стану, у якого в

розрядах D1, D5, D7 записано одиниці (за

сиґналом![]() це слово фіксується в КР580ВК28). За

переднім фронтом

це слово фіксується в КР580ВК28). За

переднім фронтом![]() у цьому такті на адресній шині

встановлюється адреса комірки пам’яті

(КП), що надійшла у буфер адреси з

лічильника команд МП.

у цьому такті на адресній шині

встановлюється адреса комірки пам’яті

(КП), що надійшла у буфер адреси з

лічильника команд МП.

У другому такті Т2 на виході МП DBINз’являється сиґнал високого рівня, за яким звичайно відбувається читання пам’яті й зовнішніх пристроїв. У цьому такті МП опитує сиґнали на входахREADY,HOLDі тригеріHLDA. Залежно від значення сиґналів на цих виводах МП переходить у різні стани: очікування, захоплення або зупинення. Якщо на виводиREADY,HOLDнадійшли сиґнали 1, 0, а тригерHLDAустановлений в 0, то МП переходить у стан Т3.

У Т3 може виконуватися або завершуватися читання пам’яті, після чого ШД переходить у високоімпедансний стан. Слід зазначити, що звичайно до четвертого такту Т4 уже змінюється значення лічильника команд і, таким чином, у ньому перебуває адреса нової команди або наступного байта, що надійде на адресні шини в першому такті наступного МЦ.

У четвертому такті Т4 код команди, що надійшла в регістр команд, дешифрується – визначається, скільки циклів і тактів потрібно для її виконання.

Як видно з діаграм, в 2-му МЦ для команд INіOUTусього три машинні такти – немає необхідності дешифрувати команду. В іншому цикл добування другого байта аналогічний циклу добування першого.

Цикл виконання команди.Сиґнал SYNC

символізує початок МЦ. За сигналом![]() у КР580ВК28 фіксується слово стану. За

цим сиґналом з’являються сиґнали на

у КР580ВК28 фіксується слово стану. За

цим сиґналом з’являються сиґнали на![]() (для читання ІВВ) або на

(для читання ІВВ) або на![]() (для читання пам’яті). На ША в цей момент

зафіксовано адресу пристрою, з яким

здійснюється обмін. По спаду в Т2 на ШД

з’являється інформація, що має бути

зчитана або записана. Якщо йде процес

запису в пам’ять або УВВ, то сиґнали,

що дозволяють запис, фіксуються в 3-му

такті на виході КР580ВК28 за сиґналом

(для читання пам’яті). На ША в цей момент

зафіксовано адресу пристрою, з яким

здійснюється обмін. По спаду в Т2 на ШД

з’являється інформація, що має бути

зчитана або записана. Якщо йде процес

запису в пам’ять або УВВ, то сиґнали,

що дозволяють запис, фіксуються в 3-му

такті на виході КР580ВК28 за сиґналом![]() із МП.

із МП.

|

|

Рисунок 2.11 – Часові діаграми роботи з пам'яттю: запис у пам’ять MOV M, RBS; читання пам’яті MOV RBD, M

|

|

|

Рисунок 2.12 – Часові діаграми роботи із пристроями вводу-виводу: читання пристроїв – IN; запис до пристроїв OUT OUT |