Микропроцесоры_Ответы

.pdf

. adres

In(out)

BX, CX, DX

part

.data AX

3.2.3. Команди вводу/виводу. Синтаксис команд

Тема 4.1: Загальні принципи та методи побудови мікропроцесорів сімейства i8086.

4.1.1. Узгодження інтерфейсу процесору i8086 з системною шиною.

До 16-розрядних МП першого покоління належать МП i8086/i8088 та i80186/i80188, до МП другого покоління - i80286. Мікропроцесор має внутрішній надоперативний запам’ятовувальниий пристрій (НОЗП) ємністю 14x16 байт. Шина адреси 20-розрядна, що дозволяє безпосередньо адресувати до 220= 1048576 комірок пам'яті (1 Мбайт).

У МП i8086 застосовано конвеєрну архітектуру, що дозволяє сумістити у часі цикли вибірки команди та вибірки з пам'яті кодів наступних команд. Це досягається паралельною роботою двох порівняно незалежних пристроїв - операційного пристрою та шинного інтерфейсу. Структурну схему МП i8086 показано на рисунку 1. Операційний пристрій виконує команду, а шинний інтерфейс здійснює взаємодію із зовнішньою шиною: виставляє адреси, зчитує коди команд, записує результати обчислень у пам'ять або пристрої введення-виведення.

Операційний пристрій складається з регістрів загального призначення (РЗП), призначених для зберігання проміжних результатів - даних та адрес; АЛП з буферними регістрами; регістра ознак; блока керування та синхронізації (БК та С), який дешифрує коди команд і генерує сигнали керування для всіх блоків схеми МП. Шинний інтерфейс складається з шести байтової регістрової пам'яті, яка називається чергою команд, чотирьох сегментних регістрів: CS, DS, ES, SS, вказівника команд IP, суматора, а також допоміжних регістрів зв'язку і буфера шин (БШ) адреси/даних. Черга команд працює за принципом FIFO (First Input - First Output, тобто перший прийшов - перший пішов) і зберігає на виході порядок надходження команд. Довжина черги 6 байт.

Коли операційний пристрій зайнятий виконанням команди, шинний інтерфейс самостійно ініціює випереджаючу вибірку кодів команд з пам'яті у чергу команд. Вибирання з пам'яті чергового командного слова здійснюється тоді, коли в черзі виявляється два вільні байти. Черга збільшує швидкодію процесора у випадку послідовного виконання команд. У разі вибирання команд переходів, викликів і повернень з підпрограм та обробленні запитів переривань черга команд скидається і вибирання починається з нового місця програмної пам'яті.

Рисунок1 –Структурна схема мікропроцесора i8086

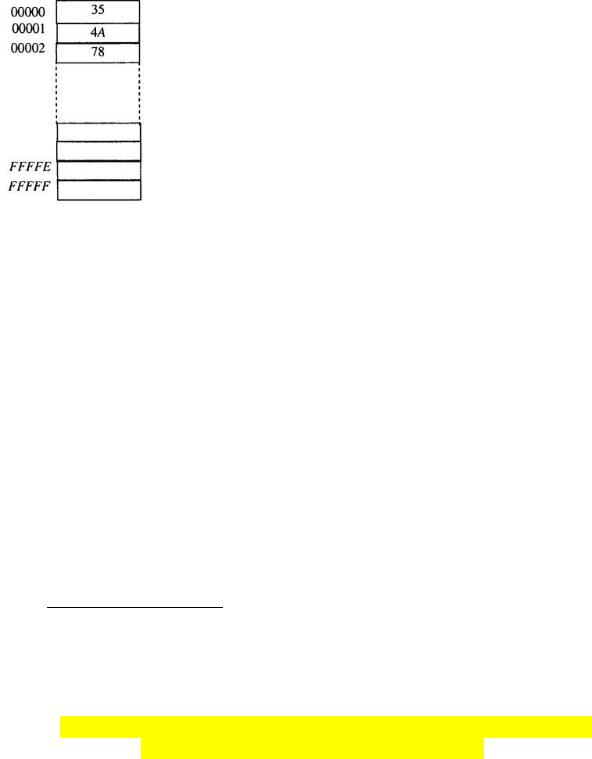

Ще одним із завдань шинного інтерфейсу є формування фізичної 20-розрядної адреси із двох 16-розрядних слів. Першим словом є вміст одного з сегментних регістрів CS, SS, DS, ES, а друге слово залежить від типу адресації операнда або коду команди. Складання 16-розрядних слів відбувається зі зміщенням на 4 розряди і здійснюється за допомогою суматора, що входить до складу шинного інтерфейсу. Пам'ять являє собою масив ємністю 1 Мбайт (рисунок2). У пам'яті зберігаються як байти, так і двобайтові слова. Слова розміщуються у двох сусідніх комірках пам'яті; старший байт зберігається у комірці зі старшою адресою, молодший - з молодшою. Адресою слова вважається адреса його молодшого байта.

У МП i8086 застосовано сегментну організацію пам'яті, яка характеризується тим, що програмно доступною є не вся пам'ять, а лише деякі сегменти, тобто області пам'яті. Усередині сегмента використовують лінійну адресацію.

4.1.2.Схема включення процесору i8086 в мінімальному режимі.

4.1.3.Схема включення процесору i8086 в максимальному режимі.

Особенностью МП i8086 является возможность частичной реконфигурации

аппаратной части для обеспечения работы в двух режимах — минимальном и максимальном. Режимы работы задаются аппаратно. В минимальном режиме, используемом для построения однопроцессорных систем, МП самостоятельно формирует все сигналы управления внутренним системным интерфейсом. В максимальном режиме, используемом для построения мультипроцессорных систем, МП формирует на линиях состояния двоичный код, который зависит от типа цикла шины. В соответствии с этим кодом системный контроллер К1810ВГ88 формирует сигналы управления шиной. Контакты, которые освободились в результате кодирования информации, используются для управления мультипроцессорным режимом.

Режимы назначаются с помощью вывода (MN/MX), который либо заземляется (для получения максимального режима), либо подключается к источнику питания +5В (для получения минимального режима).

В минимальном режиме i8086 работает просто как достаточно быстрый 16разрядный i8080 с расширенной системой команд.

Максимальный режим ориентирован на работу i8086 в составе мультимикропроцессорных систем, в которых, помимо нескольких центральных процессоров i8086, могут функционировать специализированные процессоры ввода/вывода i8089, сопроцессоры "плавающей арифметики" i8087.

Тема 5.1: Система команд i8086. Система переривів. Адресація пам’яті. Директиви передачі керування.

5.1.1. Команди перериву за типом вектору. Синтаксис команд.

В процессе идентификации источника запроса ему ставился в соответствие восьмиразрядный двоичный код n — вектор прерывания, причем за каждым внутренним прерыванием и за внешним NMI жестко закреплялся свой вектор, а для запросов, поступивших по входу INTR, реализовывалась процедура ввода вектора с внешней шины. 11алее, определенный вектор прерывания рассматривался как номер строки таблицы, располагающейся с нулевого физического адреса памяти. Четырехбайтовыми элементами этой таблицы были адреса CS: IP точек входа в подпрограммы — обработчики прерываний. Таким образом, в системе поддерживалось до 256 различных обработчиков

прерываний, причем векторы 0 — 31 резервировались за внутренними прерываниями (и NMI), а остальные — для внешних прерываний.

При идентификации источника запроса INTR выполняются следующие действия (при условии, что флаг IF = 1, иначе запрос INTR игнорируется):

1.Генерируется два цикла шины для ввода вектора внешнего прерывания.

2.Помещается в стек содержимое регистра FLAGS.

3.Помещается в стек содержимое регистра CS. Д

4.Помещается в стек содержимое регистра IP.

5.Сбрасывается в 0 флаг разрешения внешних прерываний IF, запрещая восприятие новых запросов по входу INTR до явной установки флага IF в 1 командой STI.

6.По значению вектора n обращаются к n-му элементу таблицы векторов прерываний и из нее загружаются новые значения регистров CS: IP.

7.Начинается выполнения обработчика прерывания с точки входа, определяемой

CS: IP.

Сохраненное в стеке старое содержимое регистров CS: IP образует адрес возврата. Когда обработчик прерываний заканчивает свои действия, он должен выполнить команду возвратаIRET, которая, извлекая из стека содержимое FLAGS, CS, IP, возвращает управление прерванной программе.

Механизм реализации внешних и внутренних прерываний МП 80486 и Pentium в R- режиме аналогичен описанному выше, однако в P-режиме он значительно усовершенствован:

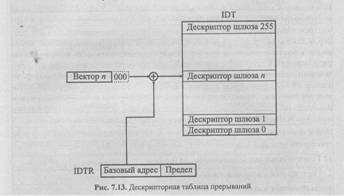

таблица векторов прерываний трансформирована в дескрипторную таблицу прерываний IDT (рис. 7.13);

более сложен процесс перехода к обработчику прерывания или особого случая;

Механизм передачи управления обработчику особого случая (прерывания) соответствует обычному способу передачи управления через шлюз вызова. При этом процессор аппаратно включает в стек значения EFLAGS, CS: EIP (адрес возврата) прерываемой программы и, кроме того, в некоторых случаях — код ошибки и текущие значения SS, ESP (последние — при смене привилегий).

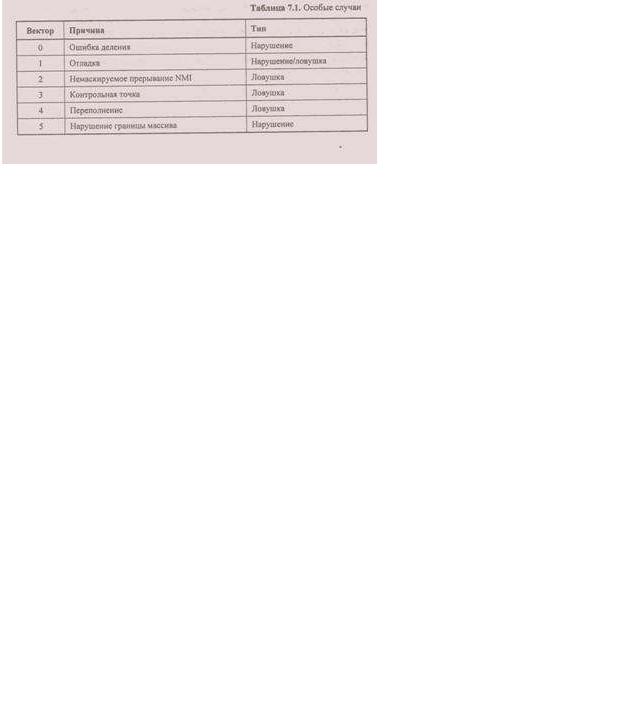

Точное значение адреса возврата зависит от того, является ли особый случай нарушением, ловушкой или аварией. Первые 32 вектора зарезервированы за особыми случаями P-режима (табл. 7.1).

5.1.2. Команди перериву за переповненням. Синтаксис команд.

Программные прерывания, вызываемые исполнением команды INT хх, по действиям процессора аналогичны дальним вызовам подпрограмм (сохранение в стеке адреса возврата — регистров CS и IP— и передача управления по указанному адресу), но имеют некоторые отличия.

В начале выполнения прерывания процессор помещает в стек регистр флагов и сбрасывает бит разрешения прерывания IF (Interrupt Flag).

Вместо адреса вызываемой подпрограммы аргументом вызова (хх) является номер вектора прерывания (0-255).

По окончании выполнения процедуры по инструкции IRET процессор извлекает из стека кроме адреса возврата (инструкции, следующей за INT) и сохраненное значение регистра флагов.

Сброс бита прерывания не позволяет прервать выполнение процедуры прерывания до ее окончания или явного разрешения командой El (Enable Interrupt). Само программное прерывание исполняется независимо от состояния флага IF. Программные прерывания позволяют легко и быстро вызывать общеупотребимые процедуры (сервисы BIOS и DOS) из любого сегмента без применения дальних вызовов. Прерывание INT 3 традиционно используется в целях отладки программ для создания точки останова, в отличие от остальных программных прерываний, оно вызывается однобайтной инструкцией (код 0CCh). Внутренние прерывания вырабатываются процессором по особым условиям

прерывание типа 0 вырабатывается в случае переполнения при операции деления на 0;

прерывание типа 1 вырабатывается после выполнения каждой команды при установленном флаге трассировки TF,

прерывание типа 4 вырабатывается по команде INTO (Interrrupt Overflow), если установлен флаг переполнения OF

5.1.3. Повернення з переривів та підпрограм.

Возврат из прерывания осуществляется по команде IRET, которая ставится в конце

обработчика прерывания. |

|

|

|

|

^ Операция |

прерывания осуществляется |

в |

следующем |

порядке: |

1)содержимое регистров Flags, CS и IP процессора (старое ССП) помещается в стек;

2)сбрасываются (обновляются) биты IF и TF регистра флагов (IF=0 - маскирует внешние прерывания по входу INTR, TF=0 - запрещает трассировку, т. е. шаговый режим);

3)определяется причина (номер N) прерывания с наивысшим в данный момент времени приоритетом (арбитраж);

4)по номеру N из таблицы извлекается вектор прерываний (из ячеек памяти с адресами 4N и 4N+2) и загружается в регистры CS, IP (новое значение ССП). Тем самым передается управление подпрограмме обработки прерывания.

Возврат из обработчика прерывания осуществляется командой IRET, по которой из стека в обратном порядке выталкиваются три слова (старое ССП) и загружаются в регистры IP, CS, Flags соответственно.

Возврат из подпрограммы осуществляется по команде IRET. При выталкивании из стека старого значения регистра флагов учитываются условия:

поле IOPL восстанавливается только при условии CPL=0,

флаг маски IF изменяется только при условии CPL≤IOPL.

5.1.4. Сегментна організація пам’яті.

Сегментная организация виртуальной памяти состоит в том, что программа разбивается на логические элементы (например, блоки, процедуры) ─ так называемые сегменты разной длины, которые размещаются в памяти как до определенной степени самостоятельная единица. Логически обращение к элементам программы будет представляться как указание имени сегмента и смещения относительно начала этого сегмента. Физическое имя сегмента (его порядковый номер) будет соответствовать некоторому адресу, с которого этот сегмент начинается при его размещении в памяти, и смещение должно прибавляться к этому базовому адресу. Таким образом, адрес для этого способа состоит из двух полей: номер сегмента и смещение относительно сегмента. Каждый сегмент, размещаемый в памяти, имеет соответствующую информационную структуру, называемую дескриптором сегмента:

Старшее двойное слово дескриптора

31 |

23 |

|

|

19 |

|

15 |

11 |

7 |

|

0 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

База сегмента |

|

G |

D |

0 |

0 |

Биты |

19-16 |

P |

DPL |

S |

Type |

A |

База сегмента |

|

(биты 31-24) |

|

|

|

|

|

поля Limit |

|

|

|

|

|

(биты 23-16) |

||

Базовый адрес сегмента (биты 15-0) |

Байт прав доступа |

|

||||||||||||

Limit-размер (предел) сегмента (биты 15-0) |

||||||||||||||

|

|

|

|

|

|

|

|

|||||||

31 |

|

|

|

|

|

|

15 |

|

|

|

|

|

0 |

|

Первое (младшее) двойное слово дескриптора |

|

|

|

|

|

|

||||||||

Рис.1. Дескриптор сегмента

При переключении микропроцессора в защищенный режим он начинает совершенно другим образом, чем в реальном режиме, вычислять физические адреса команд и операндов. Прежде всего, содержимое сегментных регистров интерпретируется иначе: считается, что там содержится не адрес начала сегмента, а номер соответствующего сегмента. Каждый сегментный регистр (в этом случае его называют селектор сегмента) разбивается на три поля:

a)поле индекса ─ старшие 13 битов (3-15). Определяют номер сегмента:

b)поле индикатора таблицы сегмента ─ бит с номером 2. Определяет часть виртуального адресного пространства.

c)поле уровня привилегий ─ биты 0 и 1. Указывает запрашиваемый уровень привилегий.

5.1.5. Фізична адреса байту в пам’яті.

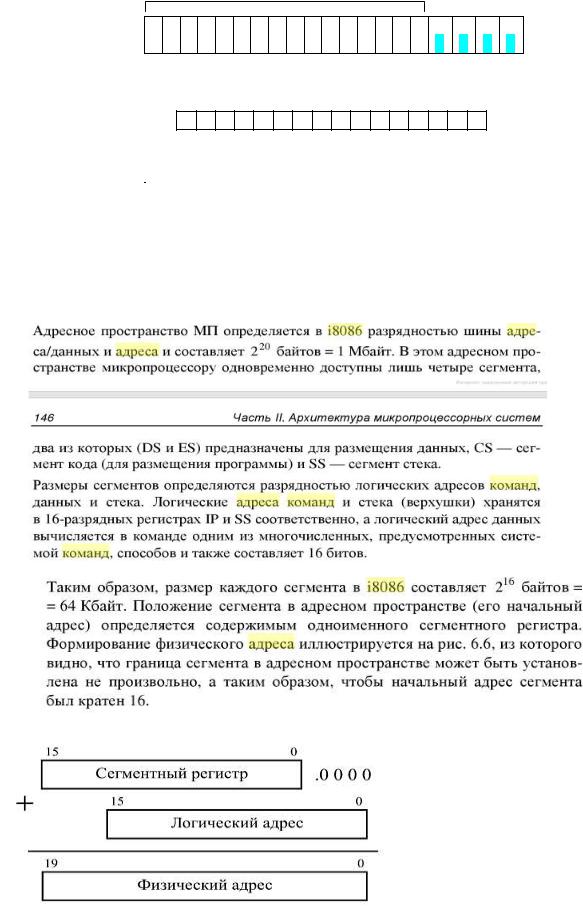

Так как внутренние регистры – 16-разрядные (216 = 64 Кбайт), а шина адреса имеет ширину 20 бит (220 = 1Мбайт), то для формирования 20-разрядного физического адреса памяти используются: сегмент адреса и смещение адреса. Физический адрес записывается парой этих значений, разделенных двоеточием, и образуется следующим образом (рис.4):

значение сегмента адреса, берущегося из регистра, CS сдвигается на 4 бита влево

сзаполнением разрядов справа нулями;

к образовавшемуся 20-битовому значению прибавляется значение смещения адреса из регистра IP. При возникновении переполнения берется только пять 16-ричных цифр результата.

Например, адрес 40:1Ch соответствует физическому адресу 0041Ch.

Значение регистра CS

Регистр CS

0 0 0 0

15 |

0 |

+

Регистр IP

=

Физический

адрес

15 |

0 |

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

19 |

|

|

0 |

|

|

|

||||||||||||||

Рис.4. Схема определения физического адреса для микропроцессоров 8086/88

5.1.6. Формування логічного адресу.

Тема 5.2: Сопроцесор і арифметичне розширення процесору. Синхронізація програми та керування таймером.

5.2.1. Функції та призначення сопроцесору.

Сопроцессор - специальная интегральная схема, которая работает в содружестве с главным процессором. Обычно сопроцессор настраивается на выполнение какой-нибудь специфические функции - математической операции или графического представления. И эту операцию сопроцессор может реализовать во много раз быстрее, чем главный процессор. Таким образом компьютеp с сопроцессором работает намного проворнее. Сопроцессор - это обычный микропроцессор, но не столь универсальный. Обычно сопроцессор разрабатывается как специальное устройство по реализации конкретно определенной функции. Он выполняет программы содержащие последовательность микpопpоцессоpных команд. Сопроцессоры, большей частью использующиеся в PC, являются математическими сопроцессорами. В математике они специализируются по умножению и делению чисел. Математические сопроцессоры называют ещѐ процессорами с плавающей запятой. Преимущество, получаемое от установки математического сопроцессора, зависит от того какие задачи решаются на компьютере. Сопроцессор может уменьшить время выполнения математических операций, таких как умножение, деление, возведение в степень на 80% и более. Сопроцессор и главный микропроцессор могут работать на разных тактовых частотах (от собственных тактовых генераторов). Когда отношение частот микропроцессора и сопроцессора выражается целым числом, они работают синхронно и могут передавать информацию друг другу оптимальным образом. Несинхронизированная работа требует, чтобы один или другой из них ожидал завершения цикла своего партнѐра, что влечѐт за со бой появление небольшого, но реального периода ожидания. Семейство сопроцессоров Intel составляют: 8087, 80287, 80387, 80387SX. Как правило сопроцессоры работают как придатки центрального. Сопроцессоры могут выполнять свои функции параллельно с работой центрального процессора, то есть оба мозга в данном случае думают одновременно, потому что каждый из них читает свои команды прямо с шины, и центральному процессору не приходится прерываться, чтобы выдать команду сопроцессору.

Сопроцессор — специализированный процессор, расширяющий возможности центрального процессора компьютерной системы, но оформленный как отдельный функциональный модуль. Физически сопроцессор может быть отдельной микросхемой или может быть встроен в центральный процессор (как это делается в случае математического сопроцессора в процессорах для ПК начиная с Intel 486DX).

Различают следующие виды сопроцессоров:

математические сопроцессоры общего назначения, обычно ускоряющие вычисления с плавающей запятой,

сопроцессоры ввода-вывода (например — Intel 8089), разгружающие центральный процессор от контроля за операциями ввода-вывода или расширяющие стандартное адресное пространство процессора,

сопроцессоры для выполнения каких-либо узкоспециализированных вычислений. Сопроцессоры могут входить в набор логики, разработанный одной конкретной фирмой (например Intel выпускала в комплекте с процессором 8086 сопроцессоры 8087 и 8089)

или |

выпускаться |

сторонним |

производителем |

(например, Weitek (англ.) 1064 для Motorola m68k и 1067 для Intel 80286). |

|

||

5.2.2. Призначення арифметичного розширення процесору.

Вместе с любыми процессорами фирмы Intel (и их аналогами) могут использоваться сопроцессоры. Они выполняют операции с плавающей запятой, которые

потребовали бы больших затрат машинного времени от основного процессора. Выигрыш можно получить только при выполнении программ, написанных с расчетом на использование сопроцессора. Сопроцессоры выполняют такие сложные операции как точное деление, вычисление тригонометрических функций, извлечение квадратного корня и нахождение логарифма в 10-100 раз быстрее основного процессора. Точность результатов при этом значительно выше той, которая обеспечивается вычислителями, входящими в состав самих процессоров. Операции сложения, вычитания и умножения выполняются основным процессором и не передаются сопроцессору. Система команд сопроцессора отличается от системы команд процессора. Выполняемая программа должна сама определять наличие сопроцессора и после этого выполнять написанные для него инструкции, в противном случае сопроцессор только потребляет ток и ничего не делает. Большинство современных программ, рассчитанных на использование сопроцессора, обнаруживает его присутствие и использует предоставленные возможности. Наиболее эффективно сопроцессоры используются в программах со сложными математическими расчетами: в электронных таблицах, базах данных, статистических программах, системах автоматизированного проектирования. В работе с текстовыми редакторами сопроцессор совершенно не используется. Фирма Intel выпускает следующие сопроцессоры: 8087, 287, 387SX, 387DX, 487SX на отдельных кристаллах, а начиная с процессора 486DX сопроцессоры встроены в микросхему процессора.

5.2.3. Функції та призначення таймеру.

В якості системного таймера комп'ютера використовується мікросхема трьохканального 16-розрядного таймера i8254 чи її аналог. Таймер призначений для одержання програмно керованих часових затримок і генерації сигналів заданої частоти. Таймер дозволяє підвищити ефективність програмування процесів управління і синхронізації зовнішніх пристроїв, особливо в реальному часі.

Таймер містить три незалежних канали (0, 1 і 2), кожний з яких може бути, у принципі, запрограмований на роботу в одному із шести режимів відліку:

переривання термінального відліку;

програмований генератор одиночного імпульсу;

генератор імпульсів заданої частоти;

генератор прямокутних імпульсів типу "меандр";

програмно формований строб;

апаратно формований строб.

5.2.4. Синхронізація сигналів таймеру.

На кожен канал можуть подаватися вхідні синхросигнали. З кожного каналу можна одержувати сигнал з частотою, яка рівна вхідній частоті, що поділена на довільне 16розрядне число. У комп'ютері на усі входи надходять синхросигнали з частотою 1,19 Мгц. Усі канали таймера в комп'ютері мають спеціальне призначення, тому особливих можливостей щодо вибору режиму роботи чи перепризначення функцій у користувача немає.

Вихід каналу 0 зв'язаний із сигналом запиту переривання IRQ0 і забезпечує переривання для лічильника реального часу (використовується режим роботи 3). Користувачу не рекомендується перепрограмувати цей канал. При старті комп'ютера канал програмується так, щоб видавати імпульси приблизно 18,2 рази в секунду. За цим перериванням програмно збільшується стан лічильника реального часу. Користувач може читати стан даного лічильника зі спеціально виділеної комірки пам'яті і застосовувати його для затримок у своїх програмах.

Вихід каналу 1 генерує сигнал запиту регенерації динамічної пам'яті (режим роботи 2). Використання цього каналу не за призначенням може викликати до утрати вмісту оперативної пам'яті.

Вихід каналу 2 генерує тональний сигнал для вмонтованого динаміка комп'ютера (режим роботи 3). Однак дозвіл цього тонального сигналу відбувається установкою виділених розрядів (0 і 1) програмно доступного паралельного порту контролера периферійних пристроїв. Один розряд (0) дозволяє роботу каналу, інший розряд (1) пропускає вихідний сигнал на динамік.

Таким чином, користувач комп'ютера може задіяти тільки канал 2. Найчастіше його застосовують для генерації звуків заданої частоти і тривалості. Крім того, вихідний сигнал даного каналу програмно доступний для читання з одного з розрядів паралельного порту. Це дозволяє, запрограмувавши таймер відповідним чином, витримувати потрібні часові інтервали. Для цього варто програмно дозволити генерацію (при відключеному динаміку), а потім програмно опитувати вихідний сигнал таймера і приймати рішення щодо зміни його рівня.

Тема 5.3: Програмування вводу/виводу даних на зовнішні пристрої. Обмін даними в локальних мережах.

5.3.1. Функції інтерфейсу вводу/виводу.

Ввід/вивід, введення-виведення (англ. I/O, input/output) в інформатиці — взаємодія між обробником інформації (наприклад, комп'ютер) і зовнішнім світом, який може представляти як людина, так і будь-яка інша система обробки інформації. Введення, ввід

— сигнал або дані, отримані системою, а вивід — сигнал або дані, надіслані нею (або з неї). Термін також може використовуватися як позначення (або доповнення до позначення) певної дії: «виконувати введення / виведення» означає виконання операцій введення або виведення. Пристрої введення-виведення використовуються людиною (або іншою системою) для взаємодії з комп'ютером. Наприклад, клавіатури і миші — спеціально розроблені комп'ютерні пристрої введення, а монітори та принтери — комп'ютерні пристрої виводу. Пристрої для взаємодії між комп'ютерами, як модеми та мережеві карти, зазвичай служать пристроями введення і виведення одночасно.

Варто відзначити, що призначення пристрою як пристрою введення або виведення залежить від перспективи. Миші та клавіатури приймають фізичну дію, здійснювану людиною-користувачем (до речі, щодо нього це будуть дії з виведення інформації), і перетворює його в сигнали, зрозумілі комп'ютеру. Виведення інформації з цих пристроїв є введенням її в комп'ютер. Аналогічно, принтери та монітори отримують на вході сигнали, які виводить комп'ютер. Потім вони перетворять ці сигнали в такий вигляд, який людина зможе побачити чи прочитати. Для людей-користувачів процес читання або перегляду подібних варіантів представлення інформації є введенням або отриманням інформації.

У комп'ютерній архітектурі об'єднання процесора і основної пам'яті (тобто пам'яті, з якої процесор може читати і записувати в неї прямо за допомогою особливих інструкцій) становить «мозок» комп'ютера, і з цієї точки зору, будь-який обмін інформацією з цим об'єднанням, наприклад, з дисковим накопичувачем, має на увазі введення-виведення. Процесор і його супутні електронні кола реалізують введення-виведення з розподілом пам'яті, використовувані в низькорівневому програмуванні при реалізації драйверів пристроїв.

Високорівнева операційна система і програмне забезпечення використовують інші, більш абстрактні концепції і примітиви введення-виведення. Наприклад, більшість операційних систем реалізують прикладні програми через концепцію файлів. Мови програмування Сі та C++, а також операційні системи сімейства Unix, традиційно абстрагують файли і пристрої у вигляді потоків даних, з яких можна читати і в які можна записувати, або і те й інше разом. Стандартна бібліотека мови Сі реалізує функції для роботи з потоками для введення і виведення даних.

Інтерфейс вводу-виводу