Микропроцесоры_Ответы

.pdf

Інтерфейс вводу-виводу вимагає управління процесором кожного пристрою. Інтерфейс повинен мати відповідну логіку для інтерпретації адреси пристрою, що генерується процесором.Встановлення контакту повинно бути реалізовано інтерфейсом за допомогою відповідних команд типу (ЗАЙНЯТИЙ, ГОТОВИЙ, ЖДУ), щоб процесор міг взаємодіяти з пристроєм вводу-виводу через інтерфейс.Якщо існує необхідність передачі розрізнених форматів даних, то інтерфейс повинен вміти конвертувати послідовні (впорядковані) дані в паралельну форму і навпаки.

Повинна бути можливість для генерації переривань і відповідних типів чисел для подальшої обробки процесором (за потреби).Комп'ютер, що використовує введеннявиведення з розподілом пам'яті, звертається до апаратного забезпечення за допомогою читання і запису в певні осередки пам'яті, використовуючи ті ж самі інструкції мови асемблера, які комп'ютер зазвичай використовує при зверненні до пам'яті.

5.3.2. Керування обміном даними. Програмний обмін.

Програмний обмін інформацією є основним у будь-якій мікропроцесорній системі. Він передбачений завжди, без нього неможливі інші режими обміну. У цьому режимі процесор є одноособовим хазяїном (або задатчиком, Master) системної магістралі. Всі операції (цикли) обміну інформацією в даному випадку ініціюються тільки процесором, усі вони виконуються строго в порядку, запропонованому програмою, яка виконується.

Процесор читає (вибирає) з пам'яті коди команд і виконує їх, читаючи дані з пам'яті або з пристрою вводу/виводу, обробляючи їх, записуючи дані в пам'ять або передаючи їх у пристрій вводу/виводу. Шлях процесора по програмі може бути лінійним, циклічним, може містити переходи (стрибки), але він завжди безупинний і цілком знаходиться під контролем процесора. Ні на які зовнішні події, не зв'язані з програмою, процесор не реагує (Рис. 1.11). Усі сигнали на магістралі в даному випадку контролюються процесором.

5.3.3. Керування обміном даними. Обмін за переривом.

Обмін з використанням переривань використовується тоді, коли необхідна реакція мікропроцесорної системи на якусь зовнішню подію, на прихід зовнішнього сигналу. У випадку комп'ютера зовнішньою подією може бути, наприклад, натискання на клавіші клавіатури або прихід локальною мережею пакета даних. Комп'ютер повинен реагувати на це, відповідно, виведенням символу на екран або ж читання й обробкою прийнятого з мережі пакета.

У загальному випадку організувати реакцію на зовнішню подію можна трьома різними шляхами:

за допомогою постійного програмного контролю факту настання події (так званий метод опитування прапора або polling);

за допомогою переривання, тобто насильного переведення процесора з виконання поточної програми на виконання негайно необхідної програми;

за допомогою прямого доступу до пам'яті, тобто без участі процесора при його

відключенні від системної магістралі.

Проілюструвати ці три способи можна наступним простим прикладом. Допустимо, ви готуєте собі сніданок, поставивши на плиту кип'ятитися молоко. Природно, на закипання молока треба реагувати, причому терміново. Як це організувати? Перший шлях - постійно стежити за молоком, але тоді ви нічого іншого робити не зможете. Вірніше буде регулярно поглядати на молоко, роблячи одночасно щось інше. Це програмний режим з опитуванням прапора. Другий шлях - установити на каструлю з молоком датчик, що подасть звуковий сигнал при закипанні молока, і спокійно займатися іншими справами. Почувши сигнал, ви знімете з плити молоко. Правда, можливо, вам доведеться спочатку закінчити те, що ви почали робити, так що ваша реакція буде повільнішою, ніж у першому випадку. Нарешті, третій шлях полягає в тому, щоб з'єднати датчик на каструлі з керуванням плитою так, щоб при закипанні молока пальник був вимкнений без вашої участі (правда, аналогія з ПДП тут не дуже точна, тому що в даному випадку на момент виконання дії вас не відволікають від роботи).

Перший випадок з опитуванням прапора реалізується в мікропроцесорній системі постійним читанням інформації процесором із пристрою вводу/виводу, який зв'язаний з тим зовнішнім пристроєм, на поведінку якого необхідно терміново реагувати.

В другому випадку в режимі переривання процесор, отримавши запит переривання від зовнішнього пристрою (часто званий IRQ - Interrupt ReQuest), закінчує виконання поточної команди і переходить до програми обробки переривання. Закінчивши виконання програми обробки переривання, він повертається до перерваної програми з того місця, де його перервали (Рис. 1.12).

Тут важливим є те, що вся робота, як і у випадку програмного режиму, здійснюється самим процесором, зовнішня подія просто тимчасово відволікає його від виконання програми. Реакція на зовнішню подію по перериванню, в загальному випадку, повільніша, ніж при програмному режимі. Як і у випадку програмного обміну, тут усі сигнали на магістралі виставляються процесором, тобто він цілком контролює магістраль. Для обслуговування переривань у систему іноді вводиться спеціальний модуль контролера переривань, але він в обміні інформацією участі не бере. Його завдання полягає в тому, щоб спростити роботу процесора з зовнішніми запитами переривань. Цей контролер, зазвичай, програмно керується процесором системною магістраллю.

Рис. 1.12. Обслуговування переривання.

Природно, ніякого прискорення роботи системи переривання не дає. Його застосування дозволяє тільки відмовитися від постійного опитування прапора зовнішньої події і тимчасово, до її настання, зайняти процесор виконанням якихось інших задач.

Тема 6.1: Архітектура мікроконтролеру i8086. Організація пам’яті і регістрів. Прямий доступ до пам’яті.

6.1.1. Організація пам’яті. Адресний простір.

Данный микроконтроллер имеет встроенную (резидентную) и внешнюю память программ и данных. Резидентная память программ (RPM) имеет объем 4 Кбайт, резидентная память данных (RDM) — 128 байт.

В зависимости от модификации микроконтроллера RPM выполняется в виде масочного ПЗУ, однократно программируемого либо репрограммируемого ПЗУ.

При необходимости пользователь может расширять память программ установкой внешнего ПЗУ. Доступ к внутреннему или внешнему ПЗУ определяется значением сигнала на выводе ЕА (External Access):ЕА = V'cc (напряжение питания) — доступ к внутреннему ПЗУ: ЕА = Vss (потенциал земли) — доступ к внешнему ПЗУ.

Внешняя память программ и данных может составлять по 64 Кбайт и адресоваться с помощью портов РО и Р2. На рис. 2 представлена карта памяти микроконтроллера Intel

8051.

Рис. 2 Организации памяти Intel 8051

Строб чтения внешнего ПЗУ — PSEN (Program Store Enable) генерируется при обращении к внешней памяти программ и является неактивным во время обращения к ПЗУ. расположенному на кристалле.

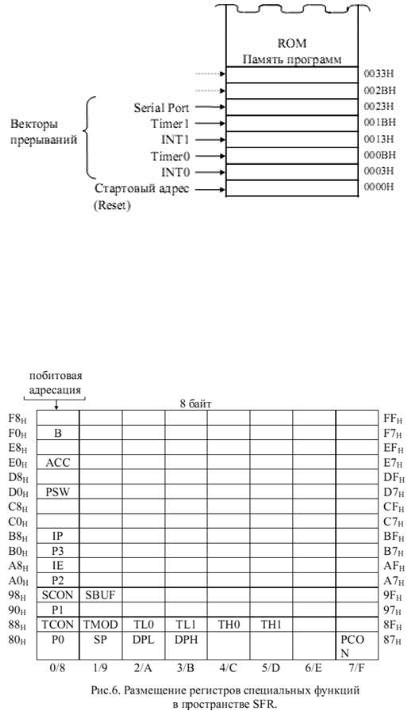

Область нижних адресов памяти программ (рис. 3) используется системой прерываний. Архитектура микросхемы INTEL 8051 обеспечивает поддержку пяти источников прерываний. Адреса, по которым передается управление по прерыванию, называются векторами прерывания.

Рис. 3 Карта нижней области программной памяти

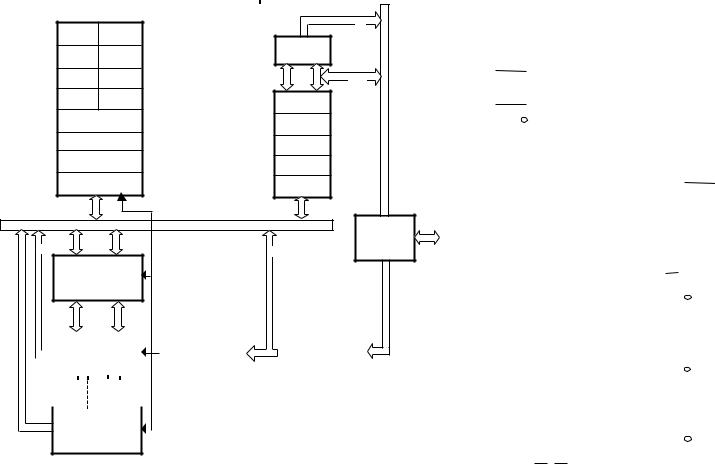

Верхняя 128 байтная половина памяти ОЗУ (upper 128) в микросхеме 1-8051 отсутствует, но имеется в версиях кристаллов с 256 байтами ОЗУ. В этом случае область "Upper 128" доступна только при косвенной адресации. Область SFR (Special Function Register) доступна только при прямой адресации. Размещение регистров специальных функций в пространстве SFR показано на рис.6. Они включают в себя регистры портов, таймеры, средства управления периферией и так далее.

Адресное пространство ЗУ – это совокупность ячеек памяти, к которым можно обращаться с использованием абсолютного адреса.

Абсолютный адрес однозначно определяет номер ячейки памяти в пространстве адресов. Адресное пространство памяти МП можно считать прямоугольной областью, разбитой на множество строк, соответствующих адресам. При разрядности шины адреса равной n, адресное пространство составляет 2n адресов.

Адресное пространство должно быть распределено между ПЗУ и ОЗУ таким образом, чтобы исключить их взаимное перекрытие. В ряде случаев под ПЗУ выделяется адресное пространство в области меньших адресов.

При разрядности шины адреса микросхемы ПЗУ равной k, ПЗУ занимает адресное пространство размером 2k. В свою очередь ОЗУ с разрядностью шины адреса j занимает в адресном пространстве область размером 2j. Распределение адресного пространства будет выполнено без перекрытия, если начальный адрес ОЗУ будет больше конечного адреса ПЗУ (см. рис. 3.4.).

Соотношение между k и j, а следовательно и емкостью ПЗУ и ОЗУ, определяется назначением и функциями МПС. Так, в персональном компьютере ПЗУ используется для хранения базовой системы ввода-вывода BIOS и размер программы BIOS определяет емкость ПЗУ (около 4 Кбайт), а емкость ОЗУ составляет не менее 640 Кбайт. С другой стороны, в микроконтроллерах MCS-51 объем ПЗУ (памяти программ) составляет 4–32 Кбайт, а ОЗУ – 128–256 байт.

Адресное пространство ЗУ

|

|

k |

Начальный адрес ПЗУ |

|

|

|

|||

|

|

|

||

|

ПЗУ |

2 |

Конечный адрес ПЗУ |

|

n |

|

j |

Начальный адрес ОЗУ |

|

ОЗУ |

||||

2 |

2 |

|

||

|

|

|||

|

|

|

Конечный адрес ОЗУ |

Рис. 3.4. Распределение адресного пространства ЗУ

6.1.2. Структура процесору i8086. Виконавчий модуль.

Упрощенная структурная схема МП Intel 8086 и его условное обозначение представлены на рис. 2.2.

|

|

|

|

МА(20) |

|

AH |

AL |

AX |

|

МД(16) |

|

BH |

BL |

BX |

|||

|

|

||||

CH |

CL |

CX |

|

|

|

DH |

DL |

DX |

CS |

|

|

|

|

|

|

||

|

SP |

|

DS |

|

|

|

BP |

|

SS |

|

|

|

|

|

|

||

|

DI |

|

ES |

|

|

|

|

|

|

||

|

SI |

|

IP |

|

|

|

|

Магистраль АЛУ |

|

|

|

|

|

|

|

Цепи |

|

|

|

|

|

управления |

|

Предварительные . |

|

|

|

||

регистры |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

Конвейер команд |

|

||||||

|

|

|

|

|

|

. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

АЛУ |

|

Управление |

|

|

|

1 |

2 |

3 |

4 |

5 |

6 |

|

|

||

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

EU |

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Флаги |

|

|

|

|

|

а) |

|

||||||||

управления

Внешние

магистрали

МП

|

|

|

|

|

GND |

|

|

|

|

AD0 |

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

AD1 |

|

|

|

|

|

|||||||||

|

|

|

|

|

Ucc |

CPU |

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

AD2 |

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

CLK |

|

|

|

AD3 |

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

AD4 |

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

MN/MX |

|

|

|

|

AD5 |

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

AD6 |

|

|

|

|

|

|||||||||

|

|

|

|

|

RDY |

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

AD7 |

|

|

|

|

|

|||||||||

|

|

|

|

|

TEST |

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

AD8 |

|

|

|

|

|

|||||||||||||

|

|

|

|

|

INT |

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

AD9 |

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

NMI |

|

|

|

|

AD10 |

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

AD11 |

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

AD12 |

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

AD13 |

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

AD14 |

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

AD15 |

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A15/ST3 |

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

A16/ST4 |

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

A18/ST5 |

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

A19/ST6 |

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

HLDA |

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

R1/E1 |

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

W |

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LOCK |

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

M/IO |

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

ST2 |

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

OP/IP |

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

ST1 |

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

DE |

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

ST0 |

|

|

|

|

|

|||||||||||

|

|

б) |

|

|

|

|

|

|

STB |

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

QS0 |

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

INTA |

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

QS1 |

|

|

|

|

|

|||||||||||

|

|

|

|

|

CLR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

R |

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

HLD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

BHE |

|

|

|

|

|

||||||||||||||||

|

|

|

|

R0/E0 |

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

ST7 |

|

|

|

|

|

||||||||||||||||

Рис. 2.1. Упрощенная структурная схема МП Intel 8086 (а) и его условное обозначение (б)

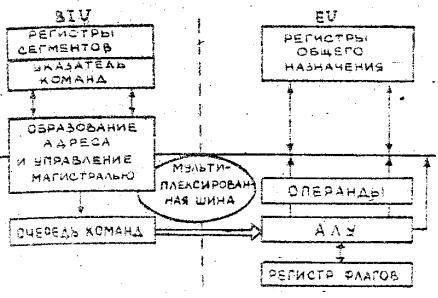

Микропроцессор включает два основных асинхронно работающих устройства: блок выполнения команд (Execution Unit) и блок сопряжения с шиной (Bus Interface Unit). В функции блока выполнения команд входит декодирование и выполнение команд, а в функции блока сопряжения с шиной - извлечение из памяти кода команд и их операндов, а также запись результатов в память. Блоки могут работать независимо друг от друга, и процессы преобразования и передачи информации в них могут идти параллельно.

Функционально микросхема разделена на два независимых блока. дин из них называется блоком сопряжения с магистралью (рис.1.3)

(Bus interface unit BIU), другой блок называется исполнительным (Execution unit EU).Блок сопряжения с магистралью выполняет две функции:

-выборка команд из памяти;

-пересылка данных между исполнительной аппаратурой и внешним миром.

Рис.3.1. Функциональная архитектура МП 8086/8088

В исполнительном блоке происходит выполнение команды. BIU содержит указатель команд (IP), в котором хранится адрес очередной выбираемой команды, байтовая очередь потока команд и регистры сегментов.

Регистры сегментов МП 8086/8088 содержат 16 разрядов и носят название CS (code segment – сегмент программы), DS (date segment сегмент данных), SS (stack segment –

сегмент стека) и ES (extra segment – дополнительный сегмент).

Блоки BIU и EU работают независимо. Блок BIU осуществляет выборку команд и пересылку данных, а EU выполняет выбранные команды. Такое разделение функций стало возможным за счет использования конвейера (очереди) команд. Блок сопряжения с магистралью заполняет конвейер командами, ожидающими выполнения. В то время как исполнительный блок заканчивает выполнение текущей команды, следующая команда уже подготовлена для выполнения. В случае перехода конвейер сбрасывается. Конвейер BIU в МП 8086 хранит до 6 байт, а 8088до 4 байт потока команд.

Исполнительный блок не имеет связи с системной магистралью. ЕU получает команда из очереди. Если команда требует обращения к памяти или внешней магистрали, EU посылает запрос ВIU на выборку или запись данных. Адреса, с которыми оперирует EU имеет 16 разрядов, но BIUвыполняет преобразование адресов так, чтобы EU мог обратиться ко всему возможному адресному пространству (1Мбайт) памяти

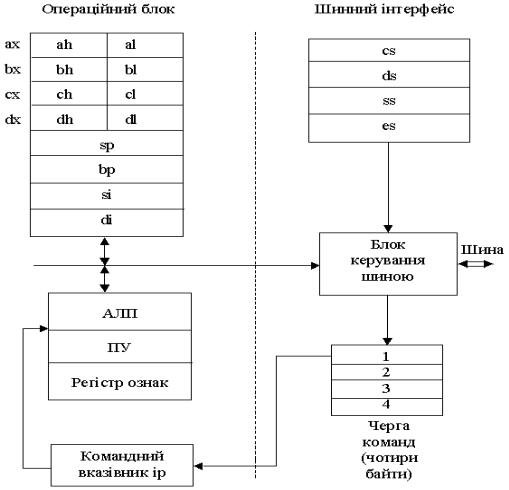

Исполнительный блок состоит из 16-разрядного арифметико-логического устройства (АЛУ), регистров, операндов и флагов, а также набора регистров общего

назначения |

Н, L, ВН, BL, СН, CL, DН, DL. Регистры |

Н и AL объединяются в регистр- |

аккумулятор |

Х; ВН и BL образуют регистр базы |

ВХ; СН и CL образуют регистр- |

счетчик СХ. DН и DL образуют регистр данных DX.

К регистрам общего назначения можно адресоваться как к 8- или 16-разрядным. Это позволяет программам для 8-разрядного МП 8080 выполняться на МП 8086/8088 после повторной трансляции. МП 8086/8088 может адресовать до 1 Мбайта памяти (1048576 байт). Каждому адресу назначен уникальный адрес (беззнаковое число от 0 до 2020- 1 (от 00 000 до FFFFF в шестнадцатеричной системе счисления). Два соседних байта в памяти образуют слово. За адрес слова принимается меньший из двух адресов байтов, слово состоит из 16 бит. Младшие биты слова содержатся в адресе байта с меньшим адресом, а старшие биты слова - в байте со старшим адресом.

В МП-8086 обмен данными между процессором и памятью осуществляется словами, начинающимися с адресов, кратных двум.

Кроме байт и слов МП 8086/8088 оперирует следующими дополнительными типами данных:

1.Неупакованный двоично-десятичный тип - байтовое представление .десятичной цифры от 0 до 9.

2.В каждом байте хранится по одной цифре. Значение цифры определяется младшим полубайтом. Старший полубайт равен 0 при делении и умножении и принимает любое значение при вычитании и сложении.

3.Ближний указатель - 16-разрядный логический адрес, который представляет собой относительный адрес внутри сегмента.

4.Дальний указатель-- 32-разрядный логический адрес из двух компонентов 16разрядного сегмента и 16-разрядного относительного адреса.

5.Целый тип - знаковое двоичное значение, содержащееся в 16-разрядном слове или 8- разрядном байте. Все операции выполняются в дополнительном коде. Бит знака расположен в бите 7 байта и в бите 15 слова. Знаковый бит равен 0 для положительного слова и в равен 1 - для отрицательного. Для 8-разрядных целых чисел диапазон изменения от -128 до +127,. а 16-разрядных в диапазоне от -32768 до +32767. Нулевое значение имеет положительный знак.

6.Обычный (беззнаковый) тип -беззнаковое двоичное значение содержащееся в 16разрядном слове или 8-разрядном байте. Все биты определяют величину числа. Значение для байта составляет от 0 до 255, для слова - от 0 до 65535.

7.Строка - непрерывная последовательность байт или слов. Строка может содержать от 0 до 216 - 1 байт или 64 Кбайта.

6.1.3. Структура процесору i8086. Шиний інтерфейс

инный интерфейс выполняет для операционного устройства все операции обмена. Данные передаются между процессором и памятью или портами ввода-вывода по запросам операционного устройства. Когда операционное устройство занято выполнением команды, шинный интерфейс самостоятельно инициирует опережающую выборку из памяти очередных команд. Команды хранятся во внутренней регистровой памяти, называемой очередью (буфером) команд. Очередь команд выполняет по существу функции регистра команды процессора. Длина очереди составляет 6 байт. Очередь команд работает по принципу FIFO ("первым пришел, первым вышел"), который сохраняет на выходе порядок поступления команд.

Шинный интерфейс инициирует выборку из памяти следующего командного слова, когда в очереди оказываются два свободных (пустых) байта. В большинстве случаев очередь команд содержит минимум один байт потока команд, и операционное устройство не ожидает выборки команды. Конечно, очередь обеспечивает положительный эффект при естественном порядке выполнения команд. Когда операционное устройство выполняет команду передачи управления, шинный интерфейс сбрасывает очередь, выбирает команду по новому адресу, передает ее в операционное устройство, а затем начинает заполнение очереди из следующихячеек. Эти действия выполняются при условных и безусловных переходах, вызовах подпрограмм, возвратах из подпрограмм и при обработке прерываний. Шинный интерфейс приостанавливает выборку команд, когда операционное устройство запрашивает операцию считывания или записи в память или порт ввода-вывода. В состав шинного интерфейса входят несколько регистров и сумматор, которые формируют 20-разрядный физический адрес памяти из двух 16разрядных логических адресов: сегмента (базы) и смещения.

При готовности операционного устройства выполнять команду оно считывает из очереди байт, а затем выполняет предписанную командой операцию. При многобайтных командах из очереди считываются и другие байты команды. Когда операционное устройство готово считать командный байт, а очередь команд пуста, оно ожидает выборки командного слова из памяти программ, которую производит шинный интерфейс. Если

команда требует обращения к памяти или порту ввода-вывода, операционное устройство запрашивает шинный интерфейс на выполнение необходимого цикла шины. Когда шинный интерфейс не занят выборкой команды, он удовлетворяет запрос немедленно; в противном случае операционное устройство ожидает завершения текущего цикла шины.

6.1.4. Структура процесору i8086. Керування і таймінг.

Пристрій керування реалізує тимчасову діаграму і виробляє необхідні керуючі сигнали для внутрішньої роботи мікропроцесора й зв'язку його з іншою апаратурою через зовнішні шини мікропроцесора.

В i8086 имеется возможность изменения внутренней аппаратной конфигурации с помощью специального управляющего сигнала. В более простом режиме 8086 ориентирован на использование в простых вычислительных и управляющих устройствах. При этом микропроцессор сам вырабатывает сигналы управления шиной и обеспечивает прямой доступ к ней посредством контроллера Intel 8257. В режиме полной конфигурации обеспечивается работа с контроллером шины 8288, который декодирует три сигнала состояния процессора и в зависимости от них выдает семь сигналов управления шиной. Такой режим используется в мультипроцессорных системах и в сложных вычислительных устройствах, в частности, в компьютере IBM PC/XT.

Интересно организована память: хранение 16-разрядных слов осуществляется в виде отдельных байтов, причем байты, передающиеся по восьми младшим линиям шины данных (D7-D0), собраны в банк 0, а передаваемые по восьми старшим линиям — в банк 1. Объем каждого банка составляет 512 Кбайт. Таким образом, нечетные байты хранятся в банке 1, а четные. — в банке 0. Выбор банка осуществляется с помощью младшего адреса и сигнала управления старшими разрядами шины данных.