Микропроцесоры_Ответы

.pdf

Еще одна важная особенность — возможность обработки 256 типов прерываний (от 0 до 255), в том числе есть прерывания, определяемые пользователем, и пошаговые прерывания.

Микропроцессор Intel 8086 приспособлен для работы с несколькими процессорами в одной системе, причем возможно использование как независимых процессоров, так и сопроцессоров. Отличие заключается в том, что независимый процессор выполняет свою собственную последовательность команд, а сопроцессор следит за потоком команд центрального процессора и выделяет из него "свои" команды, расширяя набор команд основного процессора и улучшая таким образом характеристики системы. Для поддержки этих режимов используются команды ESC, LOCK и XCHG, а также специальные управляющие сигналы, позволяющие разрешать конфликты доступа к общим ресурсам.

Внешние шины адреса и данных в 8086 объединены, и поэтому наличие на шине в данный момент времени информации или адреса определяется порядковым номером такта внутри цикла. Процессор ориентирован на параллельное выполнение команды и выборки следующей команды. В целом выполнение команды происходит примерно так же, как и в 8080. Команда выбирается из памяти и принимается микропроцессором в свободный регистр очереди команд, причем в то же самое время выполняется предыдущая команда. Конвейеризация команд позволяет значительно повысить быстродействие системы. При выполнении команд проверяются состояния входов запросов прерываний и захвата шины, и при необходимости выполняются соответствующие действия.

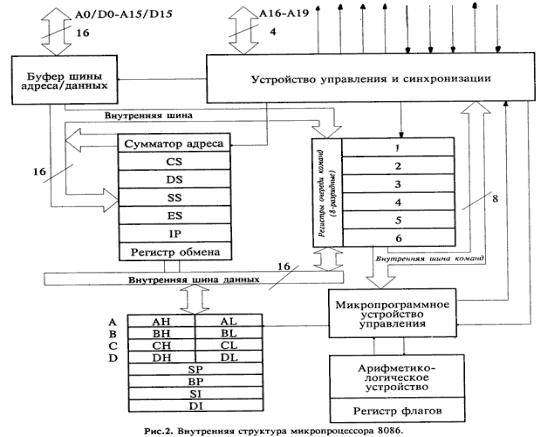

Микропроцессор i8086 состоит из трех основных частей: устройства сопряжения шины, устройства обработки и устройства управления и синхронизации.

Устройство сопряжения шины состоит из шести 8-разрядных регистров очереди команд, четырех 16-разрядных регистров адреса команды, 16-разрядного регистра команды и 16-разрядного сумматора адреса (см. рис. 2). Оно выполняет следующие функции: выбирает команды из памяти и записывает их в регистр очереди команд, вычисляет и формирует физический адрес, читает операнды из памяти или из регистров и записывает результат выполнения команд в память или в регистры.

Варто відмітити, що оперативна пам'ять не може працювати із нескінченною швидкістю, як, втім, і ніщо інше. На виконання будь-яких операцій їй потрібний час. На щось – більше, на щось – менше. Називається цей час по-англійськи timings, тобто таймінги або затримки. Вони задаються в тактах шини пам'яті. Звідси може стати ясно, чому зростають таймінги із кожним поколінням DDR – частота чіпа практично не міняється, отже, і час виконання ним операцій – теж, натомість частота шини міняється в рази. А тому і час одного такту зменшується. Тобто за час виконання команди в наносекундах більш високочастотна шина встигає «натикати» більше, тому більше тактів їй доводиться чекати. Але абсолютні значення затримок не зростають. На максимальну продуктивність пам'яті впливає такий важливий параметр як "таймінги пам'яті".

Відомо, що логічна структура банку пам'яті є двовимірним масивом - простою матрицею, кожна комірка якої має свою адресу, номер рядка і номер стовпця. Щоб зчитати вміст довільної комірки масиву, контролер пам'яті повинен задати номер рядка

RAS (RowAdressStrobe) і номер стовпця CAS (ColumnAdressStrobe), із яких і прочитуються дані. Зрозуміло, що між подачею команди і її виконанням завжди буде якась затримка (латентність пам'яті), ось її-то і характеризують ці самі таймінги. Існує безліч різних параметрів, які визначають таймінги, але найчастіше використовуються чотири із них:

CAS Latency(CAS) - затримка в тактах між подачею сигналу CAS і безпосередньо видачею даних із відповідної комірки. Одна з найважливіших характеристик будьякого модуля пам'яті;

RAS to CAS Delay (tRCD) - кількість тактів шини пам'яті, які повинні минути після подачі сигналу RAS до того, як можна буде подати сигнал CAS;

RowPrecharge (tRP) - час закриття сторінки пам'яті в межах одного банку, що витрачається на його перезарядку;

ActivatetoPrecharge (tRAS) - час активності строба. Мінімальна кількість циклів між командою активації (RAS) і командою заряджання (Precharge), яким закінчується робота із цим рядком, або закриття одного і того ж банку.

Якщо ви побачите на модулях позначення "2-2-2-5" або "3-4-4-7", можете не сумніватися, це згадані вище параметри: CAS-tRCD-tRP-tRAS.

6.1.5. Контролер динамічної пам'яті. Схема модуля.

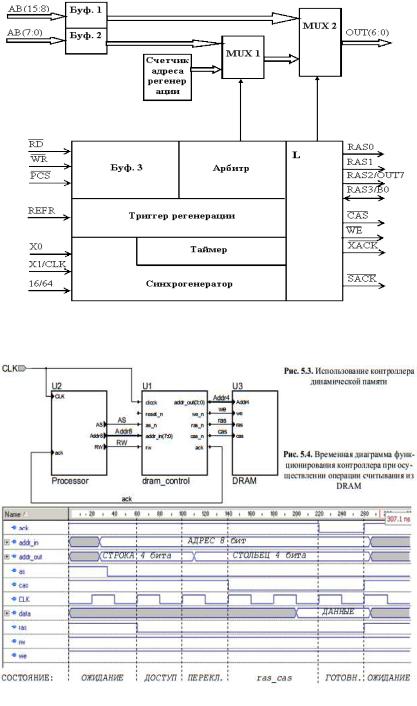

(КДП) обеспечивает мультиплексирование адреса системной шины, выработку управляющих сигналов CAS и RAS[3:0] (для селекции модулей ОЗУ), а также внутреннюю (по таймеру) или внешнюю (прозрачную) регенерацию. Структурная схема контроллера (Рис. 7.) включает в себя :

буферные схемы Буф.1,2,3 для подключения системной шины адреса и управления;

счетчик адреса регенерации;

мультиплексоры MUX1,2;

схему управления с тактовым генератором, таймером и триггером регенерации,

арбитром и логической схемой L для формирования управляющих сигналов.

КДП обеспечивает преобразование сигналов системной шины МПС в сигналы управления динамическим ОЗУ (см. Рис. 7.16), причем может работать в двух режимах : "16/64" (на память 16K или 64K соответственно). В режиме "16" две старшие линии адреса используются для формирования одного из сигналов RAS\[0..3], в режиме "64" КДП может управлять двумя банками по 64K, причем сигнал RAS появляется на одном из выходов RAS0 или RAS1 - в зависимости от состояния линии RAS3\/B0, которая в режиме "64" становится входом, определяющим номер банка ОЗУ. Регенерация может осуществляться в двух режимах - внутреннем и внешнем. Если вход REFR остается неактивным 10..16 мкС, то формируется запрос на цикл регенерации от внутреннего таймера, причем в случае конфликта арбитр отдает предпочтение циклу памяти. Таким

образом, и при регенерации по таймеру используются свободные такты шины. При внешней регенерации запрос должен быть сформирован на входе REFR. Сигнал PCS - "Защищенный выбор кристалла" отличается от традиционного CS тем, что если PCS сформирован, то цикл ЗУ аннулировать нельзя. RD, WR - запросы на циклы чтения и записи соответственно. X0, X1 - выводы для подключения кварцевого резонатора при работе с внутренним генератором. При работе с внешним генератором на вход X0 подается высокий потенциал, а на X1 - частота CLK внешнего генератора. Выходной сигнал SACK\ вырабатывается КДП в начале цикла обращения к памяти. Если запрос от МП приходится на цикл регенерации, то SACK\ задерживается до начала цикла чтения/записи. Выходной сигнал XACK\ ("Готовность данных") вырабатывается в конце цикла чтения/записи. Сигналы SACK\ и XACK\ можно использовать для управления потенциалом на входе READY микропроцессора.

Рис. 7.16. Контроллер динамического ОЗУ

Тема 6.2: Організація портів вводу/виводу. Інтерфейси зовнішніх пристроїв для взаємодії з технологічним обладнанням.

6.2.1. Адресация портов ввода-вывода. Для обращений к портам в пространстве вводавывода применяются два режима адресации. При прямой адресации фиксированный адрес порта находится непосредственно в команде, как ее второй байт, что обеспечивает. доступ к портам 0—255. При косвенной адресации номер порта находится в регистре DX и имеет диапазон от 0 до 65 535.

П.С. Каждое внешнее устройство должно быть связано с помощью интерфейса с шиной данных микропроцессорной системы так, чтобы данные могли быть переданы командами программы между этим устройством и микропроцессором. Каждый интерфейс устройства ввода/вывода должен быть адресуемым и отвечать на сигналы шины управления микропроцессора. Наиболее общий подход состоит в том, чтобы использовать один или большее количество регистров в интерфейсе устройства как буферы между устройством и процессором. Мы знаем эти буферные регистры как порты.

6.2.2. Програмування режиму вводу/виводу в порт. Приклад.

Работа с портами ввода/вывода в процессорах x86 возможна как с использованием специальных команд (IN, OUT), через отдельное адресное пространство ввода/вывода, так и по схеме с отображением регистров устройств на обычное адресное пространство. В последнем случае возможно использование обычных команд из системы команд процессора. Для адресации портов устройств в пространстве ввода/вывода, используется 16-разрядный адрес, обеспечивая доступ к 64K 8-битным портам с адресами от 0h до FFFFh. Адреса 0F8h – 0FFh– зарезервированы для системных целей. Порты с адресами 0h

– 0FFh используются оборудованием системной платы ПК (таймер, контроллер прерываний и т.п.), адреса 0100h–03FFh используют различные контроллеры: дисков, видеомонитора, компьютерной сети.

Команды IN и OUT работают с прямой адресацией (адрес порта находится в команде) для портов с адресами 0h - 0F7h и с косвенной адресацией (адрес порта находится в регистре DX) для любых портов: 0h - FFFFh. Обмен данными происходит только через регистр-аккумулятор (AX, AL), например, чтение из порта: in al,dx , запись в порт: out dx,ax

ПРИМЕР: Ниже приведен фрагмент программы передачи одного байта данных на принтер. Интерфейс принтера представлен для микропроцессора двумя портами: регистром данных (Dat_Reg) и регистром состояния (Stat_Reg). Программа читает и проверяет младший бит регистра состояния устройства. Если этот бит – 1, устройство не готово принять данные от процессора, и программа ожидает в цикле, когда бит поменяет значение. Если бит – 0, устройство готово принимать данные и микропроцессор посылает информацию в регистр данных интерфейса устройства.

Check: |

IN |

AL,Stat_Reg |

; чтение регистра состояния |

|

AND |

AL, 00000001B ; проверка младшего бита |

|

JNE |

Check |

; регистра состояния |

|

|

MOV |

AL,Data |

;пересылка в регистр данных |

|

OUT |

Dat_reg,AL |

; интерфейса |

6.2.3. Паралельний інтерфейс вводу/виводу.

Аппаратные средства и программное обеспечение, необходимые для связи периферийных устройств с микропроцессорной системой называются интерфейсом. Аппаратные средства интерфейса включают сигналы обмена данными а также оборудование, обеспечивающее этот обмен. Порядок следования сигналов во времени называется протоколом обмена.

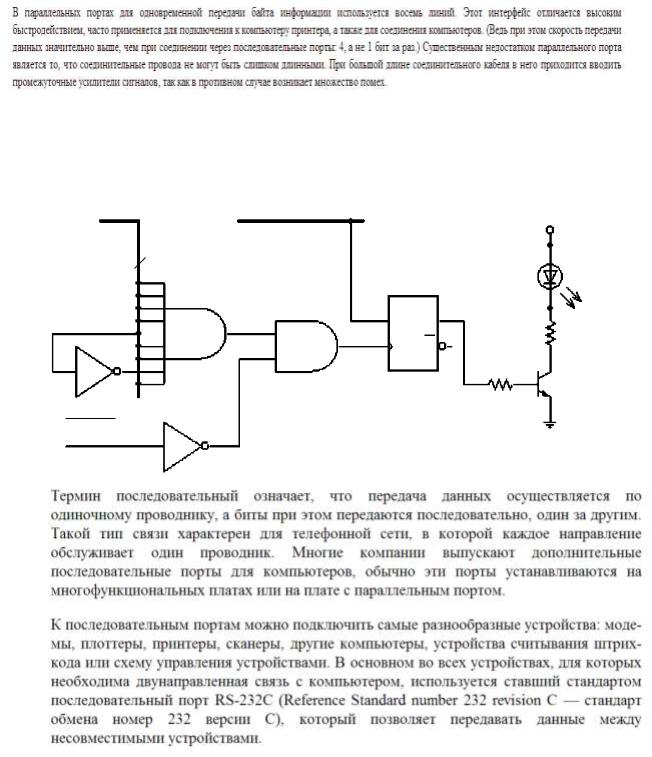

По протоколу обмена интерфейсы делят на параллельные и последовательные. Стандартные интерфейсы общего применения обычно ориентированы на байтовый (восьмибитовый) обмен информацией. В параллельном интерфейсе байт данных передается по восьми линиям одновременно, а в последовательном по одной линии бит за битом последовательно. Естественно, под линией здесь понимается два провода (информационный и общий).

На рисунке показано подключение светодиода (VD1) к шинам микропроцессорной системы. Светодиод в данной схеме рассматривается как периферийное устройство. В качестве порта вывода используется D-триггер. Логическая схема определяет адрес этого порта. Информация, которая записывается в порт, стробируется сигналом IOWC. В данном примере использован параллельный способ адресации портов ввода/вывода.

Шина |

|

A0..A7 |

Шина |

D0 |

|

+5V |

адреса |

8 |

данных |

|

|

|

|

|

|

|

|

|

VD1 |

|

|

|

|

|

|

|

|

|

|

|

|

D |

Q |

R2 |

|

|

|

|

C |

Q |

|

|

|

|

|

R1 |

||

|

|

|

|

|

|

VT1

IOWC

\

6.2.4. Послідовний інтерфейс вводу/виводу.

Тема 6.3: Тактовий генератор. Таймери. Лічильники. Внутрішня та зовнішня пам’ять. Шини адресу та даних.

*Шина ардесу, шина данных, шина управления. Предназначение шин

ША – служит для передачи адресов при обращении к памяти или устройства вводавывода ШУ – предназначена для передачи управляющих сигналов.

ШД – предназначена для пересылки данных между узлами.

6.3.1. Мікросхема тактового генератору.

Генератор тактової частоти (генератор тактових імпульсів) генерує електричні імпульси заданої частоти (зазвичай прямокутної форми) для синхронізації різних процесів в цифрових пристроях — ЕОМ, електронних годинниках і таймерах, в мікропроцесорній та іншій цифровій техніці. Тактові імпульси часто використовуються як еталонна частота

—рахуючи їх кількість, можна, наприклад, вимірювати часові інтервали.

Вмікропроцесорній техніці один тактовий імпульс, як правило, відповідає одній базовій операції. Обробка однієї інструкції може проводитися за один або кілька тактів роботи мікропроцесора, в залежності від архітектури і типу інструкції. Частота тактових імпульсів визначає швидкість обчислень.

6.3.2. Структурна схема програмованого таймеру.

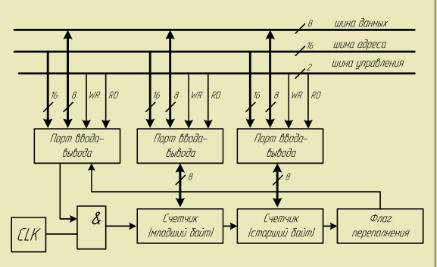

Таймеры предназначены для формирования временных интервалов, позволяя микропроцессорной системе работать в режиме реального времени. Таймеры представляют собой цифровые счѐтчики, которые подсчитывают импульсы либо от высокостабильного генератора частоты, либо от внешнего источника сигнала, в этом случае таймер называют счетчиком внешних событий. К системной шине микропроцессора таймеры подключаются при помощи параллельных портов.

Как правило, в микропроцессорной системе в качестве генератора частоты выступает генератор внутренней синхронизации микроконтроллера. Частота генератора задает минимальный временной промежуток, который может определять таймер. Интервалы времени, задаваемые с помощью таймера, могут иметь строго определенные дискретные значения. Разрядность цифрового счѐтчика таймера определяет максимальный интервал времени, который может задать таймер.

Обычно в микропроцессорных системах используются 16-тиразрядные таймеры, для подключения такого таймера к 8-миразрядному процессору требуется два параллельных порта. Кроме того, необходим выделенный порт для управления таймером: таймер нужно включать и выключать, определять, не возникало ли переполнение таймера. Факт переполнения запоминается в дополнительном триггере, подключенном к выходу переноса счетчика таймера. Этот триггер называется флагом переполнения таймера. Бит включения и выключения таймера и флаг переполнения таймера подключают к системной шине микропроцессора через отдельный порт ввода-вывода. Структурная схема таймера в самом общем виде показана на рисунке 1. Каждый из портов ввода-вывода отображается во внутреннем адресном пространстве микропроцессора, и имеет свой отдельный адрес.

Структурная схема таймера Більшість задач управління, які реалізуються за допомогою МК, вимагають

виконання їх у реальному часі. Під цим розуміється здатність системи одержувати інформацію про стан керованого об'єкта, виконувати необхідні розрахункові процедури і видавати керуючі сигнали протягом інтервалу часу, достатнього для бажаної зміни стану об'єкта .

Покладати функції формування управління в реальному масштабі часу тільки на центральний процесор неефективно, тому що це займає ресурси, необхідні для розрахункових процедур. Тому в більшості сучасних МК використовується апаратна підтримка роботи в реальному часі з використанням таймера (таймерів).

Модулі таймерів служать для прийому інформації про час настання тих або інших подій від зовнішніх датчиків подій, а також для формування керуючих впливів у часі.

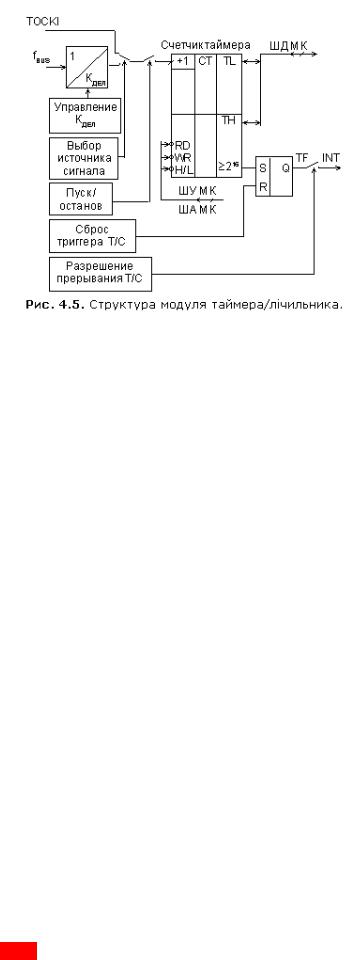

Модуль таймера 8-розрядного МК являє собою 8-ми або 16-розрядний лічильник зі схемою управління. Схемотехнікою МК звичайно передбачається можливість використання таймера в режимі лічильника зовнішніх подій, тому його часто називають таймером/лічильником. Структура типового 16-розрядного таймера/лічильника в складі МК наведена на Рис.

6.3.3. Режими роботи програмованого таймеру.

Упам'яті МК 16-розрядний лічильник відображається двома регістрами: TH - старший байт лічильника, TL - молодший байт. Регістри доступні для читання і для запису. Напрямок відліку - тільки прямий, тобто при надходженні вхідних імпульсів уміст лічильника інкрементується. У залежності від настроювання лічильник може використовувати одне з джерел вхідних сигналів:

імпульсну послідовність з виходу керованого дільника частоти fBUS;

сигнали зовнішніх подій, що надходять на вхід TOCKI контролера.

Упершому випадку говорять, що лічильник працює в режимі таймера, у другому -

урежимі лічильника подій. При переповненні лічильника встановлюється в "одиницю" тригер переповнення TF, що генерує запит на переривання, якщо переривання від таймера дозволені. Пуск і зупинка таймера можуть здійснюватися тільки під управлінням програми. Програмним способом можна також установити старший і молодший біти лічильника в довільний стан або прочитати поточний код лічильника.

Упершому випадку говорять, що лічильник працює в режимі таймера, у другому -

урежимі лічильника подій. При переповненні лічильника встановлюється в "одиницю" тригер переповнення TF, що генерує запит на переривання, якщо переривання від таймера дозволені. Пуск і зупинка таймера можуть здійснюватися тільки під управлінням програми. Програмним способом можна також установити старший і молодший біти лічильника в довільний стан або прочитати поточний код лічильника.

Розглянутий "класичний" модуль таймера/лічильника широко застосовується в різних моделях простих МК. Він може використовуватися для виміру часових інтервалів і формування послідовності імпульсів. Основними недоліками "класичного" таймера/лічильника є:

втрати часу на виконання команд пуску і зупинки таймера, що створює помилки при вимірюванні часових інтервалів і обмежує мінімальну тривалість вимірюваних інтервалів часу одиницями мс.;

складності при формуванні часових інтервалів (міток часу), відмінних від періоду повного коефіцієнта відліку, рівного (Кділ/fBUS) · 216;

неможливість одночасного обслуговування (вимірювання або формування імпульсного сигналу) відразу декількох каналів.

6.3.4. Нарощування об’єму пам’яті.

Тема 6.4: Система переривів. Контролер переривів. Організація механізму переривів. Перериви таймеру.

6.4.1. Контролер переривів. Джерело переривів.

Все микропроцессорные системы должны связываться с внешним миром. Типичная вычислительная система обычно имеет клавиатуру, дисковод и коммуникационный порт. Все они требуют внимания процессора в разное время.

Прерывания устраняют потребность в опросе путем формирования специального сигнала центральному процессору в тот момент, когда периферийное устройство требует обслуживания. Микропроцессор тогда прекращает выполнять основную задачу, сохраняет ее состояние и передает управление программе обработки прерывания. После окончания программы обработки прерывания восстанавливается первоначальное состояние процессора, и выполнение основной задачи продолжается с точки, в которой возникло прерывание.

В вычислительной системе часто происходят события, которые требуют прерывания нормального хода выполнения программы и выполнения некоторых специальных действий. Такие исключительные ситуации, или просто исключения, могут быть инициированы сигналом от внешнего устройства, или условиями, обнаруженными в процессоре.

Например, персональные компьютеры часто используют таймер, чтобы прервать процессор раз в секунду, чтобы заставить его модифицировать изображение часов, отображаемых на экране. Компьютеры, используемые в управлении производственным процессом, обычно прерываются датчиками, которые обнаруживают различные состояния оборудования, требующие немедленного внимания. Пример внутреннего состояния, требующего прерывания – попытка деления на 0, которая не может дать никакого результата. Этот тип исключительного состояния должен приостановить работу программы, чтобы прервать операцию и послать предупреждающее сообщение пользователю.

Микропроцессор 8086 имеет два источника внешних прерываний; вход

немаскируемого прерывания (NMI) и вход маскируемого прерывания (INTR). Для большинства микропроцессорных систем единственный вход маскируемого прерывания недостаточен. Большинство процессоров использует специальный контроллер прерываний, чтобы увеличить число доступных маскируемых прерываний.

6.4.2. Запроси переривів. Типи векторів переривів.

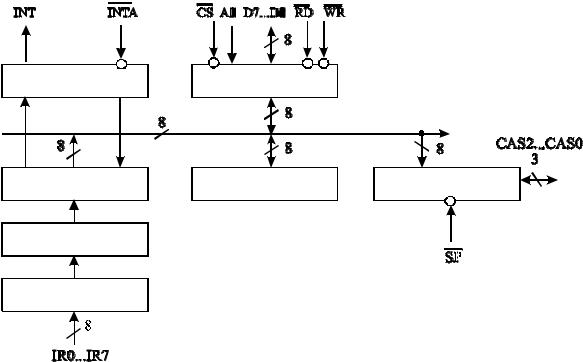

Микропроцессор 8086 использует специальную микросхему контроллера прерываний 8259 (580ВН59). Блок-схема микросхемы контроллера приведена на рис. 7.4. Этот контроллер является стандартным для многих микропроцессорных систем и персональных компьютеров. Контроллер 8259 имеет восемь входов прерываний. Используя дополнительные контроллеры, число входов прерывания возможно довести до 64. Дополнительные контроллеры называются вспомогательными; первый контроллер является основным. Основной контроллер располагает по приоритетам запросы на прерывание от вспомогательных контроллеров и своих входов IRn и передает запросы по одному на вход маскируемого прерывания процессора.

Схема управления |

Интерфейсная |

|

логика |

Регистр обслуж. |

Регистр маски |

Схема |

||||

запросов |

прерываний |

каскадирования |

||||

Схема приоритетов |

|

|

|

|

|

|

Регистр запросов |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис.7.4. Блок-схема контроллера прерываний

Микропроцессор 8086 может использовать до 256 различных прерываний. Каждое прерывание определяется его номером в пределах от 0 до 255. Каждому прерыванию соответствует вектор прерывания, который является номером прерывания, умноженным на 4. Вектор прерывания – указатель, который указывает на связанную с прерыванием подпрограмму обработки прерывания. Таблица векторов прерываний расположена в начальной области памяти микропроцессора. Таблица векторов прерываний имеет размер 1 Кбайт (4 байта, умноженные на 256).

Прежде чем начать работать, каждый контроллер прерываний должен быть инициализирован последовательностью из управляющих слов инициализации. После того, как произошел сброс системы, состояния всех регистров контроллера не определены. Слова инициализации используются, чтобы установить необходимые режимы работы контроллера.

6.4.3. Адреси функцій переривів. Приклад визову перериву.

Во многих случаях большие блоки данных должны быть переданы между устройством ввода/вывода и памятью. Дисковод, например, обычно читает и записывает данные блоками, которые могут быть объемом в тысячи байт. Если использовать для управления передачей данных процессор, то значительная часть времени его работы будет потрачена на эту операцию. Даже если при передаче данных используется режим прерываний, все равно производительность системы в целом будет сильно падать. Это происходит потому, что микропроцессор не имеет команд прямой передачи данных от внешнего устройства в память и наоборот, и ему приходится использовать регистры общего назначения для временного хранения данных. В результате передача осуществляется в два этапа: сначала из внешнего устройства – в процессор, а затем из процессора – в память. Выгоднее было бы использование передачи напрямую, минуя процессор.

Прямой доступ к памяти (ПДП) позволяет передавать данные между памятью и периферийными устройствами без вмешательства процессора. Системы, которые используют прямой доступ к памяти, имеют специальное устройство, называемое контроллер прямого доступа к памяти. Контроллер берет в этом режиме под свой контроль шины системы и выполняет управление передачей данных между памятью и периферийным устройством. Когда контроллер ПДП принимает запрос от периферийного