Микропроцесоры_Ответы

.pdf

устройства, он посылает в процессор сигнал требования прямого доступа. В этом случае процессор вырабатывает сигнал подтверждения ПДП и переходит в пассивный режим, переводя внешние шины адреса и данных в высокоомное состояние и не вырабатывая сигналы управления. В случаях, если процессору не требуется обращение к внешним шинам системы, он может продолжать выполнение команд из очереди команд. Контроллер ПДП выполняет передачу данных самостоятельно. Если передачи данных в режиме прямого доступа происходят нечасто, то это не приводит к снижению производительности системы в целом, так как передача данных при прямом доступе прозрачна для процессора.

Передача данных в режиме ПДП начинается с запроса. Устройство, требующее прямой доступ, может иметь данные для передачи или может требовать данные от другого устройства. Кроме того, передачи данных в режиме ПДП могут быть инициализированы системным программным обеспечением без внешнего запроса.

Когда режим ПДП разрешается процессором, контроллер прямого доступа к памяти обеспечивает все необходимые сигналы шины для передачи данных. Источник и приемник данных для передачи программируемы и могут быть или в пространстве адресов ввода/вывода, или в пространстве адресов памяти.

Микропроцессорные системы на основе микропроцессора 8086 используют в качестве контроллера прямого доступа к памяти микросхему 8257. Интегральная схема 8257 – программируемый 4 канальный контроллер ПДП. Каждый канал контроллера оборудован 16 разрядным регистром адреса ПДП и 16 разрядным регистром-счетчиком числа переданных байтов. Младшие 14 битов регистра-счетчика определяют количество циклов ПДП, таким образом, их максимальное количество равно 16384. Старшие 2 бита регистра-счетчика определяют тип операции ПДП для данного канала.

Логика арбитража в контроллере решает, какой канал имеет приоритет, если два канала одновременно запрашивают передачу данных. Каждый канал может получить или низкий, или высокий приоритет.

Перед использованием контроллер должен быть запрограммирован. При программировании контроллера вначале необходимо установить параметры для каждого канала. Для каждого канала программируются следующие параметры: указатель адреса ПДП, число передаваемых байт данных, тип операции ПДП

Например, персональные компьютеры часто используют таймер, чтобы прервать процессор раз в секунду, чтобы заставить его модифицировать изображение часов, отображаемых на экране. Компьютеры, используемые в управлении производственным процессом, обычно прерываются датчиками, которые обнаруживают различные состояния оборудования, требующие немедленного внимания. Пример внутреннего состояния, требующего прерывания – попытка деления на 0, которая не может дать никакого результата. Этот тип исключительного состояния должен приостановить работу программы, чтобы прервать операцию и послать предупреждающее сообщение пользователю.

Микропроцессор 8086 имеет два источника внешних прерываний; вход

немаскируемого прерывания (NMI) и вход маскируемого прерывания (INTR). Для большинства микропроцессорных систем единственный вход маскируемого прерывания недостаточен. Большинство процессоров использует специальный контроллер прерываний, чтобы увеличить число доступных маскируемых прерываний.

Тема 7.1: Засоби організації обміну із зовнішніми приладами. Схема виводів. Програмовані виводи.

7.1.1. Схема виводів мікропроцесору i8086.

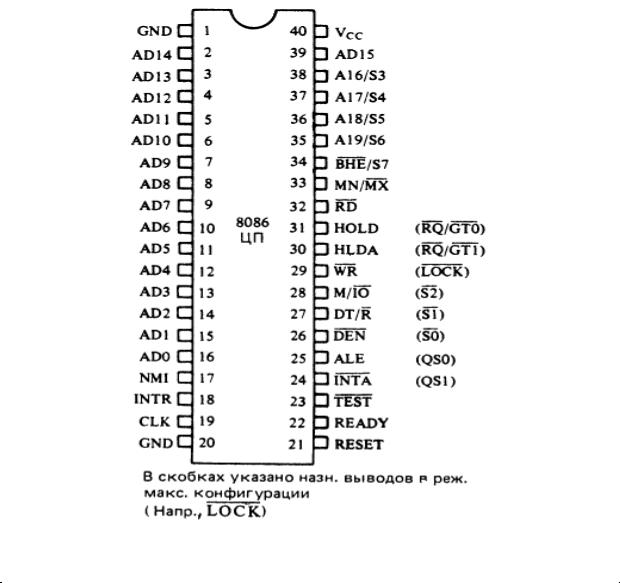

Рисунок 1. Выводы и сигналы микросхемы процессора і8086

Таблица 1. Назначение выводов и сигналов микропроцессора і8086

Обозначение |

Назначение |

Тип |

|

|

AD15 – АО Address/data – 16-разрядная |

|

|

|

мультиплексная двунаправленная шина адреса/данных |

|

|

|

(ADB - Address Data Bus), по которой с разделением во |

Вход/ |

|

AD15 - АО |

времени передаются адреса и данные. Адреса передаются |

выход |

|

|

в первом такте цикла шины и сопровождаются сигналом |

(z) |

|

|

ALE, а данные - во второй половине цикла шины и |

|

|

|

сопровождаются сигналом DEN. |

|

|

|

Линия А18/S5 сигнализирует о состоянии флага |

Вход/ |

|

А18/S5 |

разрешения прерываний, а сигнал А19/S6 может |

выход |

|

|

использоватся для управления системной шиной. |

(z) |

|

|

Сигнал ВНЕ/S7, имея высокий уровень, разблокирует |

|

|

BHE/ST7 |

шину в первом такте выполнения команды. Совместно с |

Выход (z) |

|

сигналом AD0 он моет использоваться для выбора нуных |

|||

|

|

||

|

блоков памяти. Назначение линии S7 не определено. |

|

|

RD |

Read - выходной сигнал чтения. Указывает на то, что МП |

Выход |

|

выполняет цикл чтения |

(z) |

||

|

|||

|

Ready - входной сигнал готовности, подтверждающий, |

|

|

READY |

что ячейка памяти или устройство ввода/вывода, |

Вход |

|

|

адресуемое в команде, готово к взаимодействию с МП |

|

|

|

при передаче данных. |

|

|

|

|

|

|

|||

|

|

Interrupt Request - входной сигнал запроса (при Н-уровне) |

|

||||||||

INTR |

|

маскированного |

прерывания. |

Если |

прерывания |

Вход |

|||||

|

разрешены, МП переходит к подпрограмме обработки |

||||||||||

|

|

|

|||||||||

|

|

прерывания, в противном случае игнорирует этот сигнал |

|

||||||||

|

|

Сигнал аппаратного сброса (при Н-уровце). Переводит |

|

||||||||

|

|

МП в начальное состояние, при котором сброшены |

|

||||||||

|

|

сегментные регистры (кроме CS, все разряды которого |

|

||||||||

|

|

устанавливаются в единичное состояние), указатель |

|

||||||||

|

|

команд IP, все флаги, регистры очереди команд и все |

|

||||||||

RESET |

|

внутренние триггеры |

устройства |

управления. |

Сигнал |

|

|||||

|

RESET не влияет на состояние РОН. Во время действия |

Вход |

|||||||||

(CLR) |

|

||||||||||

|

сигнала RESET все выходы, имеющие три состояния, |

|

|||||||||

|

|

|

|||||||||

|

|

переводятся в высокоимпедансное состояние; выходы, |

|

||||||||

|

|

которые имеют два состояния, становятся пассивными. |

|

||||||||

|

|

Минимальная продолжительность сигнала RESET при |

|

||||||||

|

|

первом включении МП составляет 50 мкс, а при |

|

||||||||

|

|

повторном запуске - четыре |

|

|

|

|

|

||||

|

|

Test - входной сигнал проверки. Сигнал используется |

|

||||||||

|

|

вместе с командой ожидания WAIT, выполняя которую, |

|

||||||||

|

|

МП проверяет уровень сигнала TEST. Если TEST = 0, МП |

|

||||||||

TEST |

|

переходит к выполнению следующей после WAIT |

Вход |

||||||||

|

|

команды. Если TEST = 1, МП находится в состоянии |

|

||||||||

|

|

ожидания, выполняет холостые такты и периодически, с |

|

||||||||

|

|

интервалом 5TCLK, проверяет значение сигнала TEST |

|

||||||||

CLK, (CLC) |

Clock - |

входные |

тактовые |

импульсы, обеспечивающие |

Вход |

||||||

синхронизацию работы МП |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|||||

|

|

Minimum/maximum - вход сигнала выбора минимального |

|

||||||||

MN/MX |

|

или максимального режимов. Определяет режим работы |

Вход |

||||||||

|

|

МП: при 1 - минимальный, при 0 - максимальный |

|

|

|||||||

INTA |

|

Interrupt Acknowledge - выходной сигнал подтверждения |

Выход |

||||||||

|

прерывания, определяющий чтение вектора прерывания |

||||||||||

|

|

|

|||||||||

|

|

Address Latch Enable - выходной сигнал разрешения |

|

||||||||

ALE |

|

фиксации адреса; выдается в начале каждого цикла шины |

Выход |

||||||||

|

|

и используется для записи адреса в регистр-фиксатор |

|

||||||||

|

|

Data Enable - выходной сигнал разрешения данных, |

|

||||||||

DEN (DE) |

который |

определяет |

появление |

данных |

на |

шине |

Выход (z) |

||||

|

|

адреса/данных |

|

|

|

|

|

|

|

||

|

|

Data Transmit/Receive (Output-Input) - выходной сигнал |

|

||||||||

DT/R |

(OP |

передачи/приема |

данных; |

определяет |

направление |

|

|||||

передачи данных по ADB. Предназначен для управления |

Выход (z) |

||||||||||

/IP) |

|

||||||||||

|

шинными формирователями и действует на протяжении |

|

|||||||||

|

|

|

|||||||||

|

|

всего цикла шины |

|

|

|

|

|

|

|

||

|

|

Memory/Input-Output - выходной сигнал признака |

|

||||||||

M/IO |

|

обращения к памяти (М/Ю = 1) или внешнему устройству |

Выход (z) |

||||||||

|

(М/Ю = 0). Используется для распределения адресного |

||||||||||

|

|

|

|||||||||

|

|

пространства памяти и устройств ввода/вывода |

|

|

|||||||

|

|

Write - выходной сигнал записи. Указывает на то, что МП |

|

||||||||

WR |

|

выполняет цикл записи в память или внешнее устройство, |

Выход (z) |

||||||||

|

и сопровождает данные, которые выдаются МП на шину |

|

|||||||||

|

|

|

|||||||||

|

|

данных |

|

|

|

|

|

|

|

|

|

HOLD |

|

Hold - входной сигнал запроса захвата шин от внешнего |

Вход |

||||||||

|

устройства или контроллера прямого доступа к памяти |

|

|

|

Hold Acknowledge - выходной сигнал подтверждения |

|

|

HLDA |

захвата. Сигнал указывает на то, что МП перевел свои |

Выход |

|

шины адреса/данных, адреса/состояния и управления в z- |

|||

|

|

||

|

состояние |

|

7.1.2. Адресація 8-бітного пристрою.

Имеется 8 регистров (АХ, СХ, DX, ВХ, SP, BP, SI, DI), которые можно использовать для хранения 16-разрядных данных; 8 регистров (AL, CL, DL, BL, АН, СН, DH, ВН), используемые для хранения 8-разрядных данных; 2 регистра \ВХ, BP), используемые в качестве базовых, и 2 регистра (SI, Р1) используемые в качестве индексных.

Таким образом, все регистры являются регистрами специального назначения, для адресации которых используются следующие восемь способов (универсальные для всех команд):

1)Непосредственный. Данное длинной 8 или 16 бит является частью команды. Например: выражение-константа: 12; 1010В; 08АH; ‘AB’; XX-YY-5.

2)Прямой. 16-битный эффективный адрес данного является частью команды. Например: переменная±выражение-константа: CNT; CNT+5; ARRAY-5.

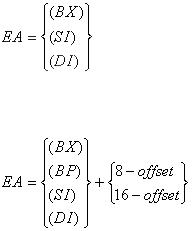

3) |

Регистровый. |

Данное |

содержится в |

определяемом командой |

регистре |

(Аx, bx, cx, dx, si, di, sp, bp). Например: регистр: AX; BH; DL. |

|

||||

4) |

Регистровый |

косвенный. |

Эффективный |

адрес данного находится в |

базовом |

регистре BX или индексном SI,DI: |

|

|

|||

.

Например: [регистр]: [BX].

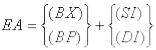

5) Регистровый относительный. Эффективный адрес равен сумме 8 или 16 битного смещения и содержимого базового или индексного регистров:

.

Например: переменная + [регистр±выражение константа]: CST[BX]; MES[SI+10H];

[BX-1].

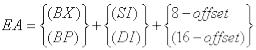

6) Базовый индексный. Эффективный адрес равен сумме содержимого базового и индексного регистров, определяемых командой:

.

.

Например: [базовый регистр][индексный регистр] : [BX][DI].

7) Относительный базовый индексный. Эффективный адрес равен сумме 8 или 16 битного смещения и базово-индексного адреса:

.

.

Например: переменная + [базовый регистр±выражение константа] [индексный регистр±выражение константа] : E[BX+5][SI-2]; DATA[BX][SI]; [BX+2][SI].