- •Введение

- •Раздел 1 Технологии тестирования и верификации цифровых систем на кристаллах

- •1.1. Современные проблемы верификации систем-на-кристаллах

- •1.2. Моделирование на уровне транзакций

- •1.3. Верификация на основе ассерций

- •1.4. Синтез ассерций

- •1.5. Средства верификации цифровых систем с использованием ассерций

- •1.6. Постановка цели и задач диссертационного исследования

- •Раздел 2 модели диагностирования функциональных нарушений hdl-кода цифровых систем на кристаллах

- •2.1. Введение в тему исследования

- •2.2. Модель процессов тестирования и верификации

- •2.3. Модель поиска функциональных нарушений в программе

- •2.4. Дискретная производная как бинарное xor-отношение

- •2.5. Выводы и рекомендации

- •Раздел 3 методы диагностирования функциональных нарушений

- •3.1. Форма представления модели

- •3.2. Метод векторно-логического анализа столбцов

- •3.3. Метод векторно-логического анализа строк

- •3.4. Матричный метод поиска функциональных нарушений в программных блоках

- •3.5. Выводы и рекомендации

- •Раздел 4 инфраструктура встроенного тестирования функциональных нарушений hdl-кода

- •4.1 Мультипроцессорные решения задач сервисного обслуживания

- •4.2. Мультиматричный процессор анализа бинарных операций

- •4.3. Аппаратная реализация мультиматричного процессора

- •4.4. Аппаратная имплементация инфраструктуры тестирования

- •4.5. Система тестирования и верификации hdl-кода

- •4.6. Выводы и рекомендации

- •Заключение

- •Приложение б. Подробный отчёт синтеза

- •Приложение в. Аппаратная имплементация инфраструктуры тестированиия

- •Приложение г. Документы, подтверждающие внедрение

- •Список использованных источников

3.5. Выводы и рекомендации

Три предложенных метода анализа столбцов, строк и матриц в целом ориентированы на повышение глубины встроенного диагностирования функциональных нарушений в программных моделях путем испоьзования структурно-аналитической модели верификации кода цифровых систем на кристаллах. Модель поиска функциональных нарушений основана на механизме ассерций, что дает возможность существенно уменьшить время диагностирования, а также сократить общее время проектирования программных и аппаратных продуктов. Предложенные методы диагностирования функциональных блоков HDL-кода SoC отличаются минимальным набором процессов и ориентированы на встроенное обслуживание программных блоков с использованием ассерционного графа транзакций. Методы совместно с моделями описания цифровых систем на кристаллах дают возможность осуществлять сервисы: моделирование и верификацию функциональных блоков HDL-кода SoC, оценку качества тестов, построение таблиц функциональных нарушений (ФН); диагностирование с заданной глубиной (до 20 -30 строк) в HDL-коде SoC; исправление ошибок кода на основе использования альтернативных программных блоков.

1. Метод векторно-логического анализа столбцов характеризуется применением векторной xor-операции между реакцией функциональности на тест, формально рассматриваемой в качестве входного вектор-столбца, и столбцов таблицы неисправностей. Для подсчета качества взаимодействия векторов в целях выбора лучшего решения определяются столбцы c минимальным числом единиц результирующего вектора. Они идентифицируют и формируют дефектные блоки с функциональными нарушениями, проверяемые на тестовых наборах.

2. Метод векторно-логического анализа строк предназначен для определения места дефекта или ФН программного кода и характеризуется наличием двух процедур: вычисление логического произведения конъюнкции строк, отмеченных единичными значениями вектора, на отрицание дизъюнкции нулевых строк для одиночных дефектных блоков; вычисление логического произведения дизъюнкции единичных строк на отрицание дизъюнкции нулевых строк для кратных дефектных блоков. Метод интересен тем, что не привязан к критериям качества диагностирования, а оперирует лишь двумя компонентами, таблицей ФН и вектором экспериментальной проверки.

3. Матричный метод поиска функциональных нарушений в программных блоках цифровых систем на кристаллах характеризуется использованием графа транзакций программных блоков и триады матриц одного формата, которые формируют активизацию блоков на тестовых сегментах в процессе моделирования; активность ассерций, соответствующих блокам, на тестовых сегментах также в процессе моделирования; дефектные блоки, полученные в результате выполнения xor-операции над двумя предыдущими матрицами. Метод ориентирован на аппаратную реализацию логических матричных операций для установления диагноза.

Раздел 4 инфраструктура встроенного тестирования функциональных нарушений hdl-кода

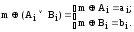

Предлагается структура системы тестирования, верификации и диагностирования функциональных нарушений HDL-блоков цифровых систем на кристаллах, использующая взаимодействие testbench (m) и библиотеки эталонных решений, которое формирует производную в виде неисправного модуля, подлежащего коррекции:

Здесь

– технические состояния программного

блока, которые соответствуют различным

библиотекам (

– технические состояния программного

блока, которые соответствуют различным

библиотекам ( – исправных модулей и неисправностей),

которые объединяются для формирования

точного диагноза. Система отличается

от аналогов двумя библиотеками, открытыми

к пополнению в процессе предоставления

сервисов. Структура системы представлена

моделями и методами ассерционно-ориентированной

верификации и диагностирования, которые

разработаны в разд. 2 и 3.

– исправных модулей и неисправностей),

которые объединяются для формирования

точного диагноза. Система отличается

от аналогов двумя библиотеками, открытыми

к пополнению в процессе предоставления

сервисов. Структура системы представлена

моделями и методами ассерционно-ориентированной

верификации и диагностирования, которые

разработаны в разд. 2 и 3.

Это дает возможность существенно (на 50%) уменьшить время диагностирования, а также сократить общее время проектирования программных и аппаратных продуктов на 15%. Предложенные программно-аппаратные решения диагностирования функциональных блоков HDL-кода SoC отличаются технологичностью и простотой реализации процессов и ориентированы на встроенное обслуживание программных блоков с использованием ассерционного графа транзакций, синтезируемого в процессе симуляции HDL-кода. Система тестирования дает возможность осуществлять сервисы: моделирование и верификацию функциональных блоков HDL-кода SoC, оценку качества тестов, построение таблиц функциональных нарушений (ФН); диагностирование с заданной глубиной (до 20-30 строк) в HDL-коде SoC; исправление ошибок кода на основе использования альтернативных программных решений.

Цель – существенное уменьшение времени проектирования и отладки HDL-кода цифровых систем на кристаллах за счет создания модуля (инфраструктуры) верификации, использующего ассерционно-ориентированные модели и методы тестирования и графовые модели программного продукта.

Задачи: 1) Имплементация в программный код метода анализа столбцов и структурно-аналитической модели диагностирования HDL-модели цифровых систем на кристаллах. 2) Программная имплементация метода анализа строк таблицы функциональных нарушений на основе механизма ассерций для повышения глубины диагностирования HDL-кода. 3) Аппаратная реализация матричного xor-взаимодействия объектов и компонентов для решения задач диагностирования функциональных нарушений. 4) Верификация программно-аппаратных компонентов системы верификации и диагностирования на практических примерах программных кодов, цифровых проектов на кристаллах.

Источники: 1. Программные и аппаратные средства верификации и диагностирования компонентов цифровых систем на кристаллах [1-6]. 2. Промышленные системы синтеза и анализа цифровых IP-модулей на кристаллах [9-14, 26-30, 35-111] и их сервисное обслуживание. 3. Реализация матричных процессоров и вычислительных архитектур для ускорения процессов тестирования и верификации [31-34].