- •1.Кодирование логической и двоичной информации электрическими сигналами.

- •2. Потенциальная система кодирования, положительная и отрицательная логика .

- •3. Реализация ф–ии “и” на диодах.

- •4. Реализация ф–ии “или” на диодах.

- •5. Реализация ф–ии “не” на диодах.

- •6. Ттл элемент, схема, работа.

- •Переходная характеристика ттл элемента.

- •8. Ттл элемент, выходные характеристики.

- •9. Разновидности схем логических элементов.

- •10. Соединение логических элементов.

- •11. Соединение логических элементов и пассивных радиокомпонентов.

- •12. Асинхронный rs триггер.

- •13. Синхронный rs триггер.

- •14. D триггер-защёлка.

- •15. D триггер с динамической блокировкой входов.

- •16. Универсальный jk триггер.

- •17. Счётный триггер.

- •18. Счётчики, общие положения.

- •19. Двоичные счётчики.

- •20. Недвоичные счётчики.

- •21. Счётчики с параллельным переносом.

- •22. Параллельные регистры.

- •23. Сдвиговые регистры.

- •24. Реверсивные регистры.

- •25. Линейные дешифраторы.

- •26. Матричные дешифраторы.

- •27. Пирамидальный дешифратор.

- •28. Мультиплексор.

- •29. Реализация логических функций на мультиплексоре.

- •30. Одноразрядный сумматор.

- •31. Последовательный многоразрядный сумматор.

- •32. Параллельный многоразрядный сумматор.

- •34. Ттл элемент памяти.

- •36. Запоминающий элемент пзу.

- •37. Запоминающий элемент динамической памяти.

- •38. Организация бис зу.

- •39. Структурная схема бис зу.

- •40. Модуль памяти статического озу.

- •41. Триггер Шмитта.

- •42. Мультивибратор.

- •43 Формирователь импульсов.

- •44. Одновибратор.

- •45. Индикация состояния выхода логического элемента .

- •46. Статическая индикация.

- •47. Определение интервала времени по заданным уровням в цепях первого порядка .

- •49. Цап на суммировании токов.

- •50. Цап на резистивной матрице r-2r.

- •51. Ацп ─ общие принципы построения, погрешности.

- •52. Параллельный ацп.

- •53. Ацп последовательного приближения.

- •54. Ацп двойного интегрирования.

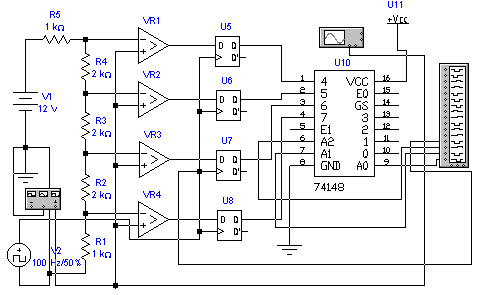

52. Параллельный ацп.

Как видно из схемы его основу составляют компараторы на инвертирующие входы которых подаются напряжения пропорциональные кванту, а на не инвертирующие входы подается входное аналоговое напряжение. Соответственно количество компараторов определяет количество уровней квантования.

Источник напряжения V1 является источником опорного напряжения, которое делится на уровни квантования резистивным делителем R1÷R5. Напряжения уровней квантования пдаются на компараторы VR1÷VR4. На не инвертирующие входы подается входное аналоговое напряжение от функционального генератора. При входном напряжении равном нулю на выходах компараторов установятся напряжения низкого логического уровня. При возрастании входного напряжения до уровня 0,5 кванта на выходе компаратора VR4 появится высокий уровень напряжения. Дальнейший рост входного напряжения приведет к последовательному единичных уровней напряжения на выходах остальных компараторов, т.е. на выходах компараторов имеем линейный унитарный код. Для преобразования унитарного кода в двоичный код использован приоритетный шифратор микросхема 74148. Триггеры U5÷U8 использованы с целью уменьшения погрешности преобразования, так как в этом случае выборка унитарного кода будет осуществляться настолько быстро, что изменение аналоговой переменной будет не существенно. Источник напряжения импульсной последовательности V2 определяет тактовую частоту выборки значений унитарного кода.

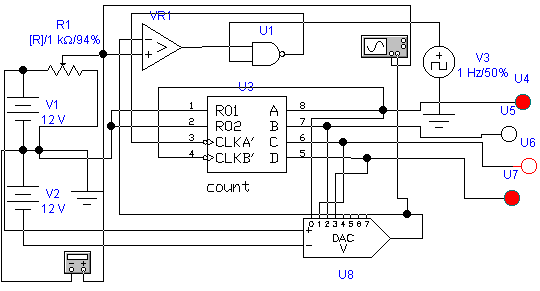

53. Ацп последовательного приближения.

В областях применения АЦП где не требуется высокое быстродействие, а высокие затраты не допустимы нет необходимости использовать параллельные АЦП. Для этих целей были разработаны АЦП последовательного приближения имеющие существенно меньшее быстродействие, но и значительно дешевле параллельных АЦП.

Существует несколько разновидностей построения последовательных АЦП: АЦП с реализацией весового метода и АЦП с реализацией числового метода.

Рассмотрим АЦП последовательного приближения с использованием числового метода.

Работа схемы осуществляется следующим образом. Входное аналоговое напряжения с резистора R1 подается на не инвертирующий вход компаратора. На инвертирующий вход компаратора подается напряжение с выхода ЦАП U8, которое в начальный момент равно 0В. следовательно на выходе компаратора будет высокий уровень напряжения, который откроет ключ U1 на элементе 2И-НЕ. Импульсное напряжение с генератора V3 через открытый ключ U1 поступает на вход двоичного счетчика U3, выходы которого подключены к разрядным входам ЦАП U8. В процессе счета код на выходах счетчика увеличивается и, следовательно, увеличивается и выходное напряжение формируемое цифро-аналоговым преобразователем. Когда его величина станет равной входному напряжению выход компаратора переключится на низкий уровень, что приведет к закрыванию ключа U1, счетчик остановится и на его выходах будет двоичный код соответствующий входному напряжению.