- •1.Кодирование логической и двоичной информации электрическими сигналами.

- •2. Потенциальная система кодирования, положительная и отрицательная логика .

- •3. Реализация ф–ии “и” на диодах.

- •4. Реализация ф–ии “или” на диодах.

- •5. Реализация ф–ии “не” на диодах.

- •6. Ттл элемент, схема, работа.

- •Переходная характеристика ттл элемента.

- •8. Ттл элемент, выходные характеристики.

- •9. Разновидности схем логических элементов.

- •10. Соединение логических элементов.

- •11. Соединение логических элементов и пассивных радиокомпонентов.

- •12. Асинхронный rs триггер.

- •13. Синхронный rs триггер.

- •14. D триггер-защёлка.

- •15. D триггер с динамической блокировкой входов.

- •16. Универсальный jk триггер.

- •17. Счётный триггер.

- •18. Счётчики, общие положения.

- •19. Двоичные счётчики.

- •20. Недвоичные счётчики.

- •21. Счётчики с параллельным переносом.

- •22. Параллельные регистры.

- •23. Сдвиговые регистры.

- •24. Реверсивные регистры.

- •25. Линейные дешифраторы.

- •26. Матричные дешифраторы.

- •27. Пирамидальный дешифратор.

- •28. Мультиплексор.

- •29. Реализация логических функций на мультиплексоре.

- •30. Одноразрядный сумматор.

- •31. Последовательный многоразрядный сумматор.

- •32. Параллельный многоразрядный сумматор.

- •34. Ттл элемент памяти.

- •36. Запоминающий элемент пзу.

- •37. Запоминающий элемент динамической памяти.

- •38. Организация бис зу.

- •39. Структурная схема бис зу.

- •40. Модуль памяти статического озу.

- •41. Триггер Шмитта.

- •42. Мультивибратор.

- •43 Формирователь импульсов.

- •44. Одновибратор.

- •45. Индикация состояния выхода логического элемента .

- •46. Статическая индикация.

- •47. Определение интервала времени по заданным уровням в цепях первого порядка .

- •49. Цап на суммировании токов.

- •50. Цап на резистивной матрице r-2r.

- •51. Ацп ─ общие принципы построения, погрешности.

- •52. Параллельный ацп.

- •53. Ацп последовательного приближения.

- •54. Ацп двойного интегрирования.

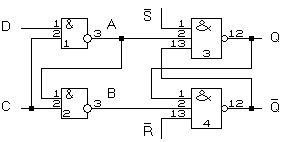

14. D триггер-защёлка.

Основой для построения схемы D триггера является асинхронный RS триггер (3 и 4 элементы). На 1 и 2 элементах собрана схема управления (входная логика), имеется два входа: D - информационный вход, С - вход синхронизации. Входные элементы - 2И-НЕ и поэтому, когда С=0 А=В=1 независимо от состояния переменной D, а это режим хранения для RS триггера на 3 и 4 элементах.

Для анализа работы схемы выберем нулевое начальное состояние : D=C=0 и Q=0, Q=1.

При этом промежуточные переменные А=В=1, что соответствует режиму хранения для асинхронного RS триггера на 3 и 4 элементах.

В момент времени t1 переменной D даем единичное значение, но изменений состояния схемы не произойдет, так как С=0. В момент времени t2 С=1, на входах первого элемента D=С=1 и, следовательно, через интервал задержки А=0. Но и на входах второго элемента С=А=1 и это приводит к тому, что переменная В начинает изменение, которое не происходит благодаря тому, что переменная А быстро принимает нулевое значение. Переменная А=0 -- активный уровень на входе асинхронного RS триггера и через два интервала Q=1, и через три интервала =0. Прошёл процесс записи единицы в триггер. Далее оставим неизменным значение С=1 и с момента t3 до t6 будем менять значение переменной D. На интервале от t3 до t6 выходная переменная Q повторяет значения входной переменной D с соответствующими задержками.

D |

C |

Q |

|

Режим |

0 |

0 |

Q(t-1) |

(t-1) |

Хранение |

1 |

0 |

Q(t-1) |

(t-1) |

Хранение |

0 |

1 |

0 |

1 |

Запись ”0” |

1 |

1 |

1 |

0 |

Запись “1” |

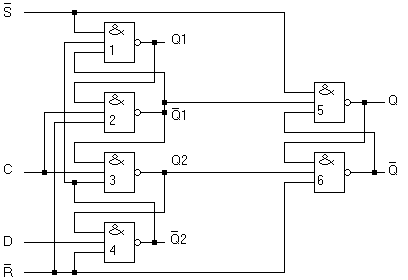

15. D триггер с динамической блокировкой входов.

Рассматриваемый триггер построен на шести элементах 3И-НЕ; 1,2,3 и 4 элементы реализуют входную логику а на 5 и 6 элементах реализован асинхронный RS триггер, являющийся основой. Можно к анализу схемы подойти по другому; на 2,3,5 и 6 элементах реализован D триггер-защёлка, а 1 и 4 элементы формируют входную логику, исключающую срабатывание триггера по уровню.

Д

Рис.24. D триггер с динамической блокировкой входов.

ля анализа работы схемы выберем начальное состояние: D=C=0, S=R=1, Q=0. При этом промежуточные переменные получат значения: Q1=0, Q2=1, =1,

=1,

=1.

Работа схемы отображается временной

диаграммой, которая приведена на рис.25.

=1.

Работа схемы отображается временной

диаграммой, которая приведена на рис.25.

В момент t1 переменной D даем единичное значение, через один интервал задержки переменная примет нулевое значение, и через два интервала переменная Q1 примет единичное значение.

Других изменений в состоянии схемы не будет. Осуществилась подготовка к записи “1” в триггер. В момент t2 переменной С даем единичное значение при D=1 -- через один интервал =0, активный уровень на входе асинхронного RS триггера. Соответственно , через два интервала Q=1 и через три интервала =0. Произошла запись “1” в триггер по фронту сигнала С.

В момент t3 переменная D=0 при С=1. Через один интервал =1 и других изменений не будет. В момент t4 D=1, через один интервал =0. В момент t5 C=0 при D=1, через один интервал =1 и через два интервала Q1=0. В момент t6 D=0 , через один интервал =1, т.е. вернулись в начальное состояние.

D |

C |

R |

S |

Q |

|

Режим |

* |

* |

0 |

1 |

0 |

1 |

Установка в “0” |

* |

* |

1 |

0 |

1 |

0 |

Установка в “1” |

0 |

0 |

1 |

1 |

Q(t-1) |

(t-1) |

Хранение |

0 |

|

1 |

1 |

0 |

1 |

Запись “0” |

1 |

|

1 |

1 |

1 |

0 |

Запись “1” |