- •1.Кодирование логической и двоичной информации электрическими сигналами.

- •2. Потенциальная система кодирования, положительная и отрицательная логика .

- •3. Реализация ф–ии “и” на диодах.

- •4. Реализация ф–ии “или” на диодах.

- •5. Реализация ф–ии “не” на диодах.

- •6. Ттл элемент, схема, работа.

- •Переходная характеристика ттл элемента.

- •8. Ттл элемент, выходные характеристики.

- •9. Разновидности схем логических элементов.

- •10. Соединение логических элементов.

- •11. Соединение логических элементов и пассивных радиокомпонентов.

- •12. Асинхронный rs триггер.

- •13. Синхронный rs триггер.

- •14. D триггер-защёлка.

- •15. D триггер с динамической блокировкой входов.

- •16. Универсальный jk триггер.

- •17. Счётный триггер.

- •18. Счётчики, общие положения.

- •19. Двоичные счётчики.

- •20. Недвоичные счётчики.

- •21. Счётчики с параллельным переносом.

- •22. Параллельные регистры.

- •23. Сдвиговые регистры.

- •24. Реверсивные регистры.

- •25. Линейные дешифраторы.

- •26. Матричные дешифраторы.

- •27. Пирамидальный дешифратор.

- •28. Мультиплексор.

- •29. Реализация логических функций на мультиплексоре.

- •30. Одноразрядный сумматор.

- •31. Последовательный многоразрядный сумматор.

- •32. Параллельный многоразрядный сумматор.

- •34. Ттл элемент памяти.

- •36. Запоминающий элемент пзу.

- •37. Запоминающий элемент динамической памяти.

- •38. Организация бис зу.

- •39. Структурная схема бис зу.

- •40. Модуль памяти статического озу.

- •41. Триггер Шмитта.

- •42. Мультивибратор.

- •43 Формирователь импульсов.

- •44. Одновибратор.

- •45. Индикация состояния выхода логического элемента .

- •46. Статическая индикация.

- •47. Определение интервала времени по заданным уровням в цепях первого порядка .

- •49. Цап на суммировании токов.

- •50. Цап на резистивной матрице r-2r.

- •51. Ацп ─ общие принципы построения, погрешности.

- •52. Параллельный ацп.

- •53. Ацп последовательного приближения.

- •54. Ацп двойного интегрирования.

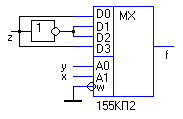

29. Реализация логических функций на мультиплексоре.

Для более полного понимания логическую функцию зададим таблицей состояний (табл. 11). Переменная f является функцией трех переменных и, следовательно, имеет восемь возможных состояний. Наиболее простое решение: для схемотехнической реализации заданной функции необходимо выбрать мультиплексор на восемь информационных входов и, соответственно, с тремя адресными входами. Аргументы функции будем подавать на адресные входы. По каждому сочетанию адресных переменных, а их восемь, будет осуществляться подключение соответствующего информационного входа к выходу мультиплексора, для получения значения функции необходимо на информационные входы мультиплексора соответственно подавать либо “0”, либо “1”. Подобная реализация функции, в соответствии с заданием (табл. 11), показана на рис. 61. На входах и выходе мультиплексора указаны обозначения функции и ее аргументов в соответствии с заданием.

x |

y |

z |

f |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

30. Одноразрядный сумматор.

Сумматор ─ электронное устройство, предназначенное для получения суммы кодов двух операндов (слагаемых). Сумматоры подразделяются на:

- одноразрядные и многоразрядные;

- последовательные и параллельные.

x |

y |

s |

p |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

31. Последовательный многоразрядный сумматор.

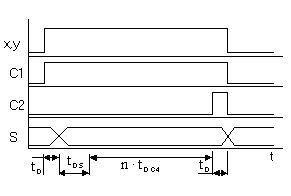

Последовательные сумматоры выполняют операцию последовательно над разрядами слагаемых, начиная с младших разрядов. При этом последовательно поразрядно осуществляется формирование переноса и его суммирование с последующими разрядными частичными суммами.

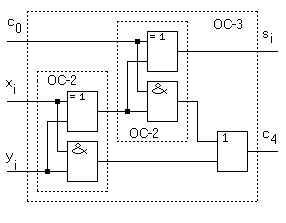

Последовательный сумматор предусматривает использование одного сумматора ОС-3 не зависимо от количества разрядов слагаемых.

Схема состоит из двух сдвиговых регистров RG1 и RG2, предназначенных для хранения и сдвига операндов, последовательного регистра RG3 для записи и хранения суммы, одноразрядного сумматора ОС-3, устройства задержки переноса, и качестве которого лучше всего применить триггер. При выполнении разрядного суммирования сформированный перенос будет записываться в этот триггер, а использован перенос будет при выполнении суммирования в следующем старшем разряде.

32. Параллельный многоразрядный сумматор.

Параллельные сумматоры выполняют операцию одновременно над всеми разрядами слагаемых, однако, перенос, сформированный в младших разрядах последовательно суммируется со старшими частичными суммами.

Схема состоит из четырех схем ОС-3 и двенадцати элементов 2И, используемых в качестве ключей. Ключи подачи операндов на входы сумматора управляются сигналом С2 (активный высоким уровнем), а ключи выдачи результата -- С1. Как только С2=1 на входы сумматора подаются операнды, и начинается процесс суммирования. Все разряды слагаемых одновременно поступают на входы сумматоров и одновременно во всех разрядах начинается формирование суммы и переноса.