- •1)Параметри імпульсного сигналу

- •3) Елементарні логічні функції

- •4)Властивості Кон’юнкції, Диз’юнкції та заперечення

- •5) Вираження елементарних логічних функцій через оперпціїї і, або, ні ----- 3) Елементарні логічні функції

- •6) Логічні елементи на дискретних деталях

- •7.Логічні елементи ттл логіки/

- •8.Логічні елементи езл логіки

- •9.Логічні елементи мдн логіки

- •10. Логічні елементи і2 л логіки

- •5. Демультиплексором

- •6. Мультиплексорне дерево.

- •7.Перетворювачі кодів

- •8. Цифрові компаратори

- •1. Тригер, його структура. Типи тригерів

- •2. Призначення, основні властивості тригера

- •9) Лічильники, загальні відомості

- •10) Лічильники на додавання

- •11) Лічильники на віднімання

- •12) Реверсивні та універсальні лічильники

11) Лічильники на віднімання

У двійковому віднімаючому лічильнику кожен імпульс, що віднімається, зменшує стан на одиницю. Поточне значення кількості вхідних імпульсів n-разрядного двійкового віднімаючого лічильника визначається по формулі

![]()

де

- значення коду на прямих виходах

тритеров лічильника;

- значення коду на прямих виходах

тритеров лічильника;

![]() - заздалегідь записане початкове число;

при цьому повинна виконуватися умова

- заздалегідь записане початкове число;

при цьому повинна виконуватися умова

![]()

У віднімаючих лічильниках сигнали міжрозрядного зв'язку називаються позиками. За правилом двійкового віднімання у момент вступу рахункового імпульсу (заїм із старшого розряду з одиничним значенням виникає за умови, що все молодші тритеры знаходяться в нульовому стані. Після цього усі вони перемикаються в стан "1", а старші - в стан "0". Сигнали позики утворюються на інверсних виходах двоступінчатих тригерів або на прямих виходах тритеров з динамічним управлінням по фронту. Параметри віднімаючого лічильника (модуль і місткість рахунку, швидкодія) співпадають з аналогічними характеристиками лічильників, що підсумовують.

12) Реверсивні та універсальні лічильники

Лічильники цього типу можуть виконувати як додавання, так і віднімання імпульсів. Для їх побудови можуть бути використані принципи роботи та схемні рішення простих лічильників (підсумовувальних та віднімальних). Реверс роботи даного лічильника здійснюється перемиканням кіл передачі переносу.

У

схемі лічильника передбачено дав режими

роботи – додавання, при якому лічильник

підсумовує, тобто збільшує на одиницю

число вхідних імпульсів, і віднімання,

при якому він за кожним тактом віднімає

одиницю двійкового коду. Реверсування

досягається передачею або сигналу

переносу з виходів ![]() ,або

сигналу позички з виходів

,або

сигналу позички з виходів ![]() тригерів.

тригерів.

При

подачі рівня 1 на керуючий вхід "ДОД",

що є дозволяючим для верхніх кон’юнкторів,

у реверсивному лічильнику прямі виходи

тригерів мають зв’язок із входами

наступних тригерів і, отже, реалізується

режим додавання. Для перемикання

лічильника у режим віднімання слід

подати одиницю на вхід "ВІД", шо

під'єднаний до всіх нижніх; кон'юнкторів.

Цього

досить для передачі сигналів позичок

з інверсних виходів ![]() тригерів.

тригерів.

Лічильник з довільним періодом роботи

Лічильники з коефіцієнтом перерахунку Ксч= 1.2n будуються на основі двійкових лічильників. Принцип роботи таких лічильників полягає у виключенні "зайвих" стійких М станів у двійкового лічильника з коефіцієнтом перерахунку 2n, при цьому число заборонених станів М=2n - Ксч. Лічильники з довільним коефіцієнтом рахунку за способом побудови діляться на лічильники з природним і довільним порядком рахунку. У лічильниках з природним порядком рахунку порядок рахунку починається з 0 і закінчується числом Ксч - I, а потрібний коефіцієнт перерахунку забезпечується схемою блокування перенесення. У лічильниках з довільним порядком рахунку в процесі рахунку лічильник приймає стани, що не відповідають його еквівалентному представленню в двійковому коді. За способом побудови ці лічильники діляться на лічильники з примусовим насчетом і початковою установкою коду, рівного М.

У лічильниках з примусовим насчетом виключення заборонених станів М досягається за рахунок примусової установки окремих його розрядів в стан "I". В результаті цього в процесі рахунку показання лічильника змінюються в природній формі, починаючи від 0 і кінчаючи деяким числом Х≤ Ксч - 2. З приходом чергового імпульсу лічильник замість стану Х+1 приймає стан Х+1+М, рівний 2n-1, тобто усі розряди лічильника приймають стан "+".

Кільцеві лічильники

- це ланцюг тригерів, в якому забезпечуються зрушення попередньо записаного маркируючого коду по кільцю, в напрямку старших або молодших розрядів. Також кільцеві лічильники відносяться до лічильників з одиничним кодуванням, у яких коефіцієнт рахунку дорівнює кількості тригерів. У кільцевих лічильниках кожен розряд має вагу рівну номеру стану

Особливість роботи цих лічильників полягає у тому, що кількість імпульсів, які потрібно підрахувати, визначається не кодом, що фіксується на виходах лічильника, а станом останнього тригера. У найпростішому випадку кільцевий лічильник будують на регістрі зсуву, наприклад на чотирирозрядному регістрі КІ55ИР1.

Схема лічильника Джонсона будується на основі кільцевого лічильника, в якому зворотний зв'язок реалізується з підключенням інверсного виходу старшого розряду до входу молодшого. На відміну від звичайного кільцевого тригера лічильник Джонсона має модуль лічби Mл=2n+2=10 (у ньому додатково фіксуються стани {0000} і {1111}).

Подільник частоти

У подільниках частоти вхідна періодична послідовність імпульсів ділиться на задане число. У якості подільника частоти можна використовувати лічильник, коефіцієнт лічення якого Кліч визначає число, на яке ділиться частота вхідних імпульсів. Особливість подільника складається в тому, що він має один вихід.

Коефіцієнт ділення Кділ=Кліч може мати постійне або змінне значення.

Для того щоб побудувати подільник частоти на входи кон’юнктора подають вихідні сигнали з тих розрядів лічильника, які у кодовій комбінації, що відповідає Кділ, мають високий рівень. Приклад подільника з Кділ = 9 показаний на рисунку.

Подільники з змінним коефіцієнтом ділення Подільники з змінним коефіцієнтом ділення (ПДЗКД) можуть бути побудовані за різноманітними схемотехнічними варіантами. Наприклад з попереднім установленням початкового стану, від якого ведеться лічення, до переповнення лічильника, або з установленням заданого проміжного значення, до котрого, починаючи з нульового, ведеться лічення вхідних імпульсів, а потім результат скидається і починається новий цикл лічення.

Основу ПДЗКД складає двійковий лічильник (DD2), що починає лічення з нульового значення і продовжує роботу до встановленого проміжного стану, рівного необхідному коефіцієнту ділення Кділ. Після цього лічильник знову скидається в нуль і починається новий цикл лічення. Для визначення моменту досягнення рівності кодів, що визначають проміжний стан лічильника і значення Кділ у схемі використаний цифровий компаратор (DD1). В момент рівності кодів А=В на виході компаратора з'являється логічна одиниця, що скидає лічильник у початковий нульовий стан. Додатковий тригер (DD3) необхідний для усунення можливості збою при установленні нульового стану СТ2 через розкид часових параметрів тригерів лічильника. Одиничним сигналом з виходу компаратора FА=В тригер встановлюється в 1 і підтримує на вході R лічильника одиничний сигнал на час, достатній для скидання всіх розрядів DD2. Наступним вхідним імпульсом тригер скидається в нульовий стан. Якщо розкид часових параметрів тригерів лічильника невеликий, то DD3 можна виключити.

Принцип перетворення аналог-код

Вимірювальне пристрої безперервної дії, що застосовується в системах автоматичного регулювання з керуючими цифровими обчислювальними машинами, можуть приєднуватися до ЦВМ лише через перетворювачі аналог-код, що перетворюють вихідну аналогову інформацію в код (двійковий, двійково-циклічний) Аналогові сигнали надходять у вигляді постійної або змінної напруги, частоти, фази, тимчасових інтервалів і кутів повороту.

Цифро аналогові перетворювачі.

Предназначені для перетворення цифрової інформації в аналогову форму у вигляді напруги (іноді струму). Їх використовують в системах управління технічними процесами, в аналогових мікропроцесорах, в дисплеях, графобудівниках, робототехніці.

Цифро-аналогове перетворення полягає в тому, що для вхідного паралельного n-розрядного коду

![]()

Де X - цифри 0 або 1, а 2 - вага i - го розряду, спочатку отримують так І пропорційного значенням числа X, а після цього преобразуют його в вихідну напругу .Значення струму I, визначається сумою еталонних струмів I, створюваних для кожного розряду числа.

![]()

Причому підсумовуються струми тільки тих розрядів, для яких X = 1. Значення еталонів струму I, пропорційні вазі позиції двійкового числа і зменшуються в два рази при переході від старшого i- розряду до сусіднього молодшого з номером i + 1

Послідовні та паралельні аналого-цифрові перетворювачі.

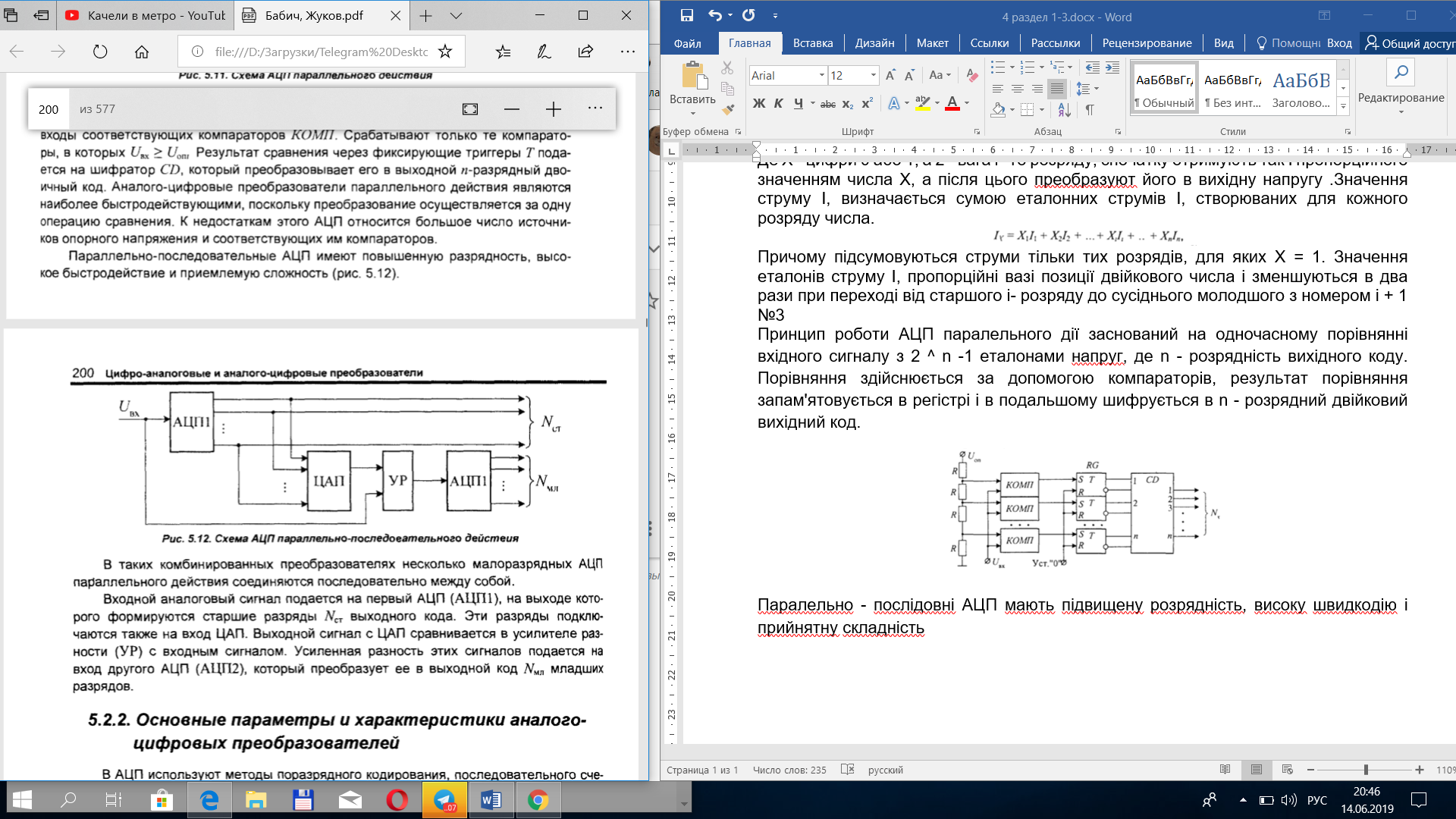

Принцип роботи АЦП паралельного дії заснований на одночасному порівнянні вхідного сигналу з 2 ^ n -1 еталонами напруг, де n - розрядність вихідного коду. Порівняння здійснюється за допомогою компараторів, результат порівняння запам'ятовується в регістрі і в подальшому шифрується в n - розрядний двійковий вихідний код.

Паралельно - послідовні АЦП мають підвищену розрядність, високу швидкодію і прийнятну складність

У таких комбінованих перетворювачах кілька малоразрядних АЦП паралельного дії з'єднуються послідовно між собою.

Перетворювач частоти

Ключовим елементом будь-якого енергозберігаючого електроприводу є перетворювач частоти. Його основне функціональне призначення - перетворення змінного трифазного напруги з мережі живлення з постійною частотою і амплітудою в вихідна напруга необхідної (регульованої) частоти і амплітуди. Регульовані параметри вихідної напруги дозволяють управляти швидкістю обертання валу двигуна, оптимізуючи режим роботи приводу, знижуючи енергоспоживання і зменшуючи ймовірність збоїв і поломок.

Класична схема, по якій конструктивно виконуються більшість перетворювачів частоти, включає проміжну ланку постійного струму і автономний інвертор напруги. Завдяки такому Дволанковий перетворенню вхідного напруги з'являється можливість задавати необхідну швидкість обертання валу двигуна.

Пам'яттю комп'ютера

Пам'яттю комп'ютера називається сукупність різних пристроїв, призначених для прийому, зберігання та видачі двійкової інформації.. За функціональним призначенням пам'ять комп'ютерів поділяється на дві основні групи: зовнішню і внутрішню. Зовнішні ЗП призначені для тривалого зберігання великих масивів інформації з ємністю до гігабайта і більше і малою швидкодією. Зовнішня пам'ять включає в себе накопичувачі на магнітних стрічках, дисках, барабанах та оптичних дисках. Внутрішні ЗП призначені для зберігання програм і даних, що обробляються в поточний момент часу. До внутрішньої пам'яті відносяться: - надоперативні (регістрові) ЗП, які використовують регістри загального призначення процесора; вони володіють невеликою інформаційною ємністю і швидкодією роботи процесора; - кеш-пам’ять, яка призначена для зберігання копій інформації, використовуваної в поточних операціях обміну. Висока швидкодія кешпам’яті підвищує продуктивність комп'ютера; - оперативні, які характеризуються високою швидкодією і інформаційною ємністю до сотень мегабайт; оперативна пам'ять комп'ютерів перших поколінь будувалася на магнітних осердях. В наш час ОП реалізується на напівпровідникових ВІС ЗП. У процесі роботи інформація із зовнішньої пам'яті при необхідності переписується в оперативний ЗП (ОЗП); - постійні, які будуються на напівпровідникових ВІС. У постійну пам'ять інформація записується заздалегідь і її можна тільки зчитувати. Оперативні і постійні ЗП утворюють основну пам'ять комп'ютера; - спеціалізовані види пам'яті - багатопортові, асоціативні, відеопам’ять та ін. За фізичним принципом побудови пам’ять комп’ютера буває: - магнітна (на осердях і плівках, на циліндричних і плоских магнітних доменах); - ультразвукова (магнітострикційна, електрострикційна); - сегнетоелектрична та голографічна (лазерна), на основі надпровідності; - напівпровідникова на ВІС і НВІС, ультра-ВІС. 94 Напівпровідникові ВІС ЗП в свою чергу характеризуються: - технологією виготовлення: на біполярних транзисторах (ТТЛШ, ЕСЛ, И2Л), на МОН-структурах (р-МОН, л-МОН, КМОН); серед новітніх розробок слід відзначити ЗП, в яких використовуються ПТШ на основі арсеніду галію; - способом зберігання інформації - статичні і динамічні (в статичних ЗП елементом пам'яті є тригер, а в динамічних елемент пам'яті будують на конденсаторі і МОН-транзисторах); - енергозалежністю: розрізняють енергозалежніВІС ЗП, в яких при відключенні джерела живлення збережена інформація руйнується (що справедливо в даний час для більшості напівпровідникових мікросхем пам'яті), і енергонезалежні (зазвичай на сегнетоелектриках), в яких інформація зберігається; - структурною організацією ВІС ЗП, символічно подається у вигляді N х т, де N-кількість збережених адресованих одиниць інформації; т - розрядність (організацію у вигляді N х 1 називають однорозрядною, а Nxm– словниково., при цьому т > 1).

Оперативн запам’ятовуючі пристрої динамічного типу

Оперативна пам'ять Оперативний запам'ятовуючий пристрій, або опе¬ративну пам'ять (від англ. НАМ, Каїкіот Ассе$8 Метогу, пам'ять із довільним доступом, що передбачає читання і запис даних у довільні ділянки). Існують два типи мікросхем пам'яті: статична та динамічна. У перших елементарну комірку утворюють тригерні схеми. Будучи встановленою вхідним імпульсом в один із двох можливих станів («О» або «1»), така схема зберігає його до чергового імпульсу або до вимкнення живлення. При прочитуванні записаного в комірку значення її стан також не змінюється. Інакше працює динамічна пам'ять: вона складається з мікроскопічних конденсаторів, кожний з яких може пере¬бувати в стані «заряджений» (що означає двійкову оди¬ницю) або «не заряджений» (двійковий нуль). Щоб збері¬гати дані в такій пам'яті, заряджені конденсатори необхідно періодично підживлювати. Тому динамічний ОЗП за інших однакових умов істотно повільніший від статичного. Проте він менш енергоємний. Обидва види пам'яті зберігають дані лише при постійному електро-живленні, тобто такий запам'ятовуючий пристрій є енер-гозалежним. Дані в цій пам'яті знищуються після ви¬мкнення або перезавантаження комп'ютера.

Динамічні ОЗП характеризуються максимальною інформаційною ємністю і використовуються як основна память в ЕОМ чи в мікропроцесорних системах. Одним із варіантів швидкодіючої ОЗП є память типу FPM, тобто із сторінковим режимом доступу до даних і визначається її структурою.

Структура динамічних ОЗП має свою специфіку і будується на транзисторно-конденсаторних елементах памяті (одно і багато транзисторних).

Пристрої пам'яті, в яких як запам'ятовуючих осередків використовуються паралельні регістри, називаються статичними ОЗП, тому що інформація в них зберігається весь час, поки до мікросхеми підключено живлення.

У мікросхемах статичних ОЗУ присутні дві операції: запис і читання.

Статичні ЗУ можуть бути стійкими, в яких інформація зберігається необмежено довго (наприклад, ЗУ на тригерах, феритових сердечниках), і нестійкими, що володіють властивістю мимовільного стирання інформації (конденсаторні ЗУ, що запам'ятовують електроннопроменеві трубки).

Статичний ЗУ (Static Random Access Memory - SRAM) в якості елемента пам'яті використовується тригер, що, звичайно, складніше, ніж конденсатор з транзисторним ключем динамічного ЗУ. Тому статичні ЗУ володіють меншою щільністю зберігання інформації: Однак тригер з часів перших комп'ютерів був і залишається самим швидкодіючим елементом пам'яті. Тому статична пам'ять дозволяє досягти найбільшої швидкодії, забезпечуючи час доступу в одиниці і навіть десяті частки наносекунд, що й обумовлює її використання в ЕОМ. Головними недоліками статичної пам'яті є її відносно високі вартість і енергоспоживання.

Постійні запам'ятовуючі пристрої

Постійні запам'ятовуючі пристрої, або ROM (Read Only Memory - пам'ять тільки для читання), - це енергонезалежні постійні і полупостоянние пристрої, що запам'ятовують, з яких можна тільки зчитувати інформацію. Вони будуються на основі модулів пам'яті, встановлених на материнській платі. Такі пристрої використовують для зберігання незмінної інформації: програм тестування пристроїв комп'ютера, драйверів базової системи введення / виводу (BIOS) і т.п.

Залежно від технології запису інформації виділяють наступні типи ПЗУ:

■ мікросхеми, програмовані тільки при виготовленні, - класичні (масочний ПЗУ або ROM);

■ мікросхеми, програмовані одноразово в лабораторних умовах, - програмовані ПЗП (ППЗУ) або Programmable ROM (PROM);

■ мікросхеми, програмовані багаторазово, - перепрограмовані ПЗП або Erasable PROM (EPROM); серед них слід відзначити електрично перепрограмовані мікросхеми EEPROM (Electrical Erasable PROM), в тому числі флеш-пам'ять.

Ємність модулів ПЗУ, як правило, не більше 128 Кбайт, швидкодія менше, ніж у ОЗУ. Для підвищення продуктивності вміст ПЗУ копіюється в ОЗУ, і при роботі безпосередньо використовується копія ПЗУ, звана тіньової пам'яттю ПЗУ (Shadow ROM).

У ПК використовуються "полупостоянние" перепрограмовані запам'ятовуючі пристрої - флеш-пам'ять. Модулі або карти флеш-пам'яті встановлюються прямо в роз'єми материнської плати і мають наступні параметри: ємність - до декількох гігабайт (ПЗУ BIOS займає 128 Кбайт), час звернення по зчитуванню - 0,035-0,2 мкс, час запису одного байта - 2-10 мкс.

Багаторазові постійні запам’ятовуючі пристрої

EEPROM (англ. Electrically erasable programmable read-only memory - електрично стирається перепрограмоване ПЗУ, пам'ять якого може стиратися і заповнюватися даними кілька десятків тисяч разів, використовується в твердотілих накопичувачах, однією з різновидів EEPROM є флеш-пам'ять;

На сьогоднішній день класична двухтранзісторного технологія EEPROM практично повністю витіснена флеш-пам'яттю типу NOR. Однак назва EEPROM міцно закріпилося за сегментом пам'яті малої місткості незалежно від технології.

Принцип роботи EEPROM заснований на зміні і реєстрації електричного заряду в ізольованій області (кишені) напівпровідникової структури. [1]

Зміна заряду («запис» і «стирання») проводиться додатком між затвором і витоком великого потенціалу, щоб напруженість електричного поля в тонкому діелектрику між каналом транзистора і кишенею виявилася достатня для виникнення тунельного ефекту. Для посилення ефекту тунелювання електронів в кишеню при записі застосовується невелике прискорення електронів шляхом пропускання струму через канал польового транзистора.

Суматори

для паралельних операндів з паралельним переносом розроб-бота для отримання максимального швидкодії.

Підхід до вирішення цього завдання вимагає пояснень. Справа в тому, що рассмат¬ріваемие суматори - комбінаційні схеми, і що виробляються ними функції можуть бути представлені в нормальних формах, наприклад, у ДНФ, що призводить до двох'ярусної реалізації при наявності парафазних аргументів і до триярусної при однофазних аргументах. Таким чином, граничний швидкодію оцінюється 2-3 елементарними затримками. Однак реальні схеми таких меж не досягають, т. К. Побудова сум¬маторов багаторозрядних слів на основі нормальних форм дало б неприйнятно громіздкі схеми. Реальні схеми мають модульну структуру, т. Е. Складаються з подсхем (розрядних схем), що різко спрощує їх, але не дає гранично можливого швидкодії.

Схема прискореного перенесення - комбінаційна логічна схема, входить в арифметико-логічний пристрій більшості сучасних ЕОМ мікропроцесорів і мікроконтролерів.

Призначена для паралельного формування бітів перенесення при додаванні двійкових чисел в суматорі. Зазвичай будується каскадним способом, складається з декількох схем прискореного перенесення меншою розрядності, зазвичай рівний натуральної ступеня числа 2, але існують і однокаскадні схеми прискореного переносу, що формують сигнали перенесення для всіх бітів слова одночасно.

Перевага цієї схеми - істотне прискорення арифметичних операцій, так як не потрібно час для поширення перенесення послідовно по всіх бітів машинного слова, недолік - підвищена складність.

Арифметико-логічний пристрій (АЛП)—блок процесора, що служить для виконання арифметичних та логічних перетворень над даними, що іменуються операндами. Цей пристрій є фундаментальною частиною будь-якого обчислювача, навіть найпростіші мікроконтролери мають його в складі свого ядра. Центральний процесор та відеопроцесор можуть мати кілька АЛП, що відрізняються своїм функціональним призначенням або типом оброблюваних даних.

За структурою

з розподіленою логікою (з закріпленими мікроопераціями);

з зосередженою логікою (з загальними мікроопераціями).

В першому випадку, апаратура для реалізації обчислень закріплена за регістрами та розділена між ними.

АЛП другого типу також можна класифікувати:

За типом запису даних

-

послідовні;

-

паралельні;

-

послідовно-паралельні.

Мікропроце́сор

інтегральна схема, яка виконує функції центрального процесора (ЦП) або спеціалізованого процесора. Сьогодні слово мікропроцесор є практично повним синонімом слова процесор, оскільки функціональний блок, що на ранніх стадіях розвитку обчислювальної техніки займали цілу плату чи навіть шафу, тепер вміщається в одну невеличку інтегральну схему із сотнями мільйонів транзисторів всередині. З середини 1980-х мікропроцесори витіснили інші види ЦП. Проте загалом це не так: центральні процесорні пристрої деяких суперкомп'ютерів навіть сьогодні є складними комплексами великих (ВІС) і надвеликих (НВІС) інтегральних схем.

Виконання того чи іншого алгоритму можливо при наявності мікропроцесора та пристроїв, в яких зберігається програма. Відомо, що програма — це сукупність команд (правил), що виконуються в послідовності, заданій алгоритмом. Команди вибираються з пам'яті в послідовності, що задається процесором. Процесор визначає адреси елементів пам'яті, в яких зберігаються необхідні данні. Дані передаються в процесор, де перетворюються згідно з командами, і результати операції передаються знову в пам'ять.

Будь-яка мікропроцесорна система працює разом з рядом зовнішніх пристроїв, одержуючи від них необхідну інформацію та передаючи іншу. Для зв'язку з зовнішніми пристроями існує інтерфейс (англ. interface). Цим терміном позначається весь комплекс пристроїв, правил та технічних засобів, що регламентують та забезпечують обмін інформацією між мікропроцесором (включаючи пам'ять) та зовнішніми пристроями. Головними в інтерфейсі є шини, або, як їх ще часто називають, магістралі. Магістраль — це сукупність провідників, для яких строго нормовані логічні рівні «0» та «1». Потужність сигналів на шинах має бути достатньою для живлення необхідної кількості приєднаних до них пристроїв. Для забезпечення цієї потужності використовуються спеціальні мікросхеми — шинні підсилювачі (ШП).

Застосування

а) вимірювання – керування АЦ-перетворювачем; лінеарізація функції перетворювання; автоматичний вибір меж виміру; компенсація перешкод; виключення систематичних похибок;

б) обробка – накопичування масивів вимірювальної інформації; побічне вимірювання; статистична та інші види обробки; стиск даних;

в) керування – приймання керуючих дій оператора; настройка прилада на режим праці; контроль за діями оператора; видача довідкової інформації; сигналізування у екстремальних ситуаціях;

г) відображення – зберігання результатів попередніх вимірювань; відображення текстової інформації; відображення графічної інформації; допоміжна та сервісна інформація (дата, час і т. п.);

д) інтерфейсні функції – керування інтерфейсом; робота в комплексі із іншими ЦВП;

е) тестові функції – самотестування; калібрування вимірювальних каналів.

Мікропроцесорні системи та мікропроцесорні комплекти

Мікропроцесор (МП) – пристрій, який здійснює приймання, оброблення і видачу інформації. Конструктивно МП містить одну або кілька інтегральних схем і виконує дії за програмою, записаною в пам'яті.

Мікропроцесорна система являє собою функціонально закінчений виріб, що складається з одного або декількох пристроїв, головним чином з мікропроцесора і/або мікроконтролера.

Склад мікропроцесорної системи:

- генератор тактових імпульсів, який є одиницею вимірювання тривалості виконання команди. Чим вище частота, тим за інших рівних умов більше швидкодіючої є МПС;

- процесор / мікроконтролер;

- сховище (ОЗУ, ПЗУ) – це невід'ємні частини системи. Інтерфейси введення і виведення – пристрої сполучення МПС з блоками введення і виведення інформації. Всі блоки МПС пов'язані між собою шинами передачі цифрової інформації. В МПС використовують магістральний принцип зв'язку, при якому блоки обмінюються інформацією завдяки єдиній шині даних. Кількість ліній в шині даних зазвичай відповідає розрядності МПС, тобто кількості біт в слові даних;

- пристрої введення-виведення та периферійні пристрої;

- шини. Шина адреси застосовується для вказівки напрямку передачі даних. Шина управління слугує для передачі сигналів, що синхронізують всю роботу МПС.

Головна особливість мікропроцесора – можливість програмування логіки роботи. Тому МПС використовуються для управління процесом вимірювання, обробки дослідних даних, зберігання і виведення результатів вимірювання. Для вимірювальних приладів характерні пристрої введення у вигляді кнопкового пульта і вимірювальних перетворювачів. Пристрої виведення зазвичай представляють цифрові табло, дисплей та зовнішні пристрої сполучення з вимірювальною системою.

Мікропроцесорний комплект (МПК) – сукупність інтегральних схем, сумісних за електричними, інформаційними та конструктивними параметрами і призначених для побудови електронно-обчислювальної апаратури й мікропроцесорних систем керування.

Типовий склад МПК:

- великі інтегровані схеми МП (один чи кілька корпусів інтегральних схем); - великі інтегровані схеми оперативних запам'ятовувальних пристроїв (ОЗП); - великі інтегровані схеми постійних запам'ятовувальних пристроїв (ПЗП); - інтерфейси, або контролери, зовнішніх пристроїв;

- службові великі інтегровані схеми (тактовий генератор, регістри, шинні формувачі, контролери та арбітри шин).

Інтерфейсні схеми, адаптери, контролери

Інтерфейс – це фізичні пристрої, що забезпечують зв'язок між двома іншими пристроями, що дозволяють підключати до комп'ютерів різноманітні периферійні пристрої і їх контролери.

Відповідно до функціонального призначення інтерфейси можна поділити на такі основні класи:

-

системні інтерфейси ЕОМ;

-

периферійно устаткування (загальні й спеціалізовані);

-

програмно-керованих модульних систем і приладів;

-

інтерфейси мереж передачі даних.

До інтерфейсу ПК можна віднести порти, слоти, роз'єми, шини.

Головне завдання інтерфейсу – передача даних і керування цим процесом. Тому найважливішою його характеристикою є пропускна здатність. Продуктивність інтерфейсу виражається в обсязі даних, переданих за одиницю часу. Вона залежить від розрядності, тобто числа одночасно проходячих по кабелю або шлейфу бітів інформації, і робочої частоти, з якою відбувається передача даних.

Адаптер – пристрій, який з'єднує між собою інші пристрої з різними способами подання даних, узгоджуючи ці способи шляхом використання відповідних програмних і технічних засобів. Електричний адаптер – пристрій створений для конвертування напруги й сили електричного струму у потрібну величину. Зокрема, адаптер – об'єкт, який дозволяє з'єднати дві частини обладнання різних типів і розмірів, об'єкт, який дозволяє підключати кілька частин електрообладнання до одного електропостачання, об'єкт, який дозволяє використовувати електричне обладнання в тих країнах, де існує інший тип електропостачання.

Контролер – електронна схема, що управляє зовнішнім пристроєм ПК. Плата контролера дозволяє материнським платам звертатися до спеціалізованих жорстких дисків, а також до сканерів. Проте в даний час більшість жорстких дисків підключається безпосередньо до материнської плати і в картах контролерів не потребує.