- •1.1 Понятие вычислительной системы. Архитектура вычислительной системы. Принцип программного управления. Основные хар-ки эвм. Классификация эвм.

- •1.2 Функциональная организация эвм. Представление данных в эвм. Машинные операции. Методы и способы адресации информации. Форматы команд. Общий алгоритм выполнения команды.

- •1.3 Память вычислительных систем. Принципы действия ячеек памяти (динамические и статические запоминающие устройства), контроллер динамического зу. Энергонезависимая память.

- •1.4. Критерии, методы и способы распределения адресного пространства. Организация основной памяти. Буферные зу. Организация виртуальной памяти.

- •1.5 Кэш память и принцип кэширования. Основные методы построения кэш-памяти. Кэш-контроллер. Основные алгоритмы перезаписи кэша.

- •1.6 Интерфейсы вм и систем и их характеристики. Функции интерфейса. Реализация интерфейсных функций. Организация и назначение шин интерфейсов.

- •1.7 Методы передачи информации. Оценка производительности сопряжения. Примеры стандартных интерфейсов.

- •1.8 Общие технические требования, предъявляемые к конструкции эвм. Типовые конструкции эвм. Анализ методов конструирования.

- •1.10 Основные понятия теории надежности. Количественные характеристики для оценки надежности узлов и блоков.

- •1. 13 Однокристальные микроконтроллеры. Обзор основных архитектур. 8-ми, 16-ти и 32-х разрядные микроконтроллеры ведущих мировых производителей. Критерии, методы и способы выбора микроконтроллера.

- •1.15 Организация интерфейса в мп и мп-системах.

- •1.16 Методы и способы обмена информацией в эвм. Организация передачи данных с использованием систем прерывания и прямого доступа к памяти.

- •1.17 Понятие мультипроцессорной вс. Классификация параллельных вс. Методы построения мп-систем.

- •Классификация по Флинну

- •Классификация по типу строения оперативной памяти

- •1.18 Мультипроцессорные системы на базе разделяемой памяти. Мп системы на базе разделяемой шины. Оценка пропускной способности шины.

- •1. 19 Мп системы на базе перекрестного коммутатора и многовходовой памяти.

- •1.20 Организация многомашинных комплексов.

- •1.21 Конвееpные вс. Понятие конвейеpа, ступени, фиксатоpа. Типичная структура конвейерной вм. (этот вопрос из билетов изъят)

- •1.22 Эвм с нетрадиционной архитектурой. Общие принципы построения. Сравнительные характеристики.

- •1.23 Классификация пу эвм, систем и сетей. Классификация интерфейсов (каналов ввода-вывода) современных вс.

- •1.24 Локальные шины вс. Особенности построения локальных шин (pci, agp). Сигналы локальной шины pci. Особенности реализации и функц-ования agp-порта

- •Спецификация шины pci

- •Основные сведения

- •Конфигурирование

- •Доступ к памяти

- •Очередь запросов

- •1.25 Интерфейсы ide (ata), scsi. Временные диаграммы обмена для ide-интерфейса. Сигналы интерфейсов. Характеристики производительности.

- •1.26 Малые интерфейсы вс. Порт usb. Особенности организации и обмена по шине usb. Структура пакетов для usb-шины.

- •1.27 Накопители на жёстких дисках. Блок схема контроллера нмд. Функции контроллера. Характеристики современных накопителей на мд.

- •1.28 Оптические и магнитооптические диски. Блок-cхема накопителя на од. Характеристики. Области применения.

- •1.29 Дисплеи. Графические контроллеры

- •1.30 Принтеры.

- •1.31 Сканеры, схема, характеристики, области применения

- •1.32 Модемы и факс–модемы, схема, структура пакетов, характеристики, области применения.

- •2.1 Критерии эффективности функционирования вс. Выбор функции обслуживания. Система приоритетного обслуживания. Загрузка системы.

- •2.2 Понятие модели смо. Представления эмм и вс в виде стохастической сети. Характеристики сети. (этот вопрос из билетов изъят)

- •2.3 Понятие глобальной вычислительной сети. Общая структура сети. Базовая сеть передачи данных. Сеть эвм. Терминальная сеть.

- •2.4 Многоуровневая организация управления. Характеристики и назначение каждого уровня управления в сети.

- •2.5 Понятие маршрутизации в сети. Классификация способов маршрутизации. Способы адресации. Протоколы. Сравнительные характеристики современных гвс.

- •2.6 Базы данных. Основные понятия. Типы организации данных. Архитектура систем баз данных. Структура хранения. Модели данных: реляционная , иерархическая, сетевая.

- •Иерархическая модель данных

- •Сетевая модель данных

- •Реляционная модель данных

- •2.7 Система управления базами данных. Сравнительная характеристика современных субд.

- •2.8 Экспертные системы. Назначение. Общие принципы построения. Режимы работы.

Доступ к памяти

DMA (англ. Direct Memory Access) — доступ к памяти, в этом режиме основной памятью считается встроенная видеопамять на карте, текстуры копируются туда перед использованием из системной памяти компьютера. По этому же принципу работают звуковые карты, некоторые контроллеры и т. п.

DME (англ. Direct in Memory Execute) — в этом режиме основная и видеопамять находятся как бы в общем адресном пространстве. Общее пространство эмулируется с помощью таблицы отображения адресов (англ. Graphic Address Remapping Table, GART) блоками по 4 Кб. Таким образом копировать данные из основной памяти в видеопамять уже не требуется, этот процесс называют AGP-текстурированием.

Очередь запросов

Передача данных из основной памяти в видеопамять карты осуществляется в два этапа, сначала передаётся 64-битный адрес, откуда данные нужно считать, затем идут сами данные. Шина AGP предусматривает два варианта передачи,

первый — совместим с шиной PCI — запросы данных и адреса происходят по одному каналу;

второй — в режиме SBA (SideBand Addressing), по отдельной боковой шине, таким образом, можно посылать запросы на новые данные, не дожидаясь получения предыдущих.

На данный момент материнские платы со слотами AGP практически не выпускаются; стандарт AGP был вытеснен более быстрым и универсальнымPCI Express. Последние массовые материнские платы с AGP производились примерно в 04-05 годы для процессора Pentium 4 Prescott и чипсетов поколения Intel 865. Видеокарты стандарта AGP выпускаются в малом количестве и стоят дороже аналогичных PCI-E карт (из-за использования «микросхемы-переходника» PCI-E → AGP).

1.25 Интерфейсы ide (ata), scsi. Временные диаграммы обмена для ide-интерфейса. Сигналы интерфейсов. Характеристики производительности.

Интерфейс ATA (AT Attachment for Disk Drives) — разрабатывался для подключения накопителей на жестких магнитных дисках к компьютерам IBM PC AT с шиной ISA. Интерфейс появился в результате создания устройств со встроенным контроллером — IDE (Integrated Device Electronic). Контроллер жесткого диска был перенесен на плату электроники накопителя с сохранением регистровой модели.

Принятая система команд и регистров, являющаяся частью спецификации ATА, ориентирована на блочный обмен данными с устройствами прямого доступа. Для иных устройств существует спецификация ATAPI, основанная на тех же аппаратных средствах, но позволяющая обмениваться пакетами управляющей информации (PI — Package Interface).

В спецификации АТА фигурируют следующие компоненты:

Хост-адаптер — средства сопряжения интерфейса АТА с системной шиной (набор буферных схем между шинами ISA и АТА).

Кабель-шлейф с двумя или тремя 40-контактными IDC-разъемами. В стандартном кабеле одноименные контакты всех разъемов соединяются вместе.

Ведущее устройство (Master) — ПУ, в спецификации АТА называемое Device-0.

Ведомое устройство (Slave) — ПУ, в спецификации называемое Device-1.

О своих функциях устройства узнают с помощью предварительно установленных конфигурационных джамперов. Если применяется кабельная выборка, то функция устройства определяется его положением на специальном кабеле-шлейфе.

Оба устройства воспринимают команды от хост-адаптера одновременно. Но выходные сигналы на шину АТА имеет право выводить только выбранное устройство. Это значит, что, начав операцию обмена с одним из устройств, хост-адаптер не может переключиться на обслуживание другого до завершения начатой операции. Параллельно могут работать только устройства IDE, подключаемые к разным шинам (каналам) АТА.

Выполняемая операция и направление обмена данными между устройством и хост-адаптером определяются предварительно записанной командой. Важным компонентом устройства является буферная память. Ее наличие позволяет выполнять обмен данными в темпе, предлагаемом хост-адаптером (в пределах возможности устройства).

Адресация в АТА это линейная адресация логических блоков LBA (Logical Block Addressing), где адрес блока (сектора) определяется 28-битным числом.

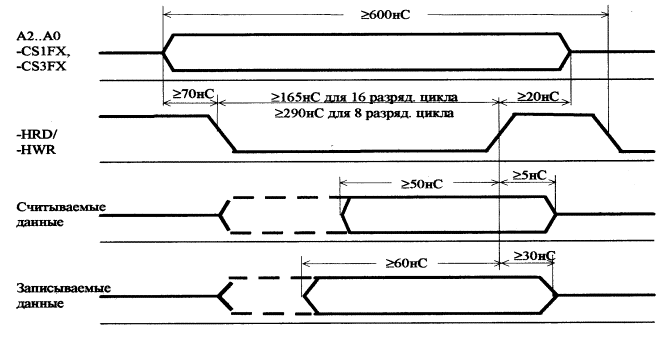

Рисунок 1. Временные диаграммы циклов обмена на шине IDE

Системный интерфейс малых компьютеров SCSI (Small Computer System Interface) предназначен для соединения устройств различных классов: памяти прямого (жесткие диски) и последовательного доступа (стриммеры), CD-ROM, оптических дисков однократной и многократной записи, устройств автоматической смены носителей информации, принтеров, сканеров, коммуникационных устройств и процессоров. Устройством SCSI (SCSI Device) называется как хост-адаптер, связывающий шину SCSI с какой-либо внутренней шиной компьютера, так и контроллер целевого устройства (target controller), с помощью которого устройство подключается к шине SCSI.

Существует три версии SCSI (SE — (single-ended) линейный, LVD — (low-voltage-differential) — интерфейс дифференциальной шины низкого напряжения, HVD — (high-voltage-differential) — интерфейс дифференциальной шины высокого напряжения).

Базовый SCSI (Small Computer System Interface – интерфейс малых компьютерных систем, иногда называемый SCSI-1) – это универсальный интерфейс для подключения различных устройств. В базовом стандарте можно было к одной шине подключить до восьми устройств, включая контроллер. Имеет 8-pазpядную шину данных, максимальная скорость передачи – до 1,5 Мб/с в асинхронном режиме (по методу «запрос-подтверждение»), и до 5 Мб/с в синхронном режиме (метод «несколько запросов – несколько подтверждений»). Может использоваться контроль четности для обнаружения ошибок.

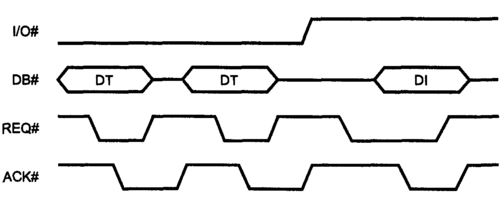

Протокол шины SCSI

В любой момент обмен информацией по шине может происходить только между парой устройств. Операцию начинает инициатор обмена ИУ (initiator), а целевое устройство ЦУ (target) ее исполняет. ИУ выбирает ЦУ по его идентификатору.

Каждый процесс ввода-вывода состоит из следующей последовательности фаз шины: из состояния Bus Free через фазу Arbitration переход к фазе Selection или Reselection. Далее следуют фазы передачи информации (Command, Data, Status, Message). Завершающей фазой является Message In, в которой передается сообщение Disconnect или Command Complete, после чего шина переходит в состояние покоя Bus Free.

Информация по шине данных передается побайтно (пословно) асинхронно, используя механизм запросов (REQuest) и подтверждений (ACKnowledge). Каждый байт контролируется на нечетность (кроме фазы арбитража), но контроль может быть отключен.

В фазе Bus Free шина находится в состоянии покоя — нет никаких процессов обмена; она готова к арбитражу. Признаком является пассивное состояние линий BSY# и SEL#.

В фазе Arbitration устройство может получить право на управление шиной. Дождавшись покоя шины (Bus Free), устройство вводит сигнал BSY# и свой идентификатор SCSI ID. Если идентификаторы выставили несколько устройств одновременно, то право на управление шиной получает устройство с наибольшим адресом, а остальные устройства отключаются до следующего освобождения шины. Устройство, выигравшее арбитраж, вводит сигнал SEL# и переходит в фазу Selection или Reselection.

В фазе Selection ИУ, выигравшее арбитраж, вводит на шину данных результат логической функции ИЛИ от пары идентификаторов — своего и ЦУ, — сопровождая его битом паритета. Установкой сигнала ATN# ИУ указывает, что следующей фазой будет Message OUT. ИУ снимает сигнал BSY#. Отсутствие сигнала I/О# отличает данную фазу от Reselection. Адресованное ЦУ отвечает сигналом BSY#, если паритет корректный и на шине данных присутствует только пара идентификаторов (его и ИУ). На некорректные значения данных устройства отвечать не должны. Если за заданное время ЦУ не ответило, срабатывает тайм-аут, ИУ освобождает шину или вводит сигнал сброса RST#.

Фаза Reselection аналогична предыдущей, но ее вводит ЦУ. Фаза появляется в том случае, когда ЦУ на время исполнения команды отключалось от шины. По завершении внутренней операции это устройство, выиграв арбитраж, будет вызывать ИУ, которое ранее породило исполнение операции. ЦУ снимает сигнал BSY#, активность сигнала I/О# отличает данную фазу от фазы Selection. Адресованное ИУ отвечает сигналом BSY#, условия ответа и тайм-аут аналогичны предыдущей фазе.

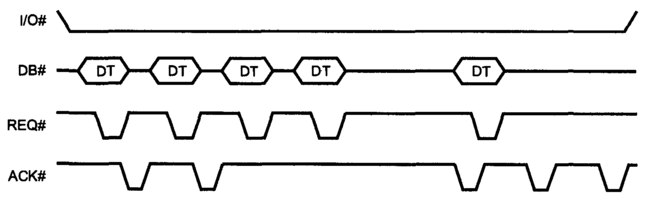

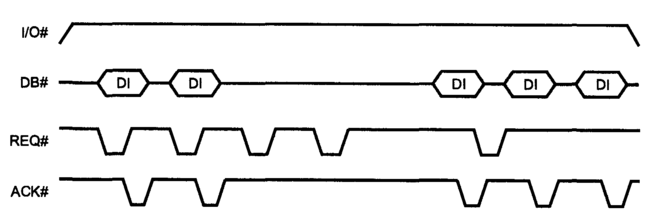

Фазы передачи данных Data OUT и Data IN по предварительной «договоренности» устройств могут выполняться и в синхронном режиме обмена.

При согласовании синхронного режима определяются минимальные длительности и периоды управляющих импульсов АСК# и REQ#, а также допустимое отставание подтверждений от запросов (REQ/ACK offset agreement). ЦУ передает серию данных, сопровождаемых стробами REQ#, в темпе, ограниченном установленными временными параметрами.

ИУ фиксирует принимаемые данные по отрицательному перепаду сигнала REQ#, но отвечать на них сигналом АСК# может с некоторым опозданием. Как только отставание числа принятых сигналов АСК# от числа посланных REQ# достигнет оговоренного предельного значения, ЦУ приостановит обмен до прихода очередного подтверждения АСК#. Операция считается завершенной, когда число принятых подтверждений совпадет с числом посланных запросов. При приеме данных ЦУ механизм согласования остается тем же, но данные фиксируются по отрицательному перепаду сигнала АСК#.

В фазе Command ЦУ запрашивает от ИУ команду. В фазе Status ЦУ делает запрос на передачу ИУ информации о своем состоянии. В фазах Data IN и Data OUT ЦУ делает запросы на передачу данных к ИУ и от него соответственно. Фазы Message Ми Message OUT служат для передачи сообщений. Фазу Message Of/ГЦУ вводит в ответ на условие Attention, порождаемое ИУ сигналом ATN#, когда оно нуждается в посылке сообщения ЦУ. Фазу Message IN ЦУ вводит при необходимости посылки сообщения ИУ.

Между фазами передачи информации сигналы BSY#, SEL#, REQ# и АСК# должны оставаться в неизменном состоянии, меняться могут только значения сигналов C/D#, I/O#, MSG# и шины данных.

Сигналы ATN# и RST# могут порождать условия Attention и Reset соответственно, причем асинхронно по отношению к фазам шины. Эти условия могут привести к изменению предопределенного порядка фаз. Сигнал ATN# вводится ИУ во время любой фазы, кроме арбитража и состояния покоя шины. Сигнал RST# вводится в любой момент любым устройством, и по условию Reset все устройства должны немедленно освободить шину. В зависимости от настройки, принятой для всех устройств конкретной системы, возможно выполнение одного из двух вариантов сброса.

«Жесткий» сброс переводит устройства в состояние, принятое по включению питания, сбрасывая все текущие процессы, очереди и т. п. В случае «мягкого» сброса после освобождения шины устройства пытаются завершить начатые операции, сохраняя текущие значения настроек.